Features

Ultra-high-speed and Ultra-large-scale

The core of the supercomputer, the SPARC64 XIfx processor delivers over 1 teraflops peak performance. Based on the state-of-the-art 20nm semiconductor process technology, 32 compute cores and 2 assistant cores are integrated into a single processor chip. An expansion to the SPARC-V9 instruction set architecture called HPC-ACE2 (High Performance Computing-Arithmetic Computational Extensions 2) features two 256-bit wide SIMD units per core with advanced operation functions, and improves the computational throughput of the processor. HMC (Hybrid Memory Cube) allows a high memory bandwidth of 480GB/s per node and the one-processor-per-node architecture exploits the maximum memory performance. Tofu Interconnect 2 (Tofu2) is integrated into the SPARC64 XIfx processor and enhances node-to-node communication bandwidth to 12.5 GB/s per link with lower latency. Highly scalable Tofu2 enables a system configuration of over 100,000 nodes.

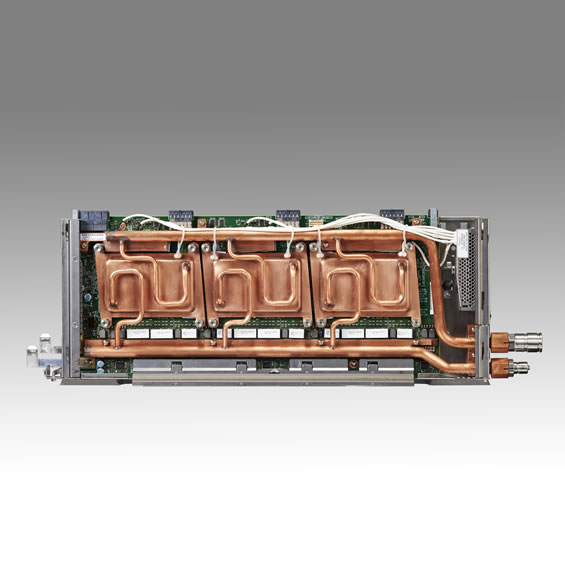

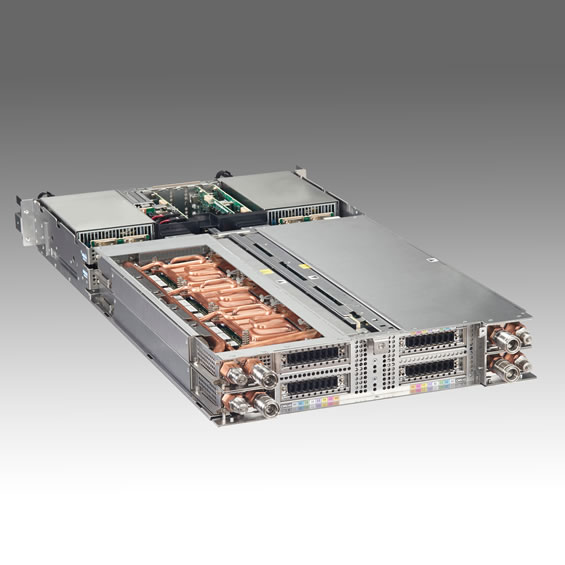

High Density Packaging and Water Cooling

12 nodes are packed into the main unit, a 19-inch 2U form factor chassis. Up to 18 main units can be mounted on a single system rack. Over 90% of the heat is removed by direct water cooling. Lower component temperature achieved by water cooling reduces semiconductor's current leakage, and improves energy efficiency and components' reliability.

Application Performance and Simple Programming Environment

Hybrid parallelization combining MPI and thread parallelization enables efficient memory usage and inter-process communication. However, programming of hybrid parallelized applications require time and effort. VISIMPACT (Virtual Single Processor by Integrated Multi-core Parallel Architecture) is the technology that simplifies hybrid parallelization. Compilers of FUJITSU Software Technical Computing Suite transform MPI programs to hybrid parallel executions automatically. In addition to this, inter-core hardware barrier and shared L2 cache assist efficient execution.

Highly Efficient Job Execution

OS or system software interruptions such as daemons cause system noise which results in application performance loss. The two assistant cores of the SPARC64 XIfx processor handle such system interruptions to remove system noise from compute cores' calculation process. They also handle MPI asynchronous communications to shorten process waiting time. With the help of the assistant cores, PRIMEHPC FX100 realizes highly efficient job execution on large scale systems.

High Reliability and Operability

The SPARC64 XIfx processor employs the same high RAS features proven on Fujitsu's mission critical servers. The flexible 6D Mesh/Torus topology of Tofu2 also contributes to overall reliability and availability. FUJITSU Software Technical Computing Suite provides system management, job scheduling, and highly scalable distributed file system functions that realize high operability on large scale systems.