Archived content

NOTE: this is an archived page and the content is likely to be out of date.

Fujitsu and University of Toronto Develop World's Lowest Power Referenceless CDR for Optical Modules

Contributing to improved processing capability in datacenters through miniaturizing and saving power in optical modules

University of Toronto,Fujitsu Laboratories Ltd.

-

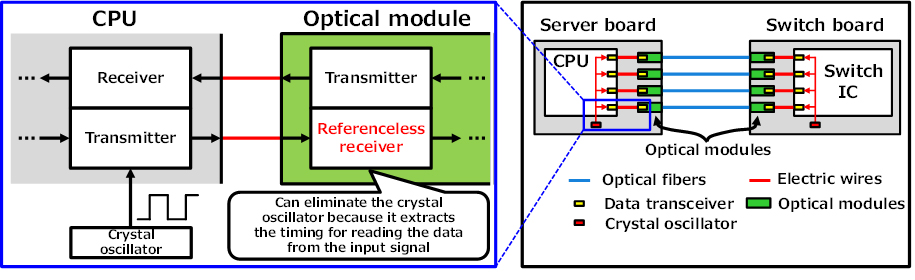

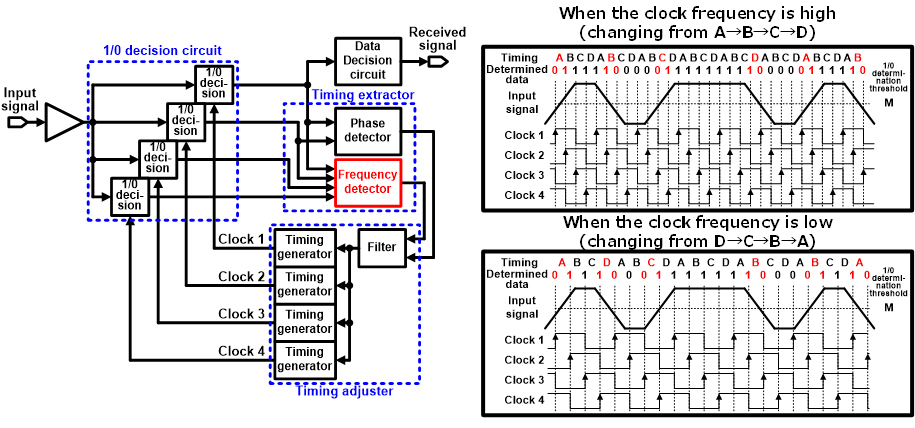

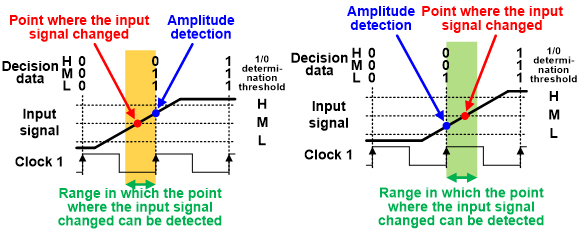

[1] Referenceless CDR

Clock and data recovery circuit. A type of receiver used in data transmission which extracts timing information (clock data) from the received data, without using a high-accuracy reference signal to generate the timing information needed to determine if the received data is a 0 or a 1.

-

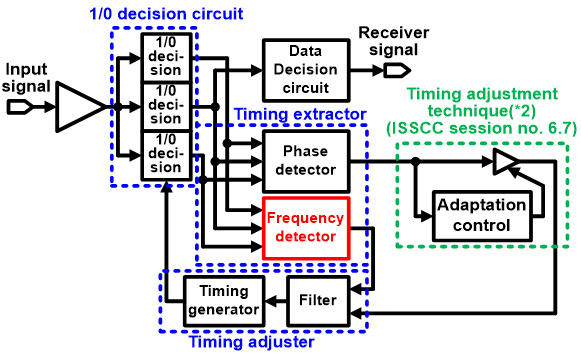

[2] Timing adjustment technology

The University of Toronto and Fujitsu Laboratories have also developed a timing adjustment technology (ISSCC session number 6.7) to improve the reliability of receivers in response to the influence of changes in temperature or noise. This offers highly reliable receivers that are independent from environmental changes.

About The Edward S. Rogers Sr. Department of Electrical & Computer Engineering at the University of Toronto

Founded in 1909, The Edward S. Rogers Sr. Department of Electrical & Computer Engineering (ECE) at the University of Toronto maintains a proud history of innovative education and world-leading research. We are the top-ranked ECE department in Canada and among the best in the world. Our strong emphasis on teaching excellence means both undergraduate and graduate students learn from professors who are international leaders in their fields, in a vibrant and diverse environment. ECE graduates become leaders in every possible field, from mobile to medicine, energy to entertainment. For more on our degree programs, research and events, visit www.ece.utoronto.ca

About Fujitsu

Fujitsu is the leading Japanese information and communication technology (ICT) company, offering a full range of technology products, solutions, and services. Approximately 156,000 Fujitsu people support customers in more than 100 countries. We use our experience and the power of ICT to shape the future of society with our customers. Fujitsu Limited (TSE: 6702) reported consolidated revenues of 4.7 trillion yen (US$41 billion) for the fiscal year ended March 31, 2016. For more information, please see http://www.fujitsu.com.

About Fujitsu Laboratories

Founded in 1968 as a wholly owned subsidiary of Fujitsu Limited, Fujitsu Laboratories Ltd. is one of the premier research centers in the world. With a global network of laboratories in Japan, China, the United States and Europe, the organization conducts a wide range of basic and applied research in the areas of Next-generation Services, Computer Servers, Networks, Electronic Devices and Advanced Materials. For more information, please see: http://www.fujitsu.com/jp/group/labs/en/.

Technical Contacts

Department of Electrical and Computer Engineering Prof. Ali Sheikholeslami

![]() E-mail: ali@ece.utoronto.ca

E-mail: ali@ece.utoronto.ca

Company:University of Toronto

Technical Contacts

Computer Systems Laboratory

![]() E-mail: hsio2017@ml.labs.fujitsu.com

E-mail: hsio2017@ml.labs.fujitsu.com

Company:Fujitsu Laboratories Ltd.

All company or product names mentioned herein are trademarks or registered trademarks of their respective owners. Information provided in this press release is accurate at time of publication and is subject to change without advance notice.

Date: 06 February, 2017

City: Kawasaki, Japan, and Toronto, Canada

Company:

University of Toronto ,Fujitsu Laboratories Ltd.