高性能プロセッサ「SPARC64 XII」、「SPARC64 X+」、「SPARC64 X」

関連製品:SPARC M10-1, M10-4, M10-4S

SPARC M12-1, M12-2, M12-2S

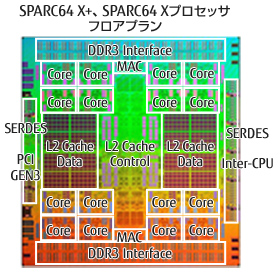

SPARC64™ XII(トゥエルブ)、SPARC64 X+(テンプラス)、SPARC64 X(テン)は、UNIXサーバに必要な高性能、高信頼性を兼ね備えた、富士通が開発するマルチコア・マルチスレッドのプロセッサです。従来の高速性、高信頼性技術を継承しつつ、マイクロアーキテクチャの強化やマルチコア化はもちろん、System on Chipや、Software on Chipなどの機能拡張により性能向上を実現しています。

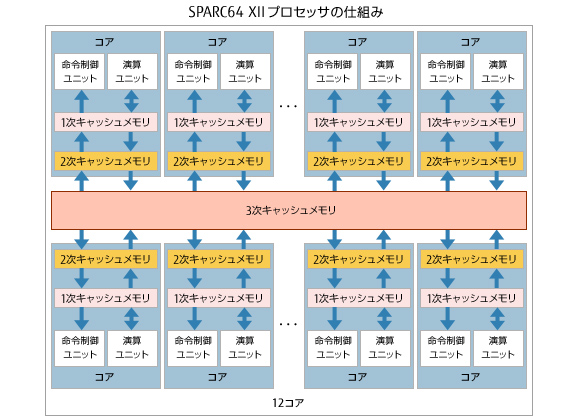

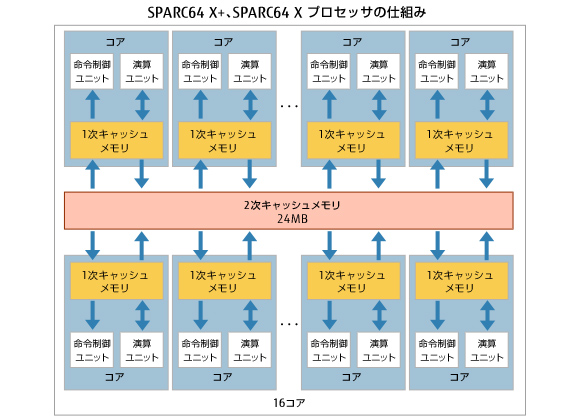

SPARC64プロセッサは、複数のコアを搭載し、マルチスレッドに対応しています。マルチスレッド方式には、SMT(Simultaneous Multithreading)を採用し、効率的にプロセッサを活用することができます。プロセッサ上には、大容量のキャッシュを搭載し、高速処理を実現しています。

| SPARC64 XII | SPARC64 X+ | SPARC64 X | ||

|---|---|---|---|---|

| プロセス | 20nm | 28nm | ||

| 周波数 | 3.2/3.9/4.25GHz | 3.2/3.4/3.7GHz | 2.8/3.0GHz | |

| コア数

(1プロセッサあたり/最大) |

最大12コア | 16コア | ||

| スレッド数

(1プロセッサあたり/最大) |

最大96スレッド

(1コアあたり8スレッド) |

32スレッド

(1コアあたり2スレッド) |

||

| キャッシュメモリ容量

(最大) |

1次 | 128KB、8way構成

(1コアあたり) |

128KB、4way構成

(1コアあたり) |

|

| 2次 | 512KB、16Way構成

(1コアあたり) |

最大24MB、24way構成

(1プロセッサあたり) |

||

| 3次 | 最大32MB

(1プロセッサあたり) |

- | ||

| メモリバンド幅 | 最大 153.6GB/s | 最大 102.4GB/s | ||

| I/Oバンド幅 | 64GB/s | 32GB/s | ||

※各プロセッサの仕様は搭載する本体により異なります。詳細は各モデルの仕様・諸元をご覧ください。

高性能を実現する高速化技術

マルチコア

複数のコアを1つのプロセッサに搭載することで、プロセッサの性能を強化する仕組みです。

SPARC64 XIIでは最大12コア。SPARC64 X+、SPARC64 Xでは、最大16コアを1つのプロセッサ上に搭載しており、性能向上を実現しています。

マルチスレッド

1つのコアで複数のスレッドを同時に処理できる技術です。ソフトウェアからは、各スレッドが複数のコアに見えるため、プロセッサを効率よく利用できます。

高速化を実現する新技術

その他にも、SPARC64プロセッサは従来の高速性、高信頼性技術を継承しつつ、様々な機能拡張を行っています。

- Software on Chip

- System on Chip

- パイプライン処理

- スーパースカラー

- 分岐予測機構

- アウトオブオーダー(Out of Order)実行

- ノンブロッキングキャッシュ制御

- ハードウェア・プリフェッチ機構

- 最大16のアウトスタンディング

- マルチスレッド