Archived content

NOTE: this is an archived page and the content is likely to be out of date.

The New Generation 16-core Processor “SPARC64™ X”

The New Generation 16-core Processor “SPARC64™ X”

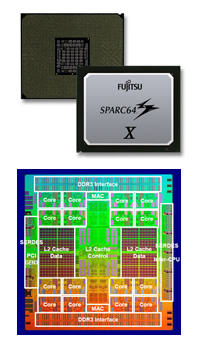

SPARC64 X is the latest 16-core processor developed based on 28 nm semiconductor technology, and will provide extreme performance and high reliability.

Fujitsu through extensive experience in processor development, is further evolving SPARC64 processors used in SPARC Enterprise servers and Supercomputers.

[Facts]

- Frequency: Up to 3.0 GHz

- Multi-processing: 16 cores per CPU chip, 2 threads per core

- Scalability: Up to 64 sockets (2,048 threads)

- Large Cache Memory:

- L1 per core: 64 KB (I) + 64 KB (D)

- L2 per chip: Up to 24 MB

- Innovations:

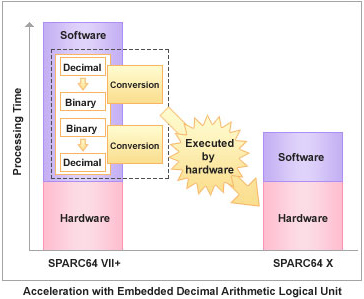

Software on Chip

“Software on Chip” is an innovation implemented in SPARC64 X, and will improve performance dramatically by incorporating software processing into the hardware. This innovation is an excellent example of how Fujitsu and Oracle are collaborating to produce technology for the future. Hardware, OS, Database and Compiler are all engineered together to maximize integrated performance improvement.

[Facts]

- Embedded Decimal Arithmetic Logical Units

- Supports IEEE Standard (IEEE754) and Oracle NUMBER

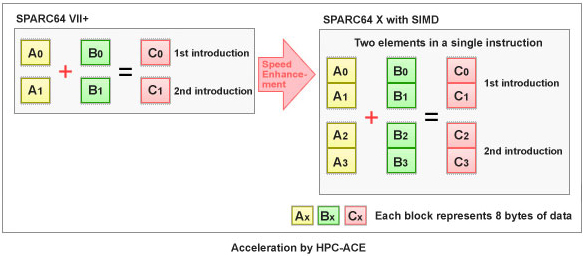

- High Performance Computing Arithmetic Computational Extension (HPC-ACE)

- Methodology that comes directly from supercomputing technology

- SIMD (Single Instruction Multiple Data) to execute multiple instruction simultaneously and improve processing speed

- Designed for bulk data retrieval and compression/decompression

- Embedded Encryption/ Decryption Engines

- Supports cryptographic algorithms : AES, DES, 3DES, RSA, and SHA

System on Chip

“System on Chip” is a methodology that embeds LSIs, including memory controller and I/O controller, into the CPU chip. System on Chip will decrease system latency by physically reducing the distances among LSIs.

This innovation will contribute to improving reliability through reducing the number of parts required.