Poynting for Microwave 解析事例

プリント回路基板のグランド-筐体接続によるESDノイズ対策効果の解析

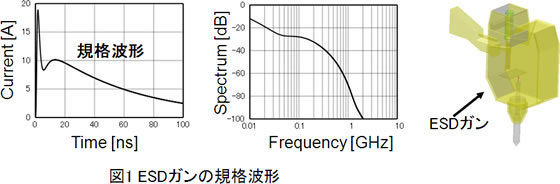

近年の電子システムの設計では、回路の小型化や動作電圧・電流の低下に伴い、電磁ノイズに対する機器耐性の劣化が問題となっています(1, 2, 3)。とりわけ、帯電人体からの静電気放電(ESD)によって生じる電磁ノイズは、図1に示されているようにGHz帯にわたる広帯域な過渡電磁ノイズであるため、電子機器に誤動作などの深刻な機器障害を引き起こすことが知られています。ESDイミュニティ試験要求IEC61000-4-2(4)は、このような人体からのESDを模擬した試験法を制定しています。同試験時の手戻りをなくし、機器の開発期間を短縮するためには、設計の初期段階で適切なESD対策を施しておくことが必要になります。

上記のESDノイズは、半導体デバイスの実装場所、プリント回路基板のパターン、筐体の構造や材質などによって複雑に変化するため(1)、その挙動を定量的に把握するためには、数値シミュレーション技術が必須となります。ESDノイズのような広帯域の過渡現象の解析では、時間領域有限差分法(FDTD法)のようなフルウェーブ解析法がよく使用されています(5, 6)。ESDノイズに対するシミュレーション技術は、近年盛んに研究されるようになってきました。

本事例では、現実の機器設計に現れるような、筐体とプリント回路基板(PCB)からなるシステムをとりあげ、ESDノイズの挙動を解析した事例をご紹介します。このようなシステムレベルの解析では大規模な計算が要求されるため、大規模な並列分散処理が可能なPoynting(7)の特長が存分に発揮されます。

筐体およびプリント回路基板モデル

本解析ではESDノイズ経路の抽出と対策を目的とするため、立ち上がり1nsの電圧源、R=330 OhmおよびC=150pFの3つが直列に接続された簡易ESDガンモデルを採用し、1次放電電流(ノイズピークレベル)をガン波形に合わせた簡易波形を用いることにしています。

実製品の筐体は、一般にさまざまな媒質や形状を持ちます。このうち、ESDノイズ電流の挙動は筐体の金属部に対する影響が大きいと考えられるので、例えば、プラスチック筐体などの場合、メッキなど導電性部分を主要なモデル化の対象としています。金属以外の部品は、必要に応じてモデル化を行います。Poyntingでは筐体の3DCADデータをSTL形式として自動インポートが可能ですので、筐体形状を容易に解析に取り込むことができます。

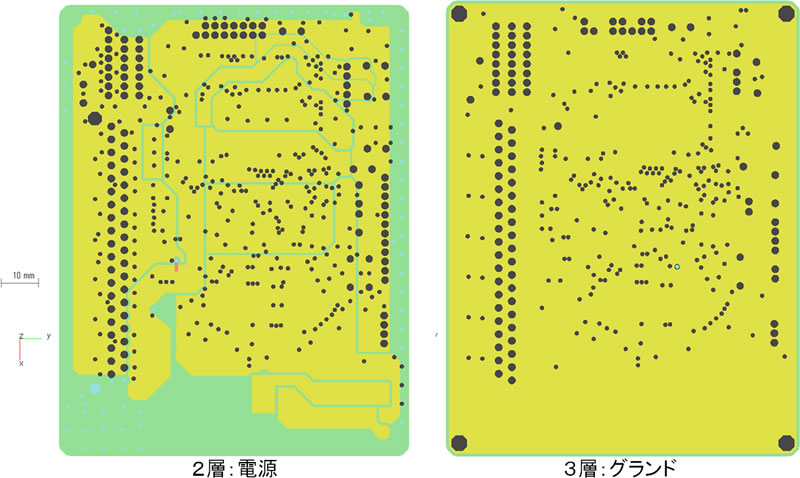

PCBの主要な構成要素は、配線パターンや電源/グランドパターン、回路素子、誘電体基板、コネクターなどの各種部品などが挙げられます。ESD過渡電流の大部分は、局所的にインピーダンスが低いところを選択して流れていくと考えられるので、ESDノイズ経路の抽出では、配線パターンに比較して大きなサイズを有する電源/グランドパターンを考慮することが重要になります。これに対して、本事例では、金属部分の影響をできるだけ正確に考慮するため、すべての配線パターンもモデルに含めることとしました。金属部品以外には、回路素子と誘電体基板がモデル化されています。

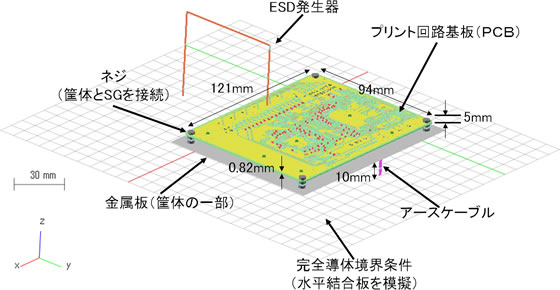

下図は、筐体とPCBからなるシステムとして、Poynting GUIで作成された数値モデルです。ESDガンから接触放電電流は、プリント基板上のコネクター接続箇所付近から注入しています。プリント基板のシグナルグランド(SG)はメッキを想定した金属板(筐体の一部を模擬)とネジで接続され、金属板はアースケーブルを通して、水平結合板を模擬したFDTD解析空間のPEC終端境界に接続されています。

概観

解析モデル

yz面

PCBの電源、グランドパターン

金属板へのグランド接続

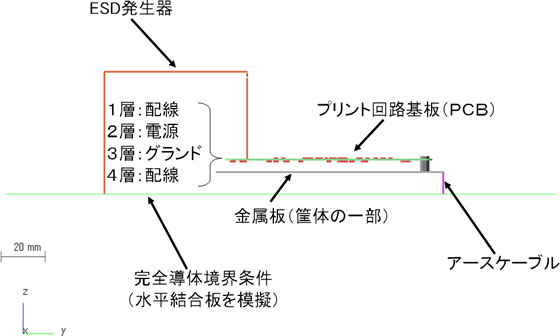

上述したモデルに対して、本事例では、ESD対策としてよく知られている、SGと筐体を接続する2つの方式を比較検討します。下図は、同モデルに対する多点接続および1点接続の様子を表しています。ESD過渡電流はインピーダンスの小さい経路を流れやすいので、多点接続では接続点1および2を通ることが予想されます。一方、1点接続では印加点から接続点4までの距離をESD電流が通過しなければならないため、PCBに大きく影響することが予想されます。

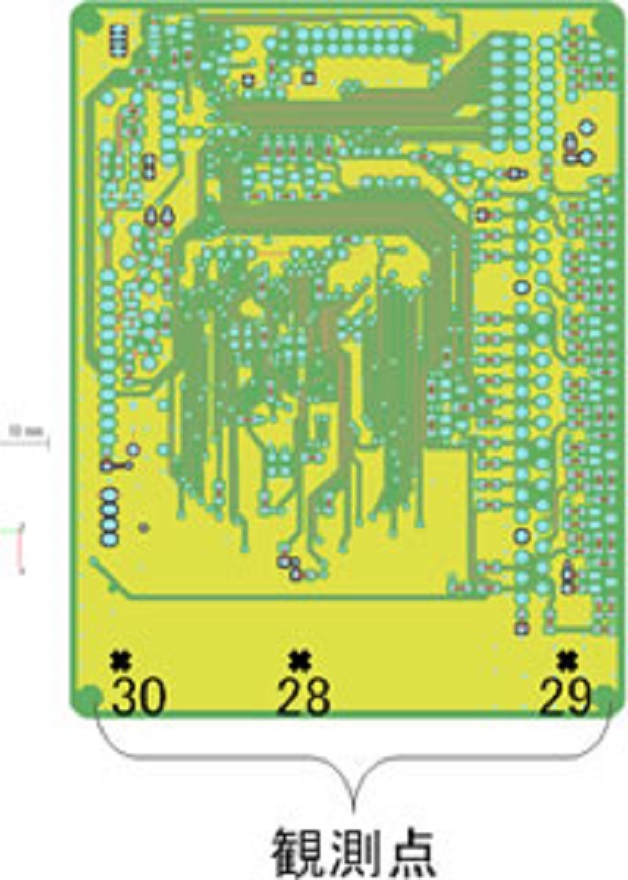

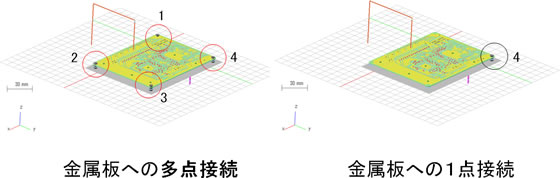

解析結果:電界の時間波形

PoyntingによるESD解析を実施し、多点接続と1点接続に対するノイズの挙動を比較した結果は、以下の通りです。カップリングの影響を詳細に見るために、PCB4層目と筐体の間の点で観測された電界の時間波形が下図に示されています。多点接続のほうが、1点接続よりも3~4倍程度ノイズ電界が小さくなっていることがわかります。これは、ESDノイズ電流がすぐ筐体側へ流れ、GNDパターンを流れる電流値が小さくなったためだと考えられます。

4層目のGNDパターン上の電界

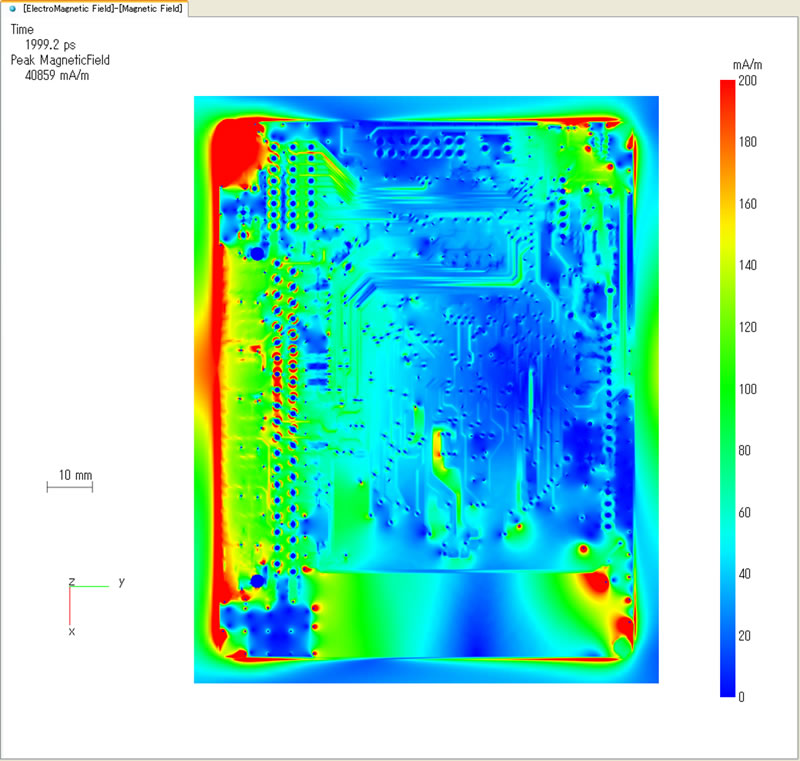

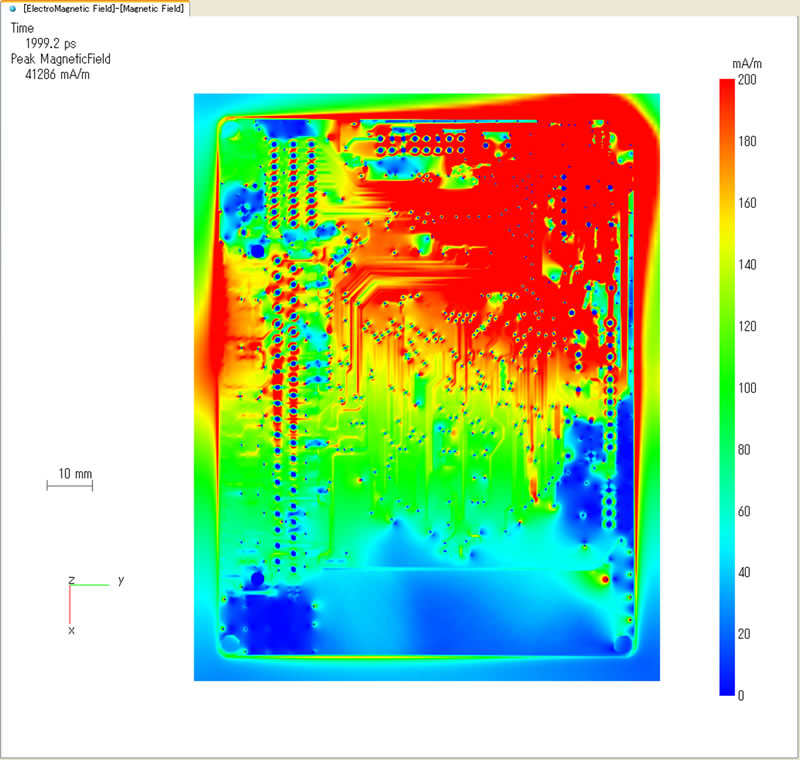

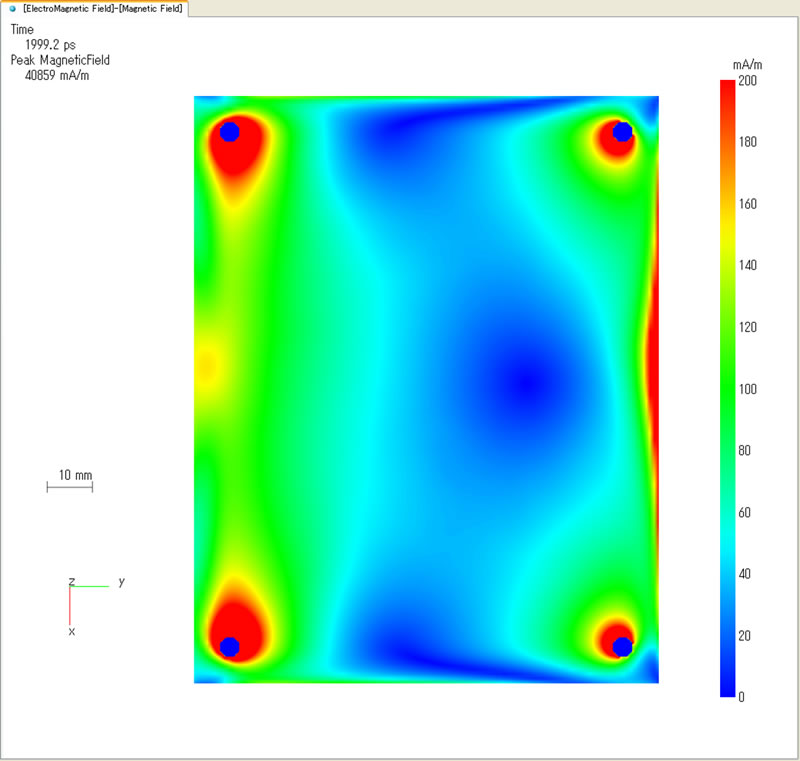

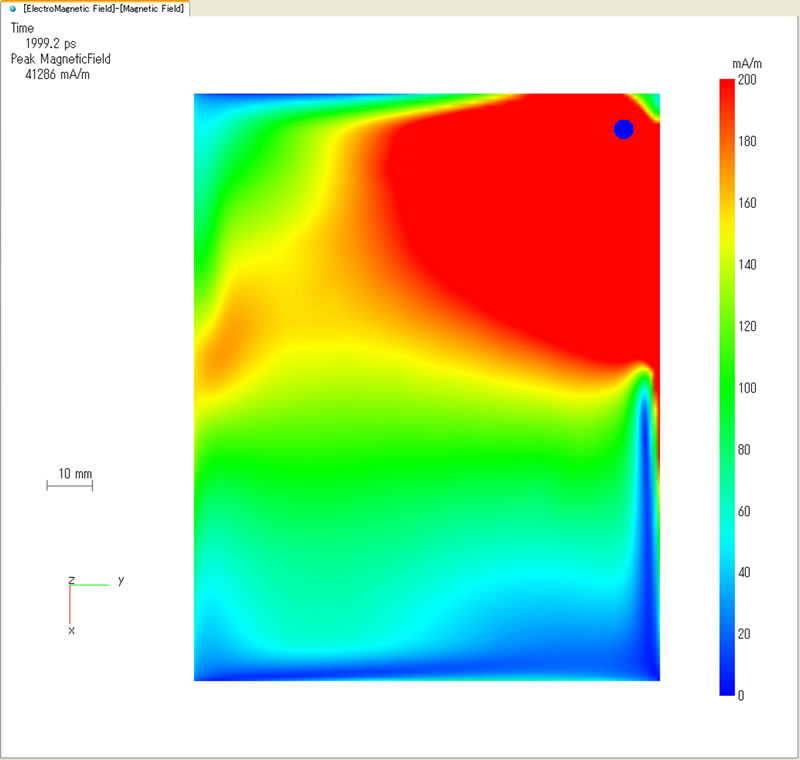

解析結果:3~4層間の磁界分布

T=2.0ns

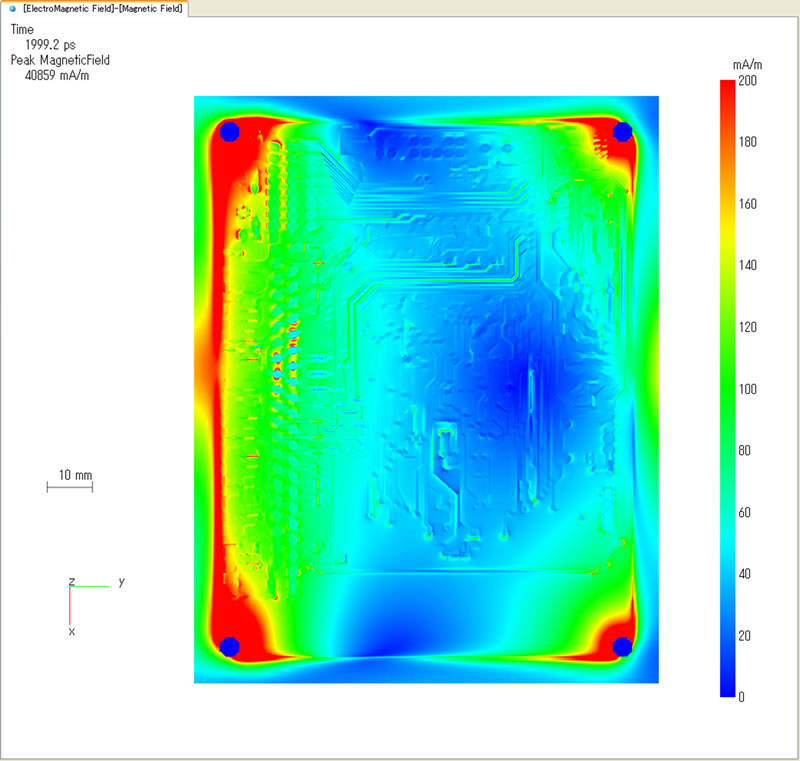

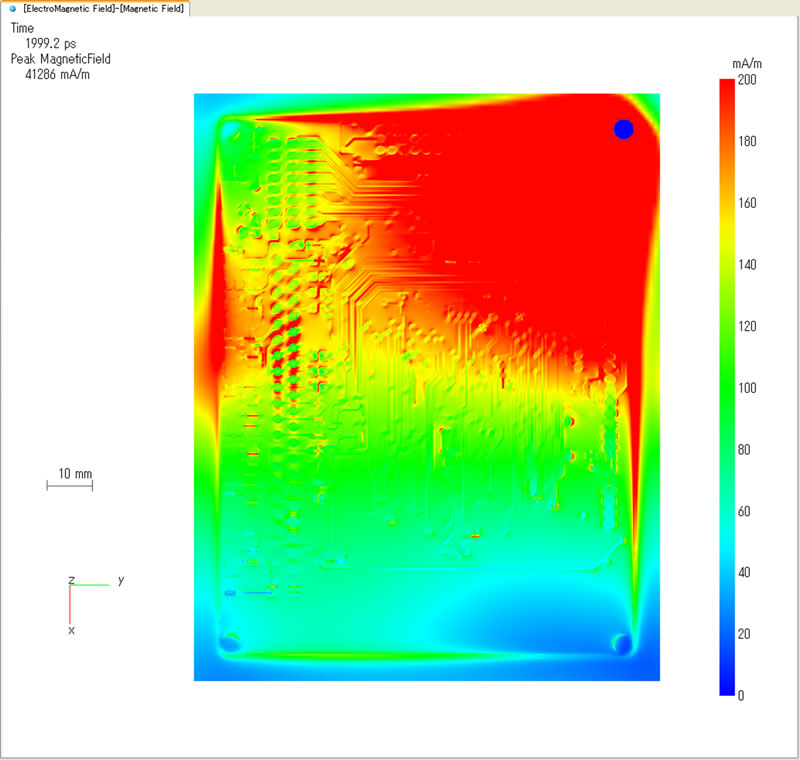

解析結果:4層上の磁界分布

T=2.0ns

解析結果:筐体上の磁界分布

T=2.0ns

解析結果:3~4層間の磁界分布

アニメーション

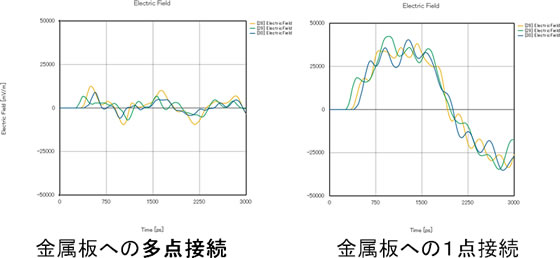

多点接続の場合には、注入されたESD電流が接続点1、2を経由してただちに筐体に逃げているのに対し、一点接続の場合には3、4層が筐体とカップリングし、PCB全体に大きな過渡電流が流れていることが確認できます。

多点接続

1点接続

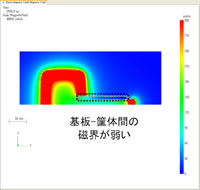

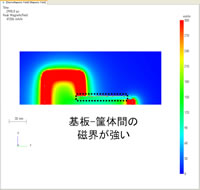

解析結果:yz面の磁界分布

T=3.0ns

まとめ

本事例では、現実的な筐体-PCB一体モデルに対して大規模FDTD計算を行い、筐体-PCB接続方式に対するESDノイズの挙動をシステムレベルで解析しました。筐体-グランド間の接続はESDノイズの挙動に大きな影響を与えることを可視化し、Poyntingの電磁界シミュレーションにより基板表面の電界値が数倍程度変化しうることを確認できました。

多点接続

- ESD発生器からのノイズ電流は、コネクター直近のSG-FG(注)接続しているネジ1,2を通って逃げ、その後、筐体を通ってアースケーブルに達する。

- 筐体と水平結合板のカップリングが大きい、PCBとのカップリングは小さい。

1点接続

- ESDノイズ電流は、PCBの3層、4層と筐体を横断して接続点4のネジに達し、アースケーブルへと流れる。

- 3層、4層パターンおよび筐体が水平結合板とカップリングしている。

コネクター直近の筐体FGへ落とすESD対策の有効性を確認

(注) FG:フレームグランドの略

参考文献

1. 静電気学会編, 「静電気ハンドブック コンパクト版」, オーム社, 2006

2. C. R. Paul, Introduction to Electromagnetic Compatibility, Second Edition, Hoboken, NJ: John&Wiley Sons, 2006.

3. H. W. Ott, Electromagnetic Compatibility Engineering, Hoboken, NJ: John&Wiley Sons, 2009.

4. IEC61000-4-2, Testing and measurement technique ? Electrostatic discharge immunity test, Editio 2.0, 2009.12.

5. O. Fujiwara, et. al., “FDTD Computation of Electromagnetic Fields Due to Electrostatic Discharge Using a Spark Resistance Formula”, J. IEICE B, Vol. J85-B, pp.1644-1651, 2002

6. O. Fujiwara, et. al., “FDTD Simulation of Electrostatic Discharge Current by ESD Testing”, J. IEICE B, Vol. J86-B, pp.2390-2396, 2003

7. 並木武文 他, 「電磁波解析ソフトウェアPoynting」, FUJITSU, 59, no.5, pp.576-582, 2008.