- 富士通「SPARC M12」に見る 開発者のワザと矜持

- SPARC M10 Special. プロセッサを作っている会社にしか作れないミッションクリティカルなマシン、それがSPARC M10

- SPARC M10 Series 1. なぜ、プロセッサの自社開発にこだわり続けるのか

- SPARC M10 Series 2. いま、なぜ、UNIXサーバに懸けるのか

- SPARC M10 Series 3. なぜ、最先端のテクノロジーがデータ伝送に求められるのか

- SPARC M10 Series 4. なぜ、世界最高の液体冷却を実現できたのか

- SPARC M10 Series 5. なぜ、ハードウェアとソフトウェアの強力タッグが必要なのか

- SPARC M10 Series 6. なぜ、品質向上を追求し続けるのか

なぜ、最先端のテクノロジーがデータ伝送に求められるのか

2013年12月6日

プロセッサの性能向上だけでは、システムの高速化は実現できない。プロセッサの速度に見合うインタフェースの性能向上が必須である。SPARC M10の開発では、メインフレームやスーパーコンピュータの開発経験ももつ技術者達が、データ伝送の分野でも大規模なブレークスルーに挑戦している。

小関 由知

さまざまなプラットフォームのプロセッサ実装や、データ伝送技術に携わり、今回高速インターコネクトの開発リーダを務めた小関は、SPARC M10の伝送技術のブレークスルーを語る。

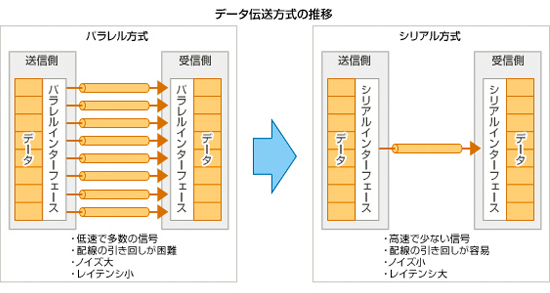

プロセッサの高速化に伴い大量のデータが処理できるようになると、筺体(注1)内や筺体間でいかに大量のデータを伝送できるかがシステムの性能向上につながります。これまでは、複数の信号線(伝送路)を使ってデータを同時並行で送受信できるパラレル方式というデータ伝送方式を採用し、バス幅の増加や動作周波数の向上で高速化に取り組んできました。

一般的には、一本の信号線で順番にデータを送るシリアル方式より、パラレル方式のほうが、より多くのデータを送ることができるといえます。しかし、動作周波数を上げていくと、信号線から生じた電磁波が隣接する信号線に影響を与え、ノイズの発生原因となります。これを解決するには信号線の間隔を大きくする必要がありますが、一方で信号線の増加やそれに伴う配線やボードの設計が難しくなってきていました。

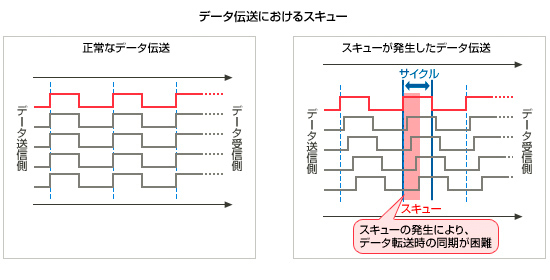

また、パラレル方式では、複数の信号線のサイクルのタイミングを合わせて、データが1か0かを認識する必要があります。しかし、送信側から受信側に到着するまでに、各信号線のサイクルに「スキュー」と呼ばれる時間差が発生してしまい、これらの同期をとることが困難になっていました。この結果、データ伝送に遅延が発生したり、正しくデータが送れなくなったりします。スキューは、配線の長さや形状などのさまざまな条件で変化するのですが、我々の高速化への取り組みの結果によってスキューの影響が高まっていました。

このような状況から、今回、シリアル方式に変更するという決断をしたのです。

シリアル方式は、配線がシンプルであることからノイズが少なく、回路の引き回し(レイアウト)が容易などのメリットがあり、また信号間の同期が不要なことから、高速のデータ伝送の主流となってきています。しかし、シリアル方式は、データの送信側ではシリアル化し、データの受信側ではパラレル化することや、高速にデータを送受信するためのデータの加工処理が必要なことから、パラレル方式に比べてレイテンシが大きくなってしまう課題があります。我々は独自技術を駆使してそれを克服し、低レイテンシの実現やシステムの性能を上げることに成功しました。

また、筐体内や4筐体までを接続する場合には電気ケーブル伝送を、5筐体以上を接続する場合(注2)には光ケーブル伝送を採用するなど、特性の全く異なる伝送路に対しそれぞれに最適な伝送技術を適用しています。ひとつのシステムの中で光と電気のデータ伝送を混在させ、使い分けることができるのは、富士通の最先端技術によるものなのです。この結果、SPARC M10では、筺体内や筺体間を最大14.5Gbpsという世界最速で接続する「高速インターコネクト」を実現できました。

さらに、SPARC M10はミッションクリティカル分野でお使いいただくことから、高速化に加えて信頼性も重視して開発に取り組みました。

城田 慎一郎

今回、データの送信側回路の開発を担当した城田は、データ伝送の高速化の取り組みについて語る。

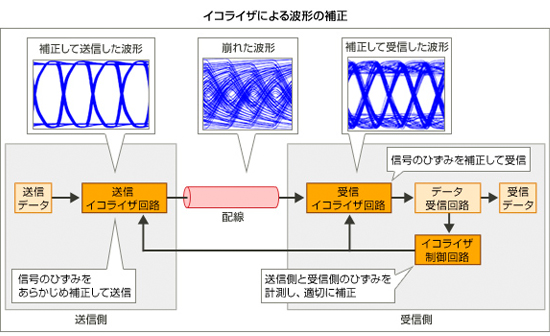

データの送信側から送った信号は、データ伝送が高速なほど、また、伝送距離が長いほどひずみが大きくなります。それは、信号を配線上の波形でみると、崩れた形となって確認できます。ひずみが大きくなると、データを判定することが難しくなり、データを正しく伝送できなくなるという問題が発生します。

これに対し、私達は送信側と受信側の両方にイコライザという補正回路を搭載し、崩れた波形を自動で補正しています。SPARC M10のイコライザはさまざまな条件に対応できるよう設計されており、ボード内、筐体内、筐体間のそれぞれのデータ伝送に適用できます。さらに、イコライザ制御回路により、送信側と受信側のひずみを計測し、イコライザでの補正をより適切なものにしています。

このような取組みの結果、最大64CPU/1024コアの大規模構成でありながら、サーバに実装されるデータ伝送としては世界最速のスピードを達成することができました。

高速化の取り組みは、これだけではありません。受信側のパラレルデータを通常のおよそ4倍の高周波数で処理したり、受信側でもつ3種類のバッファ(周波数偏差吸収、非同期クロック乗り換え、レーン間スキュー調整)を一つのバッファに統合して処理するなどの工夫をこらし、レイテンシを我々が従来もつ技術の1/3に低減することができました。そして、富士通の前世代のUNIXサーバのおよそ9倍のシステムスループットを実現しています。

当社はこのような先進的な技術を、半導体技術の国際会議「ISSCC(IEEE International Solid State Circuits Conference)」でも発表し、常に業界をリードしています。

酒林 聰太

データの受信側回路の開発と評価を担当した酒林は、最先端のデータ伝送技術を学ぶために、株式会社富士通研究所の米国拠点(Fujitsu Laboratories of America, Inc.)に派遣されていた。

システム全体の品質を高めるためには、データの伝送路には非常に高い信頼性や部品寿命が求められます。

SPARC M10は、データの送受信における伝送エラーレートにおいて富士通独自の厳しい目標を設定し、データ化けを起さない取リ組みを行っています。

システムにおけるデータの送受信は、プロセッサ間およびプロセッサとクロスバーチップ間の基板接続、筐体内の電気ケーブル接続、筐体間の電気ケーブルや光ケーブル接続など、方式やデバイスにさまざまな違いがあります。さらに、各デバイスの製造時のばらつきや、温度変化など、複合的な条件を受けて、データ化けを起す可能性を含んでいます。

私達は、データ伝送時に、数多くのパラメタを用意して自動調整し、それぞれの条件に合った最適な伝送環境を作りだしています。これらのパラメタの調整は、富士通独自の技術により実現しています。

私が派遣されていた富士通研究所の米国拠点は、パラメタの調整をはじめ世界で最先端の伝送技術を研究しており、私は3年半ほどそちらに赴任しました。そして、そこで得た技術をSPARC M10に注ぎ込んだのです。

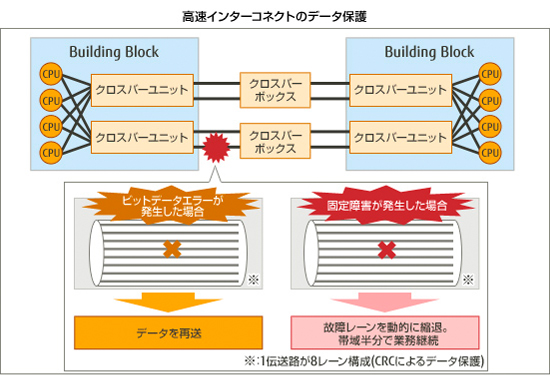

また、仮にエラーが起きたとしても、業務を続けられる仕組みも組み込んでいます。

高速インターコネクトは、CRC(注3)というチェック機能を備えており、ビットデータエラー検出されると、ハードウェアがデータを再送します。その際、故障などによりデータ再送でもリカバリができない場合は、該当レーンを動的に縮退し、業務を継続できます。

このような回路設計に加え、光ケーブルなどの部品の品質にも配慮しました。部品は富士通だけで製造できるものではないため、製造ベンダと協力しながら部品の特性分析、カスタマイズ、長時間に渡る負荷試験なども行い、品質向上に取り組みました。

株式会社富士通ITプロダクツ

さらに、伝送を含めたシステム全体としての品質を確保するため、製造拠点である株式会社富士通ITプロダクツに2ケ月半常駐して量産工程での品質強化を行いました。このようにMade in Japanの高い品質を確保したSPARC M10だからこそ、世界中のお客様のビジネスに貢献できると確信しています。

ビッグデータ時代の今日、基幹システムで処理されてきたビジネスデータと、多種多様で大容量なビッグデータを同時に分析し、より効果的な経営判断を行うことが重要である。それを実現するプラットフォームには、リアルタイムな処理性能と柔軟な拡張性が求められる。

SPARC M10は、自社開発のプロセッサで高速に処理されたデータを、世界最先端の高速インターコネクトでスピーディに伝送し、これまでにない柔軟な拡張性とリニアな性能向上を可能にしている。

そして、ロードマップの"25Gbps"の文字が示すように、富士通の伝送技術はますます進化を続けていく。

|

エンタプライズサーバ事業本部

テクノロジ開発統括部 マネージャー 小関 由知 |

|

エンタプライズサーバ事業本部

テクノロジ開発統括部 城田 慎一郎 |

|

エンタプライズサーバ事業本部

テクノロジ開発統括部 酒林 聰太 |

(注1)Building Block

(注2)クロスバーボックスによる接続

(注3)Cyclic Redundancy Check(巡回冗長検査)の略。ディスク・テープの読み出し、書き込みなど主にシリアルインターフェースのアクセスにおけるエラーをチェックする機能。

[関連プレスリリース]

![]()