- 富士通「SPARC M12」に見る 開発者のワザと矜持

- SPARC M10 Special. プロセッサを作っている会社にしか作れないミッションクリティカルなマシン、それがSPARC M10

- SPARC M10 Series 1. なぜ、プロセッサの自社開発にこだわり続けるのか

- SPARC M10 Series 2. いま、なぜ、UNIXサーバに懸けるのか

- SPARC M10 Series 3. なぜ、最先端のテクノロジーがデータ伝送に求められるのか

- SPARC M10 Series 4. なぜ、世界最高の液体冷却を実現できたのか

- SPARC M10 Series 5. なぜ、ハードウェアとソフトウェアの強力タッグが必要なのか

- SPARC M10 Series 6. なぜ、品質向上を追求し続けるのか

いま、なぜ、UNIXサーバに懸けるのか

2013年10月1日

システムのプラットフォームがコモディティ化される中、各ベンダの威信をかけた差異化機能が搭載されているUNIXサーバは、お客様のビジネスの競争力に付加価値をもたらす。

プロセッサからサーバ本体装置まで、一貫した設計・開発を可能にしている富士通。その開発者達は、メインフレーム、スーパーコンピュータ、そしてUNIXサーバと、世界最先端のテクノロジーを継承しつつ、さらなるチャレンジをいとわない。

海野 秀之

メインフレームやUNIXサーバのプロセッサ回路設計を経て、今回システム全体の開発主幹を努めた海野は、SPARC M10が目指した革新性を語る。

最新UNIXサーバ SPARC M10は、基幹システムの安定運用を実現し、さらに、ビッグデータ活用をはじめとした今後のビジネス変革に柔軟に対応できるプラットフォームを目指して開発しました。従来から互換性を非常に重視していることもあり、UNIXサーバというと「古い」というイメージを持たれているかもしれませんが、今回の開発では、作り変えなかった部分はほとんど無いというくらい最新の設計とテクノロジーを投入し、性能や機能を強化しています。

SPARC M10の開発において、特に重視したポイントは3つあります。

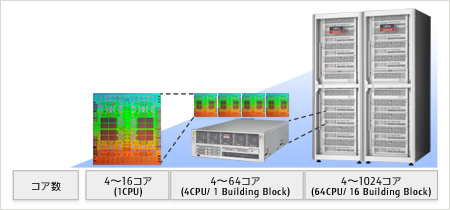

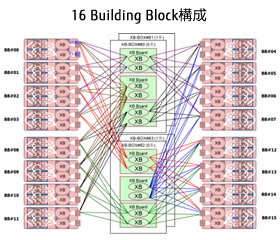

1つめは、高いスケーラビリティです。新たにBuilding Block方式を採用し、16コアを搭載した1CPUサーバから、最大16Building Block(筐体)・64CPU・1,024コアまでの高い拡張性を可能にしています。加えて、CPUコア アクティベーションによりコア単位での段階的なリソース追加を実現しており、お客様の業務計画やシステムの負荷の状況にあわせて、柔軟に拡張していただけます。

2つめは富士通のDNAともいえる、信頼性です。サーバシステムの高い信頼性、可用性を実現するためには、回路設計の段階で徹底的なデータ冗長・リカバリー機構をつくり込んだ上で、万が一の故障の際にも故障の影響を限定し、動的縮退や活性交換によって業務継続を実現するため、システム全体の制御が必要です。これには、LSIの回路設計だけでなく、OS、システム監視機構(XSCF)を含めたシステムトータルとしての挙動、さらには保守手順までを含んだシステム設計が必要とされます。SPARC M10は、富士通がメインフレーム時代からこの分野で培ってきた技術、ノウハウを継承し、業界最高水準の信頼性を実現したサーバです。

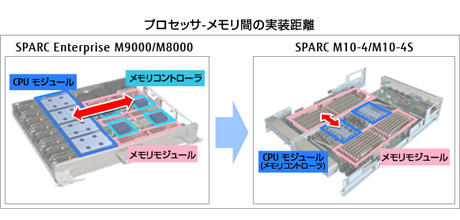

3つめは、高密度実装です。SPARC M10では、Building Block方式による拡張性を実現する一方で、筐体の高密度化、省スペース化にも挑戦しています。CPU内にメモリコントローラを内蔵し、さらに、CPUとメモリ間、CPU間を物理的に近く配置することで、より高いシステム性能を実現することができます。一方で、このように密度を上げることで、冷却はより困難になります。そこで、新たな冷却技術「Liquid Loop Cooling」を独自に開発し、さらに、冷却システム設計者、筐体構造設計者、そしてプリント板設計者が協力し、検討を重ねることで、高性能をコンパクトな筐体に凝縮しました。

プロセッサ、サーバ本体装置、OS、ファームウェアの開発者達が一丸となり、大きなブレークスルーに挑んだその結晶がSPARC M10です。

福村 祐美

スーパーコンピュータやUNIXサーバのプロセッサ開発を経験し、SPARC M10のシステム仕様を担当する福村は、お客様の声を反映した高い拡張性と柔軟性について語る。

新製品の開発では、機能や性能を強化するために、システムの設計を従来のものから変更することがあります。しかし、その変更によって、お客様にとって重要な価値が損なわれるようではいけません。そこで、SPARC M10の開発にあたっては、営業、SE、保守などの社内の各部門からお客様の声を吸い上げ、システム設計に反映しています。

たとえば、SPARC M10では1CPUに16コアを実装しましたが、利用単位を16コアにしてしまうと、従来小さな構成で利用されていたお客様にとっては、ソフトウェアライセンスのコスト増大などを招いてしまいます。このように作り手の都合をお客様に押しつけるのではなく、何とかメリットを享受していただけないだろうかと考えた結果、「CPUコア アクティベーション」という仕組みが生まれました。

CPUコア アクティベーションにより、最初は開発機として小規模構成で導入していただき、その後必要に応じて徐々にリソースを購入、追加していただくことも可能となっています。

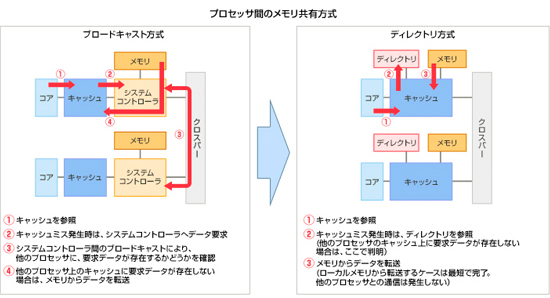

また、SPARC M10ではプロセッサ間のメモリ共有にかかわる制御方式を大幅に変更しました。従来機では、プロセッサ間で同じメモリが参照できるという共有メモリの実現のために、メモリアクセスをシステム全体にブロードキャストする方式を採用してきました。この方式では、ブロードキャスト性能がシステム全体の性能を決めるため、この部分の制御を洗練させ、また、チップ分割や伝送の高速化などの工夫を重ねることで、性能向上してきたわけです。しかし、さらに大幅な性能向上を実現するためには、ブロードキャストがボトルネックになるような方式から、新しい方式に切り替える必要がありました。

そこで、我々は、長年磨き続けてきたブロードキャスト方式からディレクトリ方式へ、プロセッサ間のメモリ共有方式を大きく変更したのです。ディレクトリ方式とは、メモリ上の各領域について、複数ノード間でメモリの使用情報が共有されているのか等の情報を「ディレクトリ」と呼ばれる領域に格納、管理することでキャッシュの一貫性を制御する方式です。これにより、メモリ共有のためにすべてのアクセスをブロードキャストする必要はなくなり、より大きな構成までシステムをスケールさせることが可能となりました。それに加えて、プロセッサに直結されたローカルメモリは、非常に高速にアクセスできるようにもなっています。

一方で、ディレクトリ方式に変えたことによる影響が生じないための工夫も行っています。たとえば、ローカルメモリがより高速にアクセスできるようになったことで、プログラムを実行するプロセッサと、そのプログラムが利用するメモリがなるべく近くなるようにリソース配置することが重要となるのですが、このようなスケジューリングはOSが自動的に行うため、ユーザが意識する必要はありません。また、4筐体を超えるシステム構成において、筺体間接続をスター型にしたのも、同様の理由からです。これにより、ノード間の転送速度の違いを抑えるとともに、システム全体を止めることなくBuilding Blockを交換できるような、保守性も確保しています。

このように、SPARC M10は、性能向上や機能追加のためのチャレンジの一方で、これまで培ってきた価値を着実に継承した、お客様に安心して使い続けていただけるシステムとなっています。

水澤 芳樹

UNIXサーバのシステムRASの仕様に携わり、現在は開発全体を推進している水澤は、富士通でしか成しえないSPARC M10の信頼性について語る。

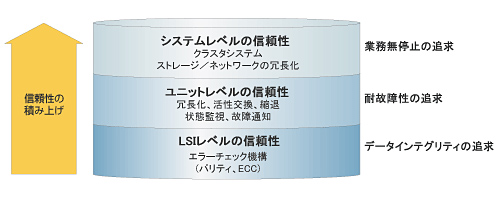

富士通のUNIXサーバは、お客様企業の基幹業務にお使いいただくため、24時間365日の安定稼働が求められます。そのため、SPARC M10には富士通がメインフレーム時代から培ってきた、高信頼システムを実現するための技術、ノウハウがつぎこまれています。これは、ひとくちに「メインフレームクラスのRAS」と表現されることもありますが、LSIレベル、ユニットレベル、システムレベルから成り立っており、それぞれのレベルで信頼性を積み上げることでシステム全体の可用性を向上することを示しています。

まず、LSIレベルで、きめ細かいエラーチェックやリカバリ機能を備えた回路設計を行っています。SPARC M10システムでは、あらゆるデータ経路、レジスタやメモリなどの記憶領域が冗長コードにより保護されています。さらには、演算結果についてもパリティ予測やレジデューによる保護がなされています。このような徹底的なデータ保護と、多数のエラーチェッカによるきめ細かいエラー検出、リカバリ処理、および、縮退機能は富士通ハードウェアの特色といえます。

次に、ディスク・電源・ファン等のユニットレベルで、冗長化、活性交換、縮退に対応することで、万が一の故障に対しても業務の継続を可能にしています。

そして、ハードウェア、ファームウェア、OSおよびクラスタなどのミドルウェアを統合したシステムレベルで高信頼化を実現しています。大規模で複雑な計算システムにおいては、障害が発生しないことが、もちろん望ましいのです。発生してしまった場合には、原因を素早く特定し回復することが大変重要となります。SPARC M10は、エラー発生時のOSやミドルウエアを含めたシステム全体の挙動が設計、検証されています。このため、万が一の障害発生時には、縮退動作により業務を継続する一方で、問題発生個所を正確に特定し、対処することが可能となっています。

このようなことが実現できるのは、ハードウエア、ファームウエア、OSの設計者、さらには、品質保証部門が一丸となって開発していることが大きいと思います。SPARC M10は、この富士通の強みを生かし、それぞれが蓄えてきた技術、ノウハウを結集して作り上げたサーバです。

河野 香代子

メインフレームの開発を経て、UNIXサーバのプリント板の開発を率いる河野は、64コアをわずか4Uに凝縮するという高密度実装への険しい道のりを振り返る。

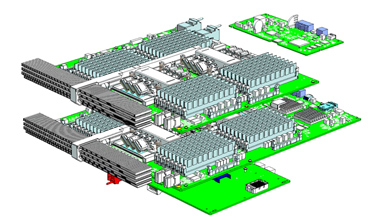

今回の開発では、高密度実装が大きな挑戦のひとつでした。SPARC M10-4/M10-4Sは、4つのCPU(合計64コア)と64枚のメモリを、4U筐体に収容しています。このため、2つのCPUと32枚のメモリを搭載したシステムボードを2枚、上下に重ねるというユニークな実装構造を採用しました。筺体内部をご覧いただければ、立体的な構造により、非常に高密度な実装になっていることが、おわかりいただけると思います。

また高密度実装は、設置面積削減の効果だけでなく、実は、システム性能の向上にも重要な役割を果たしています。

SPARC M10では、ファンによる空気冷却と筺体内で循環させる液体冷却を組み合わせたハイブリッド冷却「Liquid Loop Cooling」を富士通が独自に開発しました。

これによって、プロセッサ上部に大きなヒートシンクを取り付ける必要がなくなり、また、冷媒によって熱を遠くまで輸送し冷やすことができるため、プロセッサをファンのすぐ近くに置く必要がなくなるなど、レイアウトの自由度が増します。その結果、プロセッサとメモリを近くに配置することが可能となりました。

SPARC64 Xプロセッサは、メモリコントローラを内蔵し、16枚のメモリをバッファチップなどを介さずに直接接続することで高バンド・低レイテンシなメモリアクセスを実現しています。そして、その高性能を支えているのが、富士通独自の冷却技術と高密度実装技術なのです。

実際には、プロセッサに16枚のメモリ(DDR3 1600)を高速インタフェースで直結するのは、伝送条件上非常に厳しく、伝送の立場からは、1mmでもメモリとCPUの間隔を狭めたい。反対に、冷却の立場からは、風の流量を確保するためにも、少しでも部品の間隔を広くしたい。さらに、Liquid Loop Coolingのためのパイプを通す場所なども確保する必要があります。筐体の内部構造を成立させるためには、柱をたてる位置やネジの位置を、プリント板設計にも反映する必要があります。こういった互いに絡み合う条件を、設計者同士が活発に議論し、検討をかさねることで到達したのが、現在の姿です。この形になるまでには、実に10パターンを超える案を議論しました。

結果として、より高性能を、よりコンパクトな筐体に収めることができたと思います。1筐体を4Uサイズに収めることで、最大構成である16Building Blockを2つの標準ラックに収容することが可能です。

また、筺体のサイズももちろんのこと、「標準ラックに搭載できる」という要件が非常に重要であり、冷却風の流れる方向や、ラックに搭載したままでのファン、ハードディスク、PCIカード等の保守など、運用性を確保しています。

お客様のビジネスをさらに優位なものにするため、UNIXサーバの革新は今後も続いていく。

|

エンタプライズサーバ事業本部

基幹サーバ事業部 第二ES開発部 マネージャー 海野 秀之 |

|

エンタプライズサーバ事業本部

基幹サーバ事業部 第二ES開発部 福村 祐美 |

|

エンタプライズサーバ事業本部

基幹サーバ事業部 第三ES開発部 水澤 芳樹 |

|

エンタプライズサーバ事業本部

基幹サーバ事業部 第三ES開発部 河野 香代子 |

![]()