- 富士通「SPARC M12」に見る 開発者のワザと矜持

- SPARC M10 Special. プロセッサを作っている会社にしか作れないミッションクリティカルなマシン、それがSPARC M10

- SPARC M10 Series 1. なぜ、プロセッサの自社開発にこだわり続けるのか

- SPARC M10 Series 2. いま、なぜ、UNIXサーバに懸けるのか

- SPARC M10 Series 3. なぜ、最先端のテクノロジーがデータ伝送に求められるのか

- SPARC M10 Series 4. なぜ、世界最高の液体冷却を実現できたのか

- SPARC M10 Series 5. なぜ、ハードウェアとソフトウェアの強力タッグが必要なのか

- SPARC M10 Series 6. なぜ、品質向上を追求し続けるのか

なぜ、プロセッサの自社開発にこだわり続けるのか

2013年7月4日

富士通のプロセッサ開発の歴史はまもなく60年を迎える。

今や、全世界でサーバのプロセッサを開発できるベンダの数はわずか数社。米国勢が大半を占めるこの業界にあって、富士通のプロセッサ開発は脈々と引き継がれ、そして今も進化を続けている。

清田 直宏(1次キャッシュ担当)

入社以来、プロセッサの開発に取り組んでいる清田は、富士通のプロセッサ開発を語る。

富士通では、メインフレーム、UNIXサーバ、スーパーコンピュータという垣根を作らずに、一つのチームが一丸となってそれぞれのサーバのプロセッサを開発する体制をとっているため、技術を各サーバに展開し易く、それぞれに求められる最適な機能や性能を実現することができます。その結果、UNIXサーバ「SPARC M10」に搭載されている最新プロセッサ「SPARC64™ X」には、メインフレームで培った信頼性とスーパーコンピュータに求められる高速性の血が注ぎこまれ、さらにビジネス市場向けに磨きがかけられています。

富士通のUNIXサーバやスーパーコンピュータに搭載されたCPUで採用しているSPARCアーキテクチャは、SPARC Internationalと呼ばれる非営利独立団体で管理されているオープンなアーキテクチャです。その中でSPARC V9という版数のアーキテクチャに基づいて、富士通が開発しているのがSPARC64になります。

このオープンなアーキテクチャを採用することで、我々の思う性能向上策や新規機能をどんどんCPUに取り込んでいくことが可能となります。我々は、お客様の声をできるだけ製品に反映したいと考えており、それを自由に実装できる素材が必要なのです。

以前は、多くのベンダが様々なアーキテクチャのもとでプロセッサ開発に凌ぎを削っていましたが、今ではかなり淘汰されてしまいました。そのような歴史の中、SPARCは現在も多くのお客様にご利用いただいており、その資産は膨大です。プロセッサのアーキテクチャが変わると、その上で動作するソフトウェアに影響が出ます。我々の使命は、このお客様の資産を守るためにアーキテクチャを維持した上で、常に新しい技術を取り込みつつ、性能や機能を強化していくことにある、と考えています。

また、一口にプロセッサ開発といっても、仕様検討、論理設計、レイアウト設計、論理検証、実機検証など、さまざまなフェーズから構成されています。他社では、これらを分業化しているという話も聞きますが、当社はこれらも全て同じ開発者が一貫して担当しています。このような体制があるからこそ、お客様からのニーズを的確に取り込んだ最適な製品を提供できているのだと自負しています。

大貫 祥照(演算器担当)

これまで、プロセッサの高速化のアプローチとして、動作周波数の向上やコア数の増加などに取り組んできた。しかし、他社をリードする性能を実現するためには、技術のブレークスルーが必要であった。

SPARC64 Xは、「Software on Chip」という新しいテクノロジーで技術の壁に立ち向かったと、プロセッサの演算器を担当する大貫は語る。

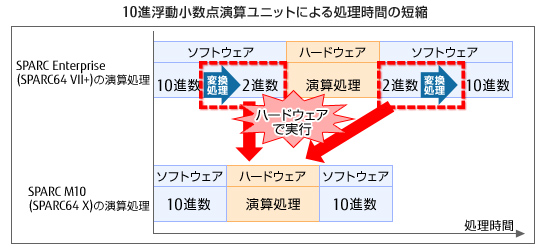

Software on Chipは、従来ソフトウェア上で行われていた処理を、ハードウェア(プロセッサ)上に組み込むという新しいアプローチです。

プロセッサ上に10進浮動小数点演算ユニットを実装することで、これまでソフトウェア上で実施していた、10進数データから2進数データへの変換をなくし、10進数データをそのまま演算できるようにしています。多くのデータベースで採用されている規格(IEEE754)やOracle Databaseで採用されている規格であるOracle Numberもサポートしており、データベースの高速化に貢献できます。

また、スーパーコンピュータで実装されている機能である、SIMD(Single Instruction Multiple Data)をUNIXサーバ用のSPARC64 Xにも取り込んでいます。SIMDとは、一度に複数のデータに対して演算処理を実行させる技術です。SPARC64 Xでは130以上の命令がSIMDに対応しており、これまで以上に、大量のデータを高速に処理することができます。次期プロセッサでも、さらに50近くの命令がSIMDに対応する予定であり、今後も進化を続けていきます。

私達はこのプロセッサの企画の段階からビッグデータを視野に入れたデータベースの高速化を検討してきました。オラクル・コーポレーションのデータベース開発者と密接に連携して、インメモリ型データベースの高速化を追求してきたのです。その中で私達はハードウェア設計者の視点から従来のソフトウェアのボトルネックであった処理を見直し、10進浮動小数点演算や暗号処理、SIMDを用いた並列比較処理などのハードウェアサポート機能を実装しました。その結果、データベース処理全体の性能を大きく向上させることに成功しました。(注1)

Software on Chipはハードウェアとソフトウェアの開発者のコラボレーションが生み出す画期的な成果であり、本システム上でデータベースソフトウェア等のチューニングを実施していただくことで、さらに性能に磨きをかけていくことができます。

我々開発部門には、お客様の性能情報もフィードバックされます。プロセッサだけでなくシステム全体の動きまで視野に入れて精査を行い、次の開発でどのような機能を取り入れたらよいか検討します。このようにシステム全体を見渡して改善のPDCAをまわすことは、プロセッサ専業ベンダでは難しいことで、サーバベンダである富士通だからこそ取り組める「強み」だと考えています。

岩崎 真一(システムコントローラ担当)

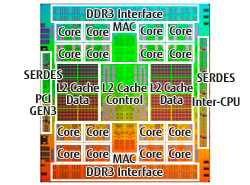

SPARC64 Xは、これまでプロセッサの周辺に実装されていたLSIをプロセッサ上に集約する「System on Chip」という設計手法を採用している。開発に携わった岩崎は、System on Chipがもたらすメリットを語る。

SPARC64 Xでは、CPU間インターフェースや、メモリアクセスコントローラやPCI Expressインターフェースをプロセッサに内蔵しています。これにより、LSI間の距離を短縮化でき、高速化が可能です。さらに、部品点数も削減できますので、システムの信頼性も向上します。

従来のUNIXサーバ SPARC Enterprise M9000では、システムボード上に、プロセッサ、メモリアクセスコントローラ、システムコントローラなどが実装されていましたが、SPARC M10ではプロセッサ上に集約できるため、高性能・省電力・省スペース化に貢献できます。

また、メモリアクセスコントローラをCPUに内蔵し、メモリとCPUを直結したことにより、高いバンド幅や低レイテンシを実現しています。また、メモリにDDR3の最高クラスである「DDR3-1600」を採用し、優れたメモリアクセス性能を実証しています。

- SPARC M10のここがスゴイ! 従来のシステムボードを1つのプロセッサに集約!

- SPARC M10のここがスゴイ! メモリのデータ転送速度が格段に速い!高速アクセスを実現!

山村 周史(2次キャッシュ担当)

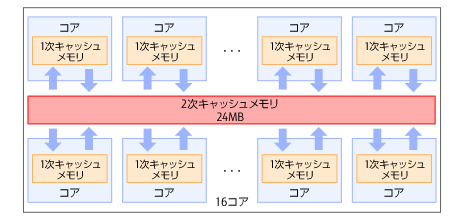

マルチコア化の流れの中、SPARC64 Xは16コアを実現。1次キャッシュメモリはそれぞれのコア内に配置されているが、2次キャッシュメモリは全てのコアで共有されており、その振る舞いが性能に大きく影響する。富士通研究所から自ら志願して、プロセッサ開発部門に異動を果した山村は、2次キャッシュメモリの魅力を語る。

SPARC64 Xの2次キャッシュメモリは、最大24MBの大容量であることが特長です。1つのプロセッサの中で2次キャッシュメモリは共有化されているので、いかに各コア、各プログラムからのリクエストをさばき、平等にリソースを分け与え、とりまわしていくかが重要です。設計にあたっては、多くのプログラムをシミュレーションで動作させて、各コアからの要求を詳細に解析しました。その結果を論理設計にフィードバックしてアルゴリズムを改良し続けました。キャッシュメモリの性能はプロセッサ全体の性能に直結するので、開発者の腕のみせどころだと自負しています。

SPARC64 Xは、CPUコアアクティベーションという仕組みを実現しており、CPUリソースを柔軟に増加させることができます。これは、お客様がSPARC M10を導入された当初は例えば2コアだけを有効にして運用を開始していただき、業務負荷の増大に対応して有効にするコア数を柔軟増やすことができる、という仕組みで、お客様のシステム導入時の初期コストや、運用コスト、ライセンス費用を最小限に抑えることが可能となります。この機構の導入により、CPU内の有効なコア数が増減することになるのですが、どのようなコア構成になっても、それらコアが接続している2次キャッシュは常に24MB全てを使用可能な設計にしており、これは性能面でも大きな強みになっています。

SPARC M10は、16Bulding Block、64CPU/1024コアまで拡張できる圧倒的なスケーラビリティが特長です。この世界最高レベルの機能の実現にも、至るところに信頼性へのこだわりが詰め込まれていると岩崎は語る。

我々は、どんなにシステム規模が大きくなっても、その信頼性の向上に妥協しません。あらゆる故障ケースを想定し、CPU内部の回路にまで疑似的に故障を発生させるなど、信頼性テストを徹底的に行います。その際は、様々なシステム構成を仮想的に実現する機能を用いて、お客様が使用されるあらゆる構成でのテストを実施しています。

コンピュータは絶対に間違えないと思われがちだが、実はそうではない。データ化けには、細心の注意を図っていると、山村は強調する。

半導体の微細化が進む中、宇宙線の衝突などで、0/1で表現される回路内のデータが反転するなどの変化がおこります。その結果、たとえば間違った預金残高の数字が表示されるなどの影響が生じます。

このようなトラブルを防ぐため、SPARC64 Xでは、1つのプロセッサに53000箇所ものエラーチェッカを装備しています。そしてそれらのチェッカでエラーを検出すると、ECCによるデータ訂正やハードウェア命令リトライといった機構でそのエラーをハードウェアが自動的に修復します。そして、万が一、コアやキャッシュで何回もエラーが発生した場合は、故障した部分を動的に縮退させる機能も備えています。他社のプロセッサの中には、エラー発生時に、システムダウンしてしまったり、縮退する前にリブートが必要だったりするケースが多いのですが、SPARC64 Xはメインフレーム譲りの信頼性で故障発生時のお客様の業務への影響を最小限に抑えます。

SPARC64は、ロードマップに示されているように、今後も継続的に開発が続けられる。4人は口を揃える。

プロセッサの開発は、継続と進化の両輪で進めなければなりません。これまで60年もの間培ってきたプロセッサ開発の技術やノウハウを土台に進化させ続け、お客様のビジネスに貢献できる製品を作り続けていきます。

歴代の開発者達の叡智が詰まったプロセッサに、世界一を目指した新たな技術を取り込みながら、挑戦は続いていく。

|

エンタプライズサーバ事業本部

プロセッサ開発統括部 第一技術部 マネージャー 清田 直宏 |

|

エンタプライズサーバ事業本部

プロセッサ開発統括部 第一技術部 大貫 祥照 |

|

エンタプライズサーバ事業本部

プロセッサ開発統括部 第三技術部 岩崎 真一 |

|

エンタプライズサーバ事業本部

プロセッサ開発統括部 第二技術部 山村 周史 |

(注1)Oracle Database 12c にて対応

(注2)本記事中に記載の肩書きや数値、固有名詞等は公開日現在のものであり、このページの閲覧時には変更されている可能性があることをご了承ください。

![]()