メモリのデータ転送速度が格段に速い!高速アクセスを実現!

2013年7月4日

大容量メモリへのアクセスを、超高速に。

SPARC64 Xにはメモリコントローラが内蔵されているため、プロセッサとメモリが直結し、高速アクセスが可能になるように設計されています。従来のSPARC Enterpriseと比較して、メモリレイテンシが最大1/5になりました。

大容量キャッシュとレジスタ

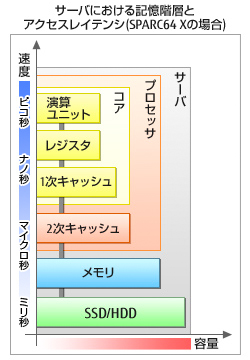

演算処理を行う演算ユニットに一番近い記憶領域であるレジスタとキャッシュは、プロセッサ内にあるため、容量は小さいながらも、高速で動作します。演算ユニットに近ければ近いほど高速性を実現できますが、そのメモリ容量は演算ユニットに近いほど小さく、大容量のメモリ領域を実装することは難問となっています。

メモリのデータ転送を高速化するために、各プロセッサベンダーでは、レジスタ数を増やしたり、キャッシュメモリの大容量化や、1次/2次キャッシュメモリだけでなく、3次キャッシュメモリを設置するなどの改良を行っています。

SPARC64 Xプロセッサは、大量のレジスタや大容量のキャッシュを実装しています。

演算ユニットにより近いレジスタや1次キャッシュ、2次キャッシュに大容量のメモリを設置することで、メモリの高速データ転送を実現しています。

| プロセッサ | 富士通

SPARC64 X |

Intel

Xeon E5-2690 |

IBM

Power 7+ |

|---|---|---|---|

| レジスタ数 | 128 | 32 | 128 |

| 1次キャッシュ(注) | 128KB | 64KB | 64KB |

| 2次キャッシュ | 24MB

(shared) |

256KB | 256KB |

| 3次キャッシュ | N/A | 20MB

(shared) |

80MB

(shared) |

(注)命令+データ

大容量メモリと、それを使いこなす広帯域なメモリバス

SPARC M10は、ビジネスサーバでは世界最高レベルの大容量メモリを搭載できるサーバです。その大容量のメモリを使いこなすために、高速な転送速度を実現するメモリの採用や、メモリバス本数の増強をしています。

SPARC M10のメモリはDDR3メモリを採用しています。DDR3メモリと言っても、メモリの周波数や転送速度によって、複数の種類に分かれています。

SPARC M10に搭載する8GB DIMM/16GB DIMMは、DDR3メモリの中でも高速な「DDR3-1600」のメモリを採用しています。メモリの周波数は1600MHzと、多くのビジネスサーバで採用されている1066MHzや1333MHzのメモリと比べて、データ転送速度が高速なメモリです。

| チップ規格

(モジュール規格) |

データ転送速度

(サイクル) |

モジュールのデータ転送速度 |

|---|---|---|

| DDR3-1600

(PC3-12800) |

1,600MHz | 1,600MHz x 8Byte = 12,800MB/秒 = 12.8GB/秒 |

| DDR3-1333

(PC3-10600) |

1,333MHz | 1,333MHz x 8Byte ≒ 10,667MB/秒 = 10.667GB/秒 |

| DDR3-1066

(PC3-8500) |

1,066MHz | 1,066MHz x 8Byte ≒ 8,533MB/秒 = 8.533GB/秒 |

| DDR3-800

(PC3-6400) |

800MHz | 800MHz x 8Byte = 6,400MB/秒 = 6.4GB/秒 |

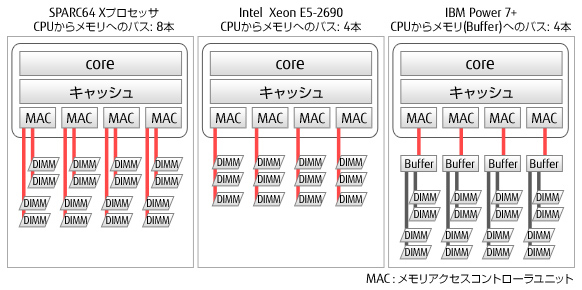

サーバとストレージ間で発生するI/Oボトルネックと同じように、プロセッサとメモリ間でもデータ転送にボトルネックが生じます。SPARC64 Xは、コアの高性能化やコア数の増加など、演算部分の性能向上に合わせて、メモリコントローラ数を増加させたり、メモリバス本数を増やしたり、メモリ容量を大容量化しています。バランスよく動作させることで、プロセッサの真価を発揮します。

そのため、SPARC64 Xプロセッサに搭載されたメモリコントローラからメモリへのバス本数も他社に比べて多く実装しています。他社プロセッサでは、4本のメモリバスが主流となっていますが、SPARC64 Xには2倍の8本のメモリバスが実装されているため、さらなる高速性を実現します。

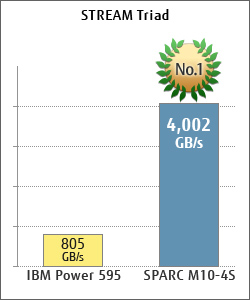

メモリアクセス性能の良さをベンチマークで証明

このように、メモリの高速性を最大限に活かせるように設計されたSPARC M10は、メモリアクセス性能指標として使用されるベンチマーク「STREAM」において、SPARC M10は世界最高性能を達成しています。(2013年6月11日現在)

- SPARC M10-4S STREAMで世界最高性能を達成(HPC用途を除いた登録値との比較)

- SPARC M10-4S STREAM 16CPUクラスで世界最高性能を達成