# 65nm CMOS Process Technology

Paul Kim

Senior Manager, Foundry Services

Fujitsu Microelectronics America, Inc.

### New 300mm Fabs – Mie, Japan

#### 300mm Fab No.2

- Process

- •65nm/90nm CMOS Logic

- Structural Features

- •Seismic-vibration control construction

- •Clean room area: 24,000 sq. meters

- Production Capacity

- •10,000 wafers per month (FY07 projection)

- •Maximum capacity of 25,000 wafers per month

- Planned Start of Operation

- •April 2007

#### 300mm Fab No.1

- Process

- •90nm/65nm CMOS Logic

- Structural Features

- Seismic-control construction

- •Clean room area: 12,000 sq. meters

- Production Capacity

- •15,000 wafers per month (FY06)

- Start of Operation

- •April 2005

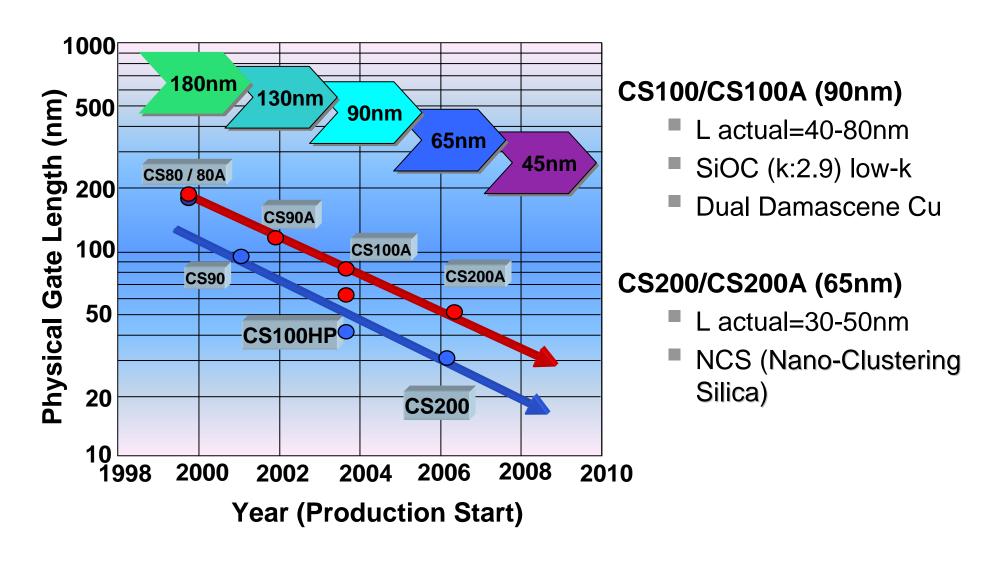

## **CMOS Technology Roadmap**

## Proven Track Record of 90nm Complex Designs and Products

#### Processors for PRIMEPOWER

Achieves world-leading performance and reliability

### Chipset for PRIMEQUEST

Achieves mainframe-class reliability and scalability

Helped reduce development time

### Baseband chip for FOMA 3G mobile phones

LSI power consumption reduced 50% (compared to existing tech)

All Rights Reserved, ©Fujitsu Limited 2005

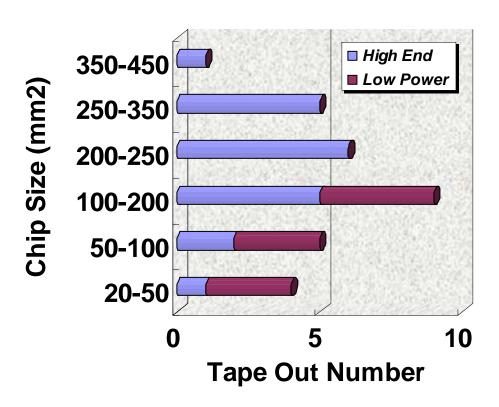

## Proven Track Record of 90nm Complex Designs and Products – continued

#### **High-performance Products**

- PC CPU (Transmeta)

- Large-scale FPGA (Lattice)

- Others

#### **Low-power Products**

- Multimedia processor

- Digital AV products

- Others

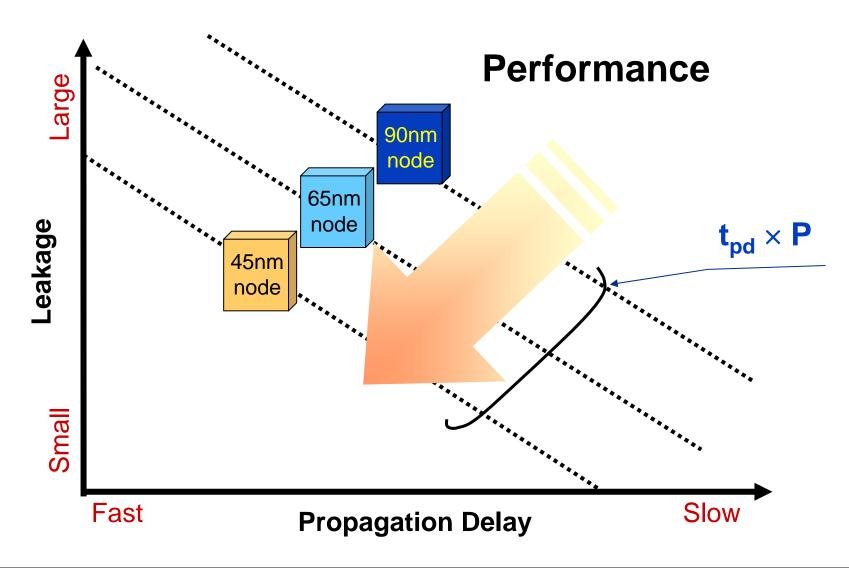

#### 65nm, CS200 / 200A Features

#### Features

- Ultra-high-speed performance (CS200)

- L<sub>G</sub> = 30nm, on-current enhance

- Compared to 90nm technology, CS200 offers:

- 1.3 times faster speed

- 0.6 times lower power

- 2 times higher density

- 3 variations of V<sub>th</sub> on a chip (CS200A)

- (1.8V & 2.5V) or (1.8V & 3.3V) I/O combination available

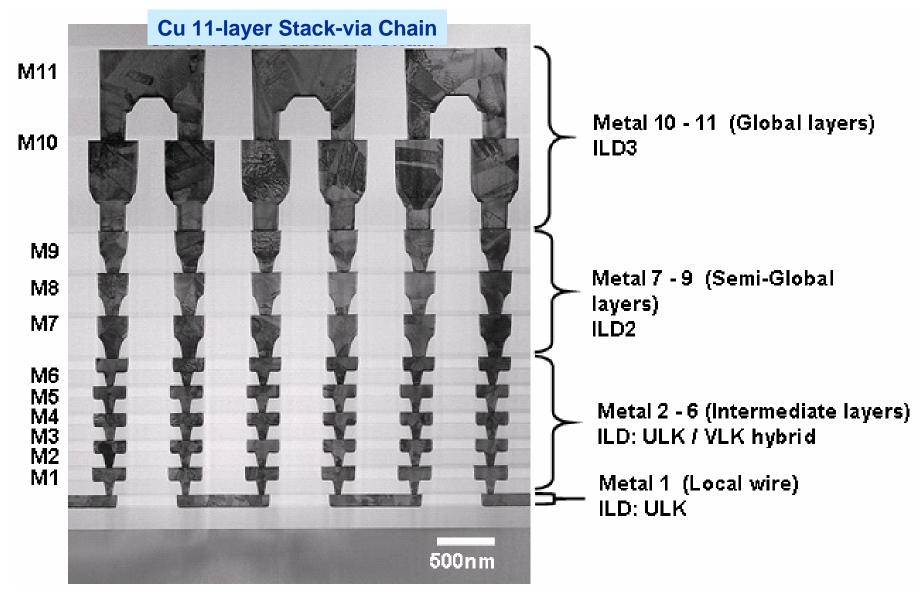

- 11-layer copper interconnects with robust, very low K ILD

### CS200 / 200A Transistor Variations

CS200: Ultra High Speed

CS200A: Wide Speed Range + Low Power Consumption

Large HS-1 **CS200** Server/ **Network** STD-Tr current **High End HVt-Tr** Server **CS200A** HS-TN Mobile Computing Leakage STD-Tr Digital Consumer **HS:High speed** STD:Standard **Cellular Phone** LL:Low leakage

**Speed**

**Fast**

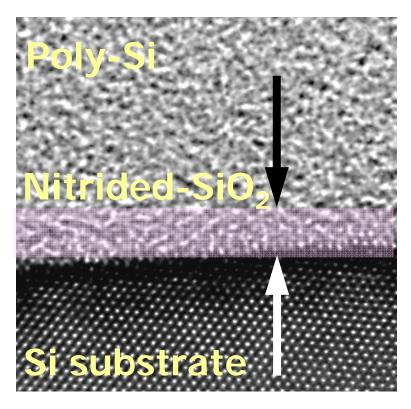

## **Leading-edge Transistors**

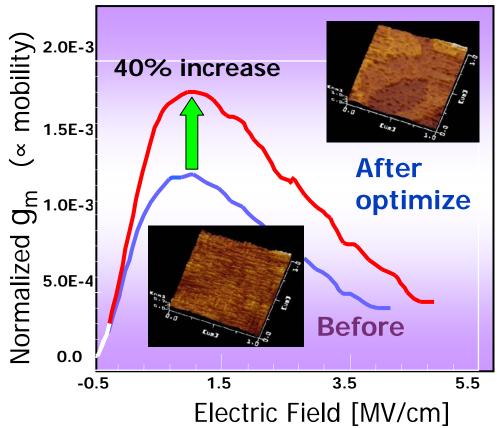

## Leading-edge Technology Ultra-Thin Gate Insulator / **Mobility Improvement**

#### **1nm-thick Gate Oxide**

### **Surface Cleaning**

## **Speed Performance Improvements**

|                                           | 65nm<br>CS200<br>( <u>ps/gate</u> ) | 90nm<br>CS100<br>( <u>ps/gate</u> ) | Delay<br>Improvement |

|-------------------------------------------|-------------------------------------|-------------------------------------|----------------------|

| Inverter                                  | 5.7                                 | 7.0                                 | 19%                  |

| 2-input NAND                              | 8.7                                 | 11.4                                | 24%                  |

| 2-input NAND + 200 grid interconnect load | 23.1                                | 30.8                                | <b>25%</b>           |

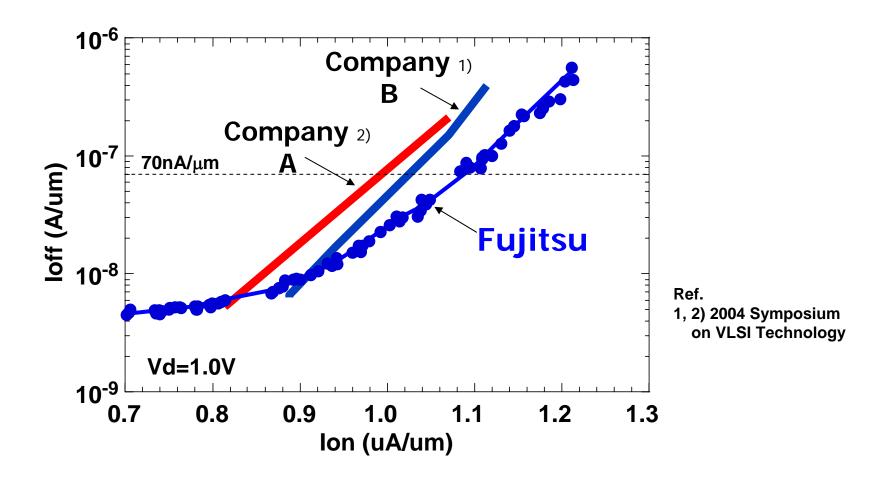

## **High-Performance Competitive Transistors**

#### Ion vs loff Characteristics of nMOSFETs

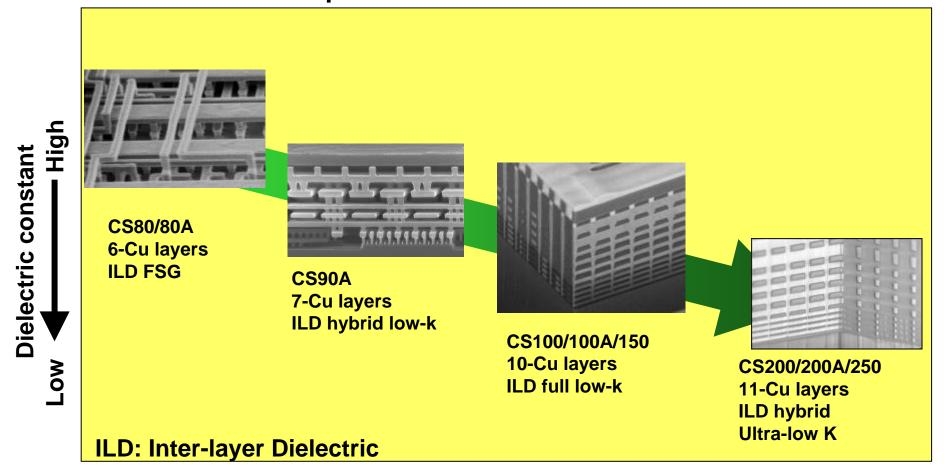

#### Advanced Cu and Low-k

#### **Four Generations of Experience**

180nm node

130nm node

90nm node

65nm node

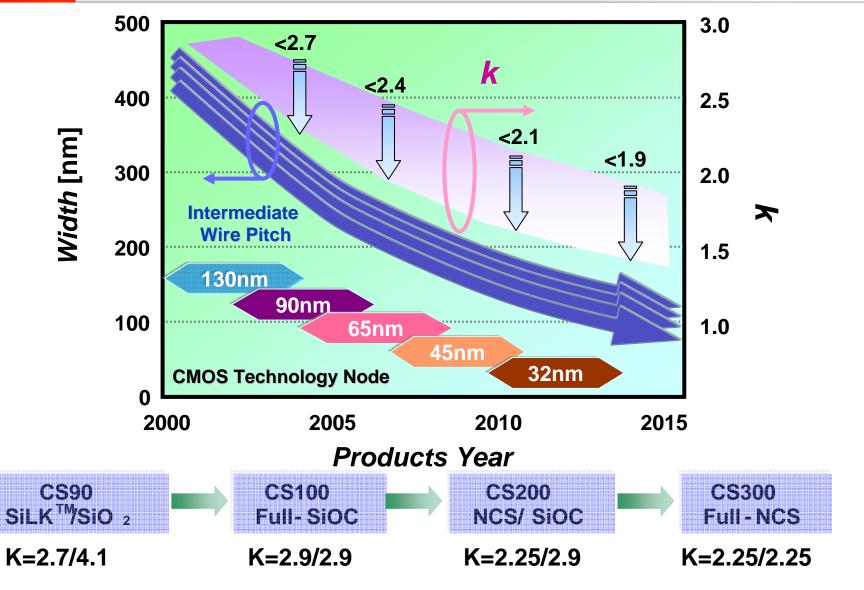

## Fujitsu's Low-k Leads ITRS

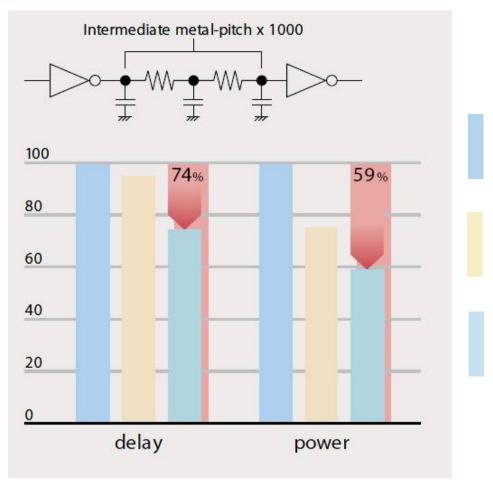

## Low-k Advantages of 65nm

#### Ultra low-k impacts on speed and power dissipation

**CS100A (90nm)**

with SiOC/SiOC

Rsh:  $90m\Omega/sq.$ , C: 56fF/1000 grid

**CS200A (65nm)**

with SiOC/SiOC

Rsh: 150m $\Omega$ /sq., C: 52fF/1000 grid

**CS200A (65nm)**

with NCS/SiOC

Rsh:  $150m\Omega/sq.$ , C: 40fF/1000 grid

### 11-Layer Copper Interconnects

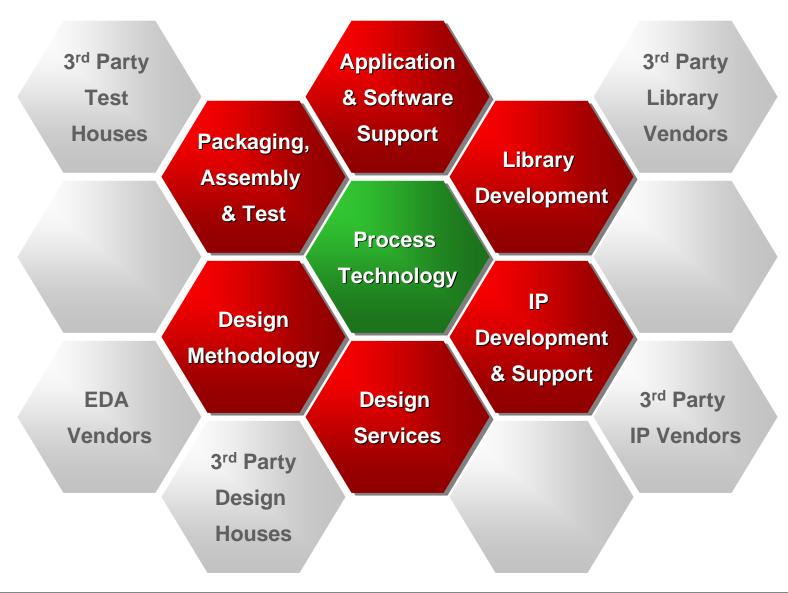

## The Fujitsu Ecosystem

## **Fujitsu Technology Access**

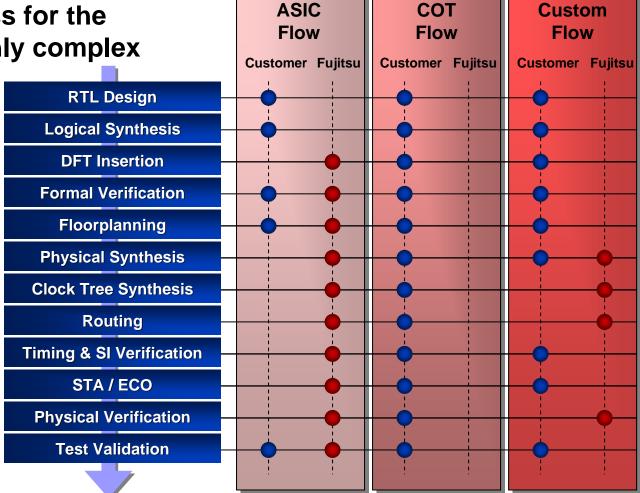

Flexible collaboration models provide easy access to Fujitsu's leading-edge process for the development of highly complex

silicon products

## **Design Flow & Methodology**

- Reference design flow Fujitsu's leading-edge design methodology focuses on timing, signal and power integrity closure

- Support for both Cadence SOCEncounter<sup>TM</sup> and Synopsys Galaxy<sup>TM</sup> platforms

- In-house CAD software development augments leading third-party EDA solutions

- Ensures silicon correlation and a fast path to silicon success by combining Fujitsu's strengths in process, CAD tool and methodology development with design experience and expertise

- Production proven flows used on 100+ multi-million-gate designs at 180, 130 and 90nm

- Constantly updated and improved to address all issues at each process node

## Fujitsu Design Services

- Library and tool support

- Methodology development and support

- High-speed I/O design and expertise

- Vertical expertise and IP cores

- RTL design

- Synthesis and physical synthesis

- Design partitioning and floorplanning

- Static timing analysis

- Test insertion and ATPG generation

- Place and route

- Timing and SI closure

- Formal verification

- Physical verification

- Test and product engineering

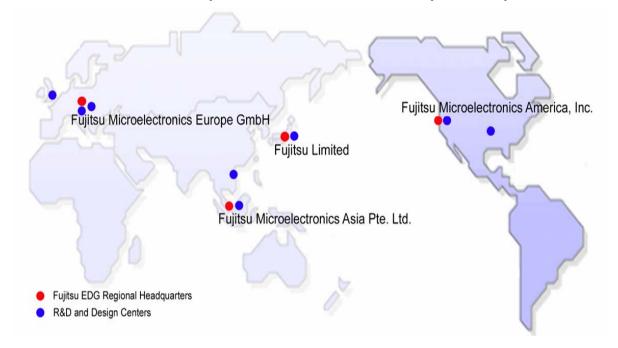

### **Fujitsu Worldwide Design Centers**

#### Global Presence

Local design centers around the world provide design services for all phases of the development process

- Skilled engineering teams experienced in development of large complex designs at 130nm and below

- 100+ multi-million gate designs taped out

# Summary

#### Fujitsu Objective

Helping customers accelerate their innovation, differentiate their products and enhance their competitive advantage, therefore helping them succeed

#### Leading-edge technologies

- Strength in process technologies

- 90nm, 65nm and beyond

- Partnerships and customer collaborations

- Flexible customer engagements and close collaborations

- Early customer engagements

- Tailored support and services to meet customer needs

- System-level LSI solutions

- ASIC and ASSP/SoC, including10GbE switch chip and WiMAX SoC

- Full design and development environments and support

THE POSSIBILITIES ARE INFINITE