Archived content

NOTE: this is an archived page and the content is likely to be out of date.

Fujitsu Laboratories Develops CMOS Transmitter IC for 40Gbps Optical Transmission Systems

- World's first 65nm standard CMOS-based single-chip integration of all functions necessary for 40Gbps transmitter ICs -

Fujitsu Laboratories Ltd.,Fujitsu Laboratories of America Inc.,Fujitsu Limited

-

[1] CMOS technology

A semiconductor technology comprised of N-type and P-type metal-oxide semiconductor (MOS) transistors with complementary connections, created on a silicon substrate. Attributable to their low power requirements, CMOS integrated circuits are currently the mainstream.

-

[2] I/O interface (Input/Output interface)

Refers to functions for I/O signal logic and sequencing, and transmitter IC operation mode, which can be controlled using I2C bus interface.

-

[3] Signal processing

Refers to the following functions: a data-recovery function that enables five 10Gbps electrical signals to be received without error, a function that accommodates timing errors between these five signals, and a function that synchronizes the timing of these signals.

-

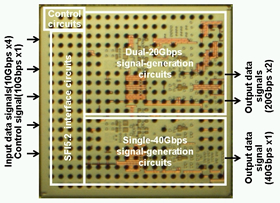

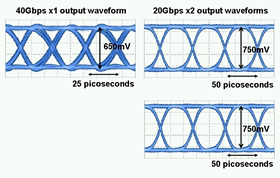

[4] High-speed signal generation

A function that receives four 10Gbps electrical signals, and generates either two 20Gbps electrical signals or one 40Gbps electrical signal.

-

[5] Compound semiconductor

A semiconductor formed using two or more elements, such as gallium-arsenide (GaAs) or indium-phosphide (InP), and which features higher electron mobility than silicon, therefore permitting faster operation.

-

[6] Parasitic capacitance

Undesirable static capacitance that emerges between a transistor element's Input/Output (I/O) electrodes, or between the transistor and electrodes of peripheral elements surrounding the transistor. The amount of parasitic capacitance varies depending on the electrode size of the elements or distance between elements, thus making it impossible to indicate parasitic capacitance in schematic circuit diagrams.

-

[7] Inductor

A coil element in which electrical conductivity becomes more difficult at higher frequencies (passes low-frequency signals, but resists passage of high-frequency signals). Inductors are usually formed as coil circuit patterns on semiconductors.

-

[8] SFI5.2

Serdes Framer Interface Level 5 Phase 2. Refers to a standard promulgated in October 2006 at the Optical Internetworking Forum (OIF) 2006.

About Fujitsu Laboratories

Founded in 1968 as a wholly owned subsidiary of Fujitsu Limited, Fujitsu Laboratories Limited is one of the premier research centers in the world. With a global network of laboratories in Japan, China, the United States and Europe, the organization conducts a wide range of basic and applied research in the areas of Multimedia, Personal Systems, Networks, Peripherals, Advanced Materials and Electronic Devices. For more information, please see:http://jp.fujitsu.com/group/labs/en/

About Fujitsu Laboratories of America, Inc.

Fujitsu Laboratories of America, Inc. is a wholly owned subsidiary of Fujitsu Laboratories Ltd. (Japan), focusing on research on advanced VLSI CAD, Internet, and interconnect technologies. Conducting research in an open environment, it contributes to the global research community and the working IT industry. It is headquartered in Sunnyvale, CA.

For more information, please see: www.fla.fujitsu.com

About Fujitsu

Fujitsu is a leading provider of IT-based business solutions for the global marketplace. With approximately 160,000 employees supporting customers in 70 countries, Fujitsu combines a worldwide corps of systems and services experts with highly reliable computing and communications products and advanced microelectronics to deliver added value to customers. Headquartered in Tokyo, Fujitsu Limited (TSE:6702) reported consolidated revenues of 5.3 trillion yen (US$53 billion) for the fiscal year ended March 31, 2008. For more information, please see: www.fujitsu.com.

Technical Contacts

Network SOC Development Lab.System LSI Development Lab.

![]() Phone: +81(44)754-2692

Phone: +81(44)754-2692

![]() E-mail: 40g_pr@ml.labs.fujitsu.com

E-mail: 40g_pr@ml.labs.fujitsu.com

Company:Fujitsu Laboratories Limited

Company and product names referenced herein are trademarks or registered trademarks of their respective owners. Information provided in this press release is accurate at time of issue and is subject to change without advance notice.

Date: 13 February, 2009

City: Kawasaki and Tokyo, Japan and Sunnyvale, U.S.

Company:

Fujitsu Laboratories Ltd.,

Fujitsu Laboratories of America, Inc.,

Fujitsu Limited,

,

,