# Approaches to Using Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> as Gate Dielectrics for CMOSFETs

Yoshihiro Sugiyama

Sergey Pidin

Pidin • Yusuke Morisaki (Manuscript received January 21, 2003)

We report on recent approaches to using Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> in MOSFETs. A MOS diode with an Al<sub>2</sub>O<sub>3</sub> gate dielectric into which dimethylhydrasin (DMH) was doped shows a minimum  $D_{it}$  of  $4 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup>, which is half that of Al<sub>2</sub>O<sub>3</sub>. Mobility enhancement and an increase of saturation current were obtained with the DMH-doping. A SiN/HfO<sub>2</sub>/SiON gate stack was found to suppress HfO<sub>2</sub>/polysilicon reaction and dopant diffusion. The base oxide of SiON also helps to improve the reliability and thermal stability of the gate stack. An inversion EOT of 1.7 nm was obtained with a SiN/HfO<sub>2</sub>/SiON gate stack that shows a saturation current of 357  $\mu$ A/ $\mu$ m at L<sub>9</sub> of 0.35  $\mu$ m. A 55 nm CMOS with a 3 nm HfO<sub>2</sub> gate dielectric was fabricated using high-temperature annealing at  $\geq 1000^{\circ}$ C and cobalt silicide. Gate leakage current was decreased by more than three orders of magnitude and a low off-state current was obtained. We also investigated the thermal stability of Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub>. Within  $0 \le x \le 0.8$ , Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub> stays amorphous up to 800°C, which is 300°C higher than the corresponding temperature for HfO<sub>2</sub>.

## 1. Introduction

Down-scaling to sub-100 nm technology nodes requires the introduction of novel materials and processes to both the front end of line and back end of line to achieve the performance indicated in the ITRS roadmap. Channel engineering of nondoped channels, strained Si,<sup>1),2)</sup> and strained SiGe<sup>3)</sup> can be considered to be the most practical method that is compatible with conventional processes. However, gate oxide scaling is reaching the point where gate leakage current due to direct tunneling starts to occur. Although optimization of the silicon nitride/oxynitride stack<sup>4)</sup> and SiON gate<sup>5)</sup> is being pursued to suppress the leakage current, the inevitable issues of negative bias temperature instability<sup>6)</sup> and mobility lowering must also be considered.<sup>7)</sup> To overcome these problems, an alternative gate dielectric with high permittivity (high-k) is strongly required for both high-performance and low standby power (LSTP) applications.

High-k materials have been extensively studied in recent years. Ta<sub>2</sub>O<sub>5</sub> was one of the first materials that were eagerly studied for their high permittivity.<sup>8),9)</sup> Because Ta<sub>2</sub>O<sub>5</sub> is unstable on a Si surface,<sup>10)</sup> Ta<sub>2</sub>O<sub>5</sub> tends to form an underlying SiO<sub>2</sub> film at the Ta<sub>2</sub>O<sub>5</sub>/Si interface during deposition that significantly decreases the effective capacitance. The barrier height of Ta<sub>2</sub>O<sub>5</sub> from silicon is as small as 0.28 eV.<sup>11)</sup> Then, researchers became very interested in zirconium oxide because its heat of formation is larger than that of  $SiO_2^{(12)}$  and it exhibits medium permittivity in addition to a relatively large band gap and barrier height compared to  $Ta_2O_5$ .<sup>13)</sup> However,  $ZrO_2$  reacts with the poly silicon gate that forms Zr-silicides.<sup>14)</sup> Consequently, HfO<sub>2</sub>, whose Hf constituent is in the same column of the periodic table as zirconium, emerged as a significant gate-dielectric candidate<sup>15)</sup> because it forms fewer silicides than ZrO<sub>2</sub> and its permittivity and barrier height are comparable to those of  $ZrO_2$ . This promising material exhibits crystallization even with an as-grown CVD thin film.<sup>16)</sup> Crystallization may give rise to a leakage path for current and dopant impurities from the polysilicon gate.<sup>17)</sup> Because high-k MOSFETs can be fabricated using conventional CMOS process technology, the thermal stability is one of the most important criteria that must be considered when selecting materials. Al<sub>2</sub>O<sub>3</sub> exhibits a high thermal stability; it remains in the amorphous phase even during annealing at > 1000°C.<sup>18)</sup>

Recently, nitrogen doping and nitridation of high-k gate dielectrics have been reported.<sup>18)-22)</sup> Nitrogen in high-k gate dielectrics can be expected both to suppress boron diffusion from the polysilicon gate and to increase the thermal stability. Although nitrogen is usually incorporated before or after high-k deposition, there have been few reports of in-situ nitrogen doping into high-k gate dielectrics.<sup>20)</sup> Also, a stacked gate with a nitrided film and a high-k film should be studied to investigate the effectiveness of nitrogen.<sup>23)</sup>

In this paper, we describe high-k MOSFETs with an  $Al_2O_3$  film, mainly focusing on in-situ nitrogen doping into the  $Al_2O_3^{(20)}$  by MOCVD. Then, we evaluate the effectiveness of SiN and SiON insertions at both sides of a HfO<sub>2</sub> gate dielectric and apply them to an ultra-thin gate stack.<sup>23)</sup> Then, we show the feasibility of high-k, HfO<sub>2</sub> gate dielectrics for low standby power applications.<sup>24)</sup> Finally, we compare the thermal stabilities of Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub> and HfO<sub>2</sub>.

## 2. Preparation of high-k gate dielectrics and MOSFETs

2.1 Al<sub>2</sub>O<sub>3</sub>

We used low-pressure metalorganic chemical vapor deposition (LP-MOCVD) to deposit an  $Al_2O_3$  film on a Si substrate. The precursors were triethyl aluminum (Al( $C_2H_5$ )<sub>3</sub>, TEA) and dimethylhydrasin (NH<sub>2</sub>N(CH<sub>3</sub>)<sub>2</sub>, DMH) as a nitrogen source. The precursors were regulated with a nitrogen carrier gas.  $O_2$  gas was used as an oxidant. A Si substrate with LOCOS isolation was chemically cleaned by the RCA method prior to the MOCVD. The substrate was heated to the deposition temperature of 500°C.

The conductance method<sup>25)</sup> was used to investigate the interface trap density of  $D_{it}$  using the three-element model.<sup>26)</sup> In the investigation, a quantum-mechanical CV simulation was used to derive the equivalent oxide thickness (EOT), flat band voltage (V<sub>fb</sub>), and hysteresis.

## 2.2 HfO<sub>2</sub>

$HfO_2$  was deposited by ALCVD on a thermally grown oxynitride layer (bottom SiON) or a chemical oxide layer (bottom SiO<sub>2</sub>) after standard RCA cleaning. The typical  $HfO_2$  layer was 3 nm thick. To form a gate stack with a thinner EOT, the  $HfO_2$  layer thickness was decreased and an LPCVD-SiN layer was grown on the  $HfO_2$  (top SiN) to suppress silicide formation and dopant penetration. This was followed by poly-Si gate deposition. We used the split CV method at 100 kHz to measure the gate capacitance in the inversion region.

## 2.3 $Hf_xAI_{1-x}O_y$

$Hf_xAl_{1-x}O_y$  was deposited by the same method as the one used for  $Al_2O_3$ . The composition ratio (atomic percentage ratio) of x was defined by Rutherford Back Scattering (RBS) and spectroscopic ellipsometry. The thermal stability was estimated by X-ray diffraction (XRD) and cross-sectional transmission electron microscopy (XTEM).

### 2.4 Device fabrication process

After high-k gate dielectric film deposition, post-deposition annealing and sequential polysilicon deposition were performed. The polysilicon was patterned with EB or photolithography using dry etching. The minimum gate length,  $L_{CAD}$ , was 50 nm. After extension and pocket implantation, if needed, a side wall of the polysilicon gate was formed and source/drain/gate implantation

was performed. The following activation annealing was done in the range from  $800^{\circ}$ C to  $1050^{\circ}$ C. Metal Co-silicide contacts were used except for the Al<sub>2</sub>O<sub>3</sub> MOSFETs. Post metallization annealing was performed at  $450^{\circ}$ C in an H<sub>2</sub>/N<sub>2</sub> ambient.

## 3. Results and discussion

## 3.1 Al<sub>2</sub>O<sub>3</sub> gate dielectrics

$Al_2O_3$  exhibits a high thermal stability. If nitrogen could be readily incorporated, dopant diffusion would be suppressed and any negative fixed charge would be neutralized. In this section, we investigate the effect of in-situ nitrogen doping into  $Al_2O_3$  using DMH, which is as an active source of nitrogen.

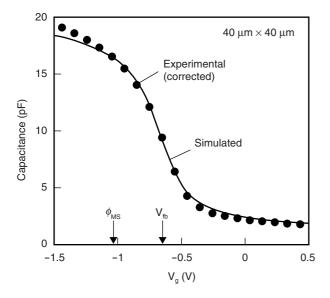

**Figure 1** shows the CV characteristics of an  $Al_2O_3$  MOS diode that is 3.5 nm thick. We corrected experimental capacitance data using the three-element model with a series resistance determined by Vogel's method.<sup>26)</sup> The CV parameters obtained by fitting a quantum mechanical simulator to the calibrated data and setting a gate leakage current of  $J_g$  at  $V_{fb}$ -1 V are shown in **Table 1**. We also fabricated DMH-doped, nMOS

Figure 1

$C\bar{V}$  characteristics of 40  $\mu m^{\Box}$   $Al_2O_3$  MOS diode. Circles show corrected capacitances obtained using the three-element model. Solid line shows a simulated result that accounts for quantum mechanical effects.

and pMOS versions of this 3.5 nm, Al<sub>2</sub>O<sub>3</sub> MOS diode. Compared to the non-DMH-doped diodes, the EOT and hysteresis are slightly lower in the nMOS and the pMOS,  $\Delta V_{fb}$  is higher in the nMOS and lower in the pMOS, and  $J_g$  is higher in the nMOS and the pMOS. The source/drain annealing conditions were 950°C for 10 s for pMOS and 1000°C for 5 s for nMOS. Changing the annealing temperature of the pMOS diode from 800°C to 950°C made little difference to the work function difference between the polysilicon gate and well. Nitrogen in silicon oxynitride induces a positive charge. Therefore, the decrease of  $\Delta V_{fb}$  in pMOS may be caused by the introduction of N to the Al<sub>2</sub>O<sub>3</sub> film. Actually, N was distributed around the Al<sub>2</sub>O<sub>3</sub>/Si-substrate interface with a peak density of about 0.5%. The opposite shift of  $\Delta V_{fb}$  in nMOS is not well understood. Since the precursors include alkyl groups, other chemical reactants may contribute to the shift and the increase of J<sub>g</sub>.

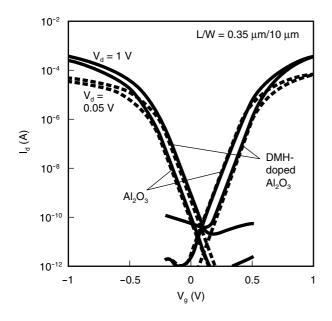

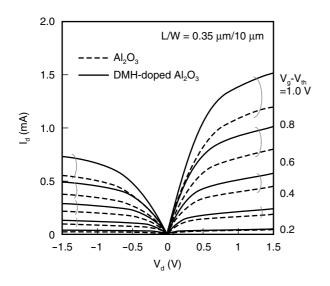

**Figure 2** shows the  $I_d$ - $V_g$  characteristics of  $Al_2O_3$  MOSFETs with and without DMH doping. Both types of MOSFETs show a subthreshold slope of 70 mV/decade. The  $I_d$ - $V_g$  of the  $Al_2O_3$  MOSFET is unsymmetrical and is further shifted in the positive direction by DMH doping. The nMOSFET shows a larger  $V_{th}$  shift, which corresponds to the results of MOS diodes. **Figure 3** shows the  $I_d$ - $V_d$  characteristics. The DMH-doped  $Al_2O_3$  MOSFET apparently shows a higher current drivability ( $I_{dsat}$  [ $I_{on}$ ]) than that of the  $Al_2O_3$  MOSFET, even when the gate overdrive is taken into consideration. **Figure 4** shows the normalized transconductance

Table 1

CV parameters and leakage current of  $\rm Al_2O_3\,MOS$  diodes with and without DMH doping.

|                         | nMOS                           |                                             | pMOS      |                                             |

|-------------------------|--------------------------------|---------------------------------------------|-----------|---------------------------------------------|

|                         | Al <sub>2</sub> O <sub>3</sub> | DMH-doped<br>Al <sub>2</sub> O <sub>3</sub> | $AI_2O_3$ | DMH-doped<br>Al <sub>2</sub> O <sub>3</sub> |

| EOT (nm)                | 2.6                            | 2.5                                         | 2.5       | 2.3                                         |

| Hys. (V)                | 0.06                           | 0.05                                        | 0.16      | 0.07                                        |

| $\Delta V_{fb}$ (V)     | 0.42                           | 0.47                                        | 0.23      | 0.17                                        |

| Jg (A/cm <sup>2</sup> ) | 0.003                          | 0.02                                        | 0.1       | 0.5                                         |

Figure 2

$I_{d}$ - $V_{g}$  characteristics of  $AI_{2}O_{3}$  MOSFETs with and without dimethylhydrasin (DMH) doping. L/W = 0.35  $\mu$ m/10  $\mu$ m.

Figure 3

$I_d\mathchar`-V_d$  characteristics of  $AI_2O_3$  MOSFETs with and without DMH doping. L/W = 0.35  $\mu\mbox{m}/10~\mu\mbox{m}.$

$(g_m)$ -gate voltage relationship of the  $Al_2O_3$  MOSFET. The capacitive effective thickness (CET) is defined as the  $C_{max}$  in the accumulation region of the CV curve. We used a MOSFET with a SiON gate dielectric as a reference. The difference in normalized transconductance between  $Al_2O_3$  and

#### Figure 4

Normalized  $g_m$ -V<sub>g</sub> characteristics of Al<sub>2</sub>O<sub>3</sub> MOSFETs with and without DMH doping (L/W = 0.35  $\mu$ m/10  $\mu$ m) and for a reference MOSFET with a SiON gate dielectric.

the reference MOSFETs is large. However, the effect of DMH-doping into the  $Al_2O_3$  clearly contributes to a mobility enhancement over the entire range. Since it is well known that MOSFETs with  $Al_2O_3$  gate dielectrics show a lower effective mobility due to a large amount of ionized, scattered particles near the lower interface of the high-k,<sup>27)</sup> we also consider that this lower  $g_m$  is caused by Coulomb scattering near the channel.

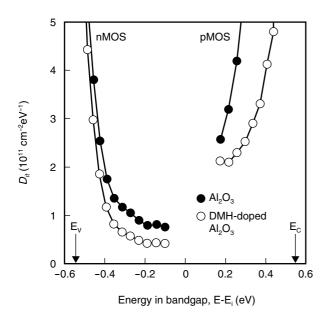

**Figure 5** shows the energy dispersion of the interface trap density,  $D_{it}$ , at the lower interface of the high-k. To obtain  $D_{it}$ , we used the conductance method and the following relationship:<sup>20),25)</sup>

$$D_{ii} = \frac{2.5}{q} \left( \frac{G_p}{\omega} \right)_{MAX}$$

(1)

The samples used were MOS diodes with a large area of 160  $\mu$ m<sup> $\Box$ </sup> to increase the signal-to-noise ratio. The diodes were on the same wafer as the MOSFETs. The DMH-doped Al<sub>2</sub>O<sub>3</sub> MOS diodes show a lower  $D_{it}$  in the whole range of p- and n-types. The pMOS had a larger  $D_{it}$  because they were subjected to a lower activation annealing temperature (950°C) than the nMOS (1000°C).

Figure 5

Energy dispersion of interface trap density ( $D_{ii}$ ) of Al<sub>2</sub>O<sub>3</sub> MOS diodes with and without DMH doping. Samples are 160 µm<sup>D</sup> and were fabricated on the same wafer as the MOSFETs.

This temperature difference strongly affects the formation of  $D_{it}$ . A minimum  $D_{it}$  of  $4 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> was obtained in the DMH-doped Al<sub>2</sub>O<sub>3</sub> MOS diode near the midgap, which is half of that obtained in the Al<sub>2</sub>O<sub>3</sub> MOS diode. Since the DMH-doping slightly decreases the EOT, interface layer growth could be suppressed even with a nitrogen content as low as 0.5%, which helps decrease the  $D_{it}$ . Although, as discussed previously, other causes can be considered, this mobility enhancement and increase of I<sub>dsat</sub> is attributed to DMH-doping into the Al<sub>2</sub>O<sub>3</sub>.

### 3.2 Ultra-thin HfO<sub>2</sub> gate stack

As far as  $J_g$  is concerned, it is crucial that we suppress chemical reactions between the polysilicon gate and high-k material, especially in an ultra-thin gate stack. As is the case that the reaction between  $ZrO_2$  and polysilicon is well understood, an  $HfO_2$ /polysilicon interface also shows area-dependent breakdown characteristics.<sup>28)</sup> In addition to a base oxide of SiON, we investigated the effect of a SiN insertion layer

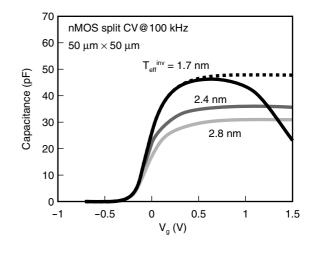

Figure 6 CV characteristics of nMOS diodes with SiN/HfO<sub>2</sub>/SiON gate stacks in the inversion region. Area is 50  $\mu$ m<sup>D</sup>. Measurement frequency was 100 kHz.

between the HfO<sub>2</sub> and polysilicon gate.

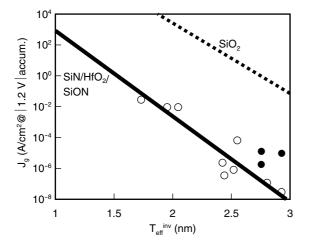

Figure 6 shows the CV characteristics in the inversion region of SiN/HfO<sub>2</sub>/SiON gate stacks having three different thicknesses. The decrease of capacitance at higher gate voltages is due to gate leakage; however, the inversion EOT, T<sub>eff</sub><sup>inv</sup>, was estimated to be 1.7 nm. This means that after gate depletion and the inversion layer thicknesses have been factored in, we can expect to achieve an EOT as small as 0.9 nm. Figure 7 shows the  $J_g$ - $T_{eff}^{inv}$  relationship for the SiN/HfO<sub>2</sub>/ SiON gate stacks.  $J_g$  was defined as the leakage current at  $V_g = 1.2$  V in the accumulation region. A  $J_g$  of less than 30 mA/cm<sup>2</sup> at 1.2 V was obtained with a  $T_{eff}^{inv}$  of 1.7 nm. These devices have a  $J_g$ that is 5 to 6 orders of magnitude smaller than that of a reference SiO<sub>2</sub> gate stack. We investigated the effect of a SiN layer on the breakdown voltage of V<sub>BD</sub>. We prepared SiN/HfO<sub>2</sub>/SiON, HfO<sub>2</sub>/ SiON, and HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks with, respectively, a  $T_{eff}^{inv}$  of 2.4 nm, 2.5 nm, and 2.6 nm. The SiN/ HfO<sub>2</sub>/SiON gate stack showed a small distribution and a  $V_{\text{BD}}$  as high as -4 V, while the other two gate stacks showed a very low  $V_{BD}$  of under –1.3 V. The area dependence of the  $V_{BD}$  of the SiN/HfO<sub>2</sub>/SiON gate stack was also quite small. These results imply that the SiN layer on the HfO<sub>2</sub> completely

Figure 7

$J_g^- T_{\rm eff}^{\rm inv}$  relationship of SiN/HfO<sub>2</sub>/SiON gate stack.  $J_g$  was defined as the leakage current at  $V_g$  = 1.2 V in the accumulation region. White circles are for nMOS, and black circles are for pMOS. The dotted line shows the case for SiO<sub>2</sub>.

suppressed the partial reaction between the  $HfO_2$ and the polysilicon gate. This phenomenon was confirmed by AES analysis. In addition, we also observed that the SiN top layer suppressed gate dopant diffusion through the gate stack. Therefore, the SiN/HfO<sub>2</sub>/SiON gate stack is a promising technology for realizing ultra-thin, gate stacks in 65 nm nodes and beyond.

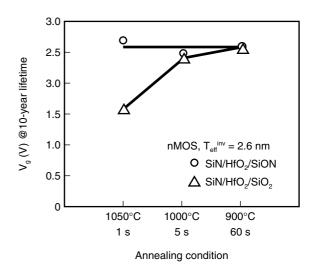

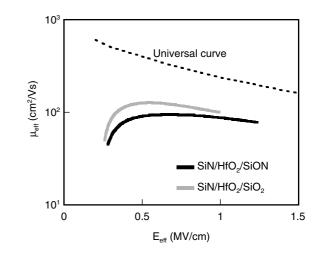

We now focus on the effects of the base oxide on reliability and mobility. Figure 8 shows the annealing temperature dependence of the time dependent dielectric breakdown (TDDB) of nMOS diodes with SiN/HfO<sub>2</sub>/SiON and SiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks for a 10-year lifetime. Both gate stacks have a  $T_{eff}^{inv}$  of 2.6 nm. The figure shows that the SiN/HfO<sub>2</sub>/SiON gate stack has an almost constant  $V_g$  of around 2.6 V when it is annealed at between 950°C and 1050°C. However, the  $V_g$  of the SiN/ HfO<sub>2</sub>/SiO<sub>2</sub> gate stack decreases by 1 V as the annealing temperature increases over the same range. This indicates that the base oxide of SiON has a better thermal stability<sup>29)</sup> than SiO<sub>2</sub>, which may strongly influence reliability. However, as shown in Figure 9, from the point of view of effective mobility, the SiN/HfO<sub>2</sub>/SiON gate stack

Annealing temperature dependence of time dependent dielectric breakdown of nMOS diodes with SiN/HfO<sub>2</sub>/SiON and SiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks.

Figure 9 Effective mobility curves of nMOSFETs with a SiN/HfO<sub>2</sub>/ SiON gate stack and a SiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack.

shows a lower mobility than the SiN/HfO<sub>2</sub>/SiO<sub>2</sub>. This may be caused by a fixed charge that is induced by N-doping into the SiO<sub>2</sub>. It is well known that N incorporation into the SiO<sub>2</sub> lowers the mobility in SiON and SiN gate stacks; therefore, this difference may be due to the presence of nitrogen.

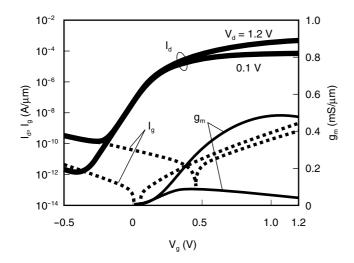

Figure 10 shows the characteristics of an nMOSFET with an optimized SiN/HfO<sub>2</sub>/SiON gate stack. An  $I_{dsat}$  of 357  $\mu$ A/ $\mu$ m at  $L_g$  of 0.35  $\mu$ m was

Characteristics of an nMOSFET with an optimized SiN/ HfO<sub>2</sub>/SiON gate stack. The thick solid lines show  $I_{d}$ -V<sub>g</sub>, thin solid lines show  $g_{m}$ -V<sub>g</sub>, and dotted lines show  $I_{g}$ -V<sub>g</sub>.

obtained with a  $T_{\rm eff}^{\rm inv}$  of 1.7 nm. The gate leakage current was very low, despite the small  $T_{\rm eff}^{\rm inv}$ . An excellent subthreshold swing of 73 mV/decade was also obtained.

## 3.3 Feasibility of using HfO<sub>2</sub> gate dielectric MOSFET in low standby power applications

From the practical point of view, high-k gate dielectrics are expected to be used in low leakage and LSTP applications. In this section, we show the feasibility of a  $HfO_2$  gate dielectric MOSFET for LSTP applications whose  $L_g$  is much lower than has been reported so far.<sup>30)</sup> The  $HfO_2$  thickness in this experiment was 3 nm.

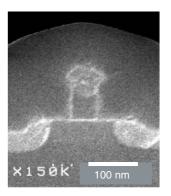

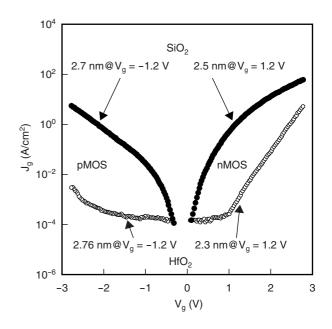

**Figure 11** shows a cross-sectional SEM image of a  $HfO_2$  MOSFET with a 50 nm polysilicon gate and Co-silicide. The extension and pocket implant conditions were varied to facilitate the removal of residual  $HfO_2$  during the wet process. From CV measurements, the gate depletion was suppressed by increasing the activation annealing temperature to 1000°C. The EOT of the  $HfO_2$ MOSFETs was estimated to be 1.4 nm. **Figure 12** compares the  $J_g$ - $V_g$  characteristics of the  $HfO_2$ MOSFETs in the inversion condition with a refer-

#### Figure 11

Cross-sectional SEM image of  $HfO_2$  MOSFET with 50 nm polysilicon gate and Co-silicide contact.

Figure 12

$J_g$ - $V_g$  characteristics of HfO<sub>2</sub> MOSFETs in inversion condition and a reference MOSFET with a SiO<sub>2</sub> gate oxide. RTA was performed at 1025°C.

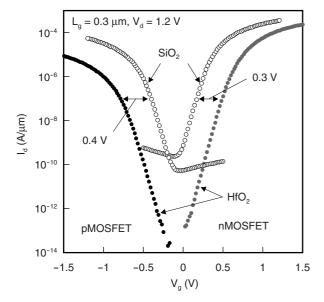

ence MOSFET having a SiO<sub>2</sub> gate oxide whose thickness was nearly equal to that of the HfO<sub>2</sub> MOSFETs. The J<sub>g</sub> of the HfO<sub>2</sub> MOSFETs was decreased by as much as three orders of magnitude due to the increase of permittivity. **Figure 13** compares the I<sub>d</sub>-V<sub>g</sub> characteristics of the HfO<sub>2</sub> MOSFETs with L<sub>g</sub> of 300 nm and a reference MOSFET having the same channel dose. V<sub>th</sub> was defined at an I<sub>d</sub> of 10<sup>-7</sup> A/µm for all samples. The I<sub>d</sub> of the HfO<sub>2</sub> MOSFETs in the off-state (I<sub>off</sub>) is

Figure 13

$I_d$ - $V_g$  characteristics of HfO<sub>2</sub> MOSFETs with  $L_g$  of 300 nm and a reference MOSFET with the same channel dose. RTA was performed at 1025°C.

less than 1 pA/ $\mu$ m, which is 10 000 times lower than that of the SiO<sub>2</sub> reference. The SiO<sub>2</sub> reference has a high I<sub>off</sub> because it has a high gate leakage current. Therefore, the I<sub>off</sub> cannot be suppressed by increasing the threshold voltage.

$V_{\rm th}$  almost stays constant down to  $L_g$  of 50 nm. Although the corresponding subthreshold factor gradually rolls up to 100 mV/decade, short channel effects in the nMOSFETs were fairly well suppressed even when the  $L_g$  was reduced to 50 nm. The subthreshold factors of the pMOSFETs (95 to 100 mV/decade) were slightly larger than those of the nMOSFETS, even at  $L_g$  as high as 0.2  $\mu$ m. This difference can be considered to be due to boron penetration through the HfO<sub>2</sub>. This issue can be improved by introducing a thin SiN layer as discussed in Section 3.2.

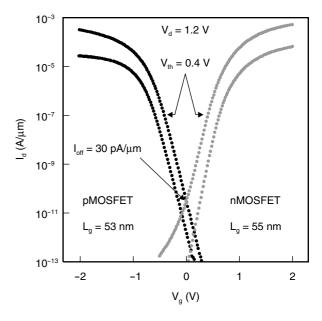

The  $I_d\text{-}V_g$  characteristics of HfO<sub>2</sub> MOSFETs with  $L_g$  of 55 nm are shown in **Figure 14**. The  $V_{\rm th}$  was controlled by adjusting the channel doping concentration. The  $I_{\rm off}$  of 25 pA/µm that was achieved was slightly larger than that shown in Figure 13, because the  $V_{\rm th}$  was decreased by channel doping control and the subthreshold factor was

Figure 14  $I_{d}$ -V<sub>g</sub> characteristics of HfO<sub>2</sub> MOSFETs with L<sub>g</sub> of 55 nm and HfO<sub>2</sub> of 3 nm.

increased. However, the  $I_{off}$  is still small, considering the value of EOT. We observed well-behaved  $I_d$ - $V_d$  characteristics in the HfO\_2 MOSFETs with a small  $L_g$  of 55 nm. An  $I_{dsat}$  of 140 (110)  $\mu$ A/ $\mu$ m and an  $I_{off}$  of 25 (25) pA/ $\mu$ m were obtained at  $V_g = V_d = 1.2$  V. A  $T_{eff}^{inv}$  of 2.3 (2.9) nm and a  $J_g$  of  $2 \times 10^{-4}$  (5  $\times 10^{-4}$ ) A/cm² for n(p)MOSFETs with a 3 nm-thick HfO\_2 layer. Although  $I_{dsat}$  was observed to be relatively small,  $I_{on}/I_{off}$  can be improved by improving the mobility and suppressing boron penetration as discussed in Section 3.2.

#### 3.4 Thermal stability

CVD  $HfO_2$  films tend to crystallize at a fairly low temperature. Since  $Al_2O_3$  has a high thermal stability, Al incorporation into  $HfO_2$  can be considered to increase the thermal stability in addition to increasing the entropy. In this section, we examine the thermal stability of  $Hf_xAl_{1-x}O_y$  using XRD and XTEM.

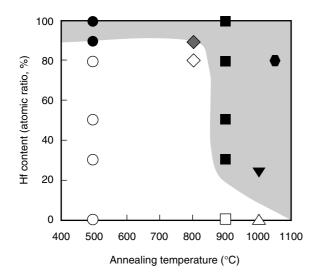

**Figure 15** shows the tendency of crystallization in the range from the as-deposited temperature (500°C) to 1050°C. Although the annealing time and film stack structure are not

Figure 15

Crystallization map of Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub>layers. The x-axis shows the Hf content as the atomic percentage, and the annealing temperature is from the 500°C as-deposited temperature to 1050°C. White symbols indicate the amorphous phase, and black symbols indicate the crystallized phase as judged from XRD and XTEM. The gray diamond indicates an ambiguous phase. Also:

- Circles indicate 10 nm, as-deposited layer.

- Diamonds indicate 4 nm layer annealed at 800°C for 30 s.

- Squares indicate 10 nm layer annealed at 900°C for 30 s.

- Black triangle indicates 10 nm layer annealed at 1000°C for 10 s.

- Hexagon indicates 4 nm layer annealed at 1050°C for 60 s with polysilicon.

- White triangle is quoted from Ref.18).

- All samples except the as-deposited and quoted samples were annealed in N<sub>2</sub> ambient.

unified, the degree of crystallization can be grasped and the hatched area can be considered to be crystallized. Even when the Hf content of x is increased from 0 to 0.8, the  $Hf_xAl_{1-x}O_y$  stays amorphous up to 800°C. Therefore, even an Al incorporation of only about 10% by atomic percentage into  $HfO_2$  increases its thermal stability by 300°C.

We measured the gate leakage current and accumulation capacitance of MOS capacitors with a polysilicon gate and a 4 nm-thick  $Hf_xAl_{1-x}O_y$  ( $0 \le x \le 1$ ) layer. We found that the minimum leakage current and the maximum capacitance was obtained at x = 0.8. This suggests that even a small amount of Al in  $Hf_xAl_{1-x}O_y$  suppresses the crystal-

lization that may cause leakage current and increases the dielectric constant. This in turn suggests that Hf-rich  $Hf_xAl_{1-x}O_y$  combines the thermal-stability advantage of  $Al_2O_3$  and the dielectric-constant advantage of  $HfO_2$ , and is therefore a potential candidate for 65 nm nodes and beyond.

## 4. Summary

We reported on recent progress in high-k gate dielectrics made of  $Al_2O_3$ ,  $HfO_2$ , and  $Hf_xAl_{1-x}O_y$  ( $0 \le x \le 1$ ). Several types of MOSFETs were fabricated with a conventional CMOS process and then evaluated. We obtained the following results:

- 1) We investigated an  $Al_2O_3$  gate stack with and without DMH-doping. A minimum  $D_{it}$  of  $4 \times 10^{10}$  cm<sup>-2</sup>eV<sup>-1</sup> was obtained near the midgap in a DMH-doped  $Al_2O_3$  MOS diode, which is half that obtained in a non-DMH-doped  $Al_2O_3$  MOS diode. Also, DMH-doping into  $Al_2O_3$  provided a mobility enhancement and an increase of  $I_{dsat}$ .

- 2) We found that a top SiN layer greatly helps to suppress  $HfO_2/polysilicon$  reaction and dopant diffusion. The base oxide of the SiON also helps to improve the reliability and thermal stability of the gate stack. We fabricated an nMOSFET with a SiN/HfO<sub>2</sub>/SiON gate stack having a  $T_{eff}^{inv}$  of 1.7 nm that shows an  $I_{dsat}$  of 357  $\mu$ A/ $\mu$ m at  $L_g$  of 0.35  $\mu$ m. This SiN/ HfO<sub>2</sub>/SiON gate stack is a promising technology for realizing ultra-thin, gate stacks in 65 nm nodes and beyond.

- 3) A 55 nm CMOS with a 3 nm  $HfO_2$  gate dielectric was fabricated using a conventional process flow with high-temperature annealing at  $\geq 1000^{\circ}$ C and a cobalt silicide. The  $J_g$ was decreased by more than three orders of magnitude, and a low  $I_{off}$  was obtained. These results show that  $HfO_2$  is very promising for low-standby power applications.

- We investigated the thermal stability of Hf<sub>x</sub>Al<sub>1-x</sub>O<sub>y</sub> by varying the annealing temperature and the Hf content of x. Within the

range  $0 \le x \le 0.8$ ,  $Hf_xAl_{1-x}O_y$  stayed amorphous up to 800°C, which is at least 300°C higher than the corresponding temperature for  $HfO_2$ .

## References

- D. K. Nayak, J. C. Woo, J. S. Park, K. L. Wang, and K. P. MacWilliams: High-Mobility p-Channel Metal-Oxide-Semiconductor Field-Effect Transistor on Strained Si. *Appl. Phys. Lett.*, **62**, 22, p.2853-2855 (1993).

- J. Welser, J. L. Hoyt, and J. F. Gibbons: Electron Mobility Enhancement in Strained-Si N-Type Metal-Oxide-Semiconductor Field-Effect Transistors. *IEEE Electron Device Lett.*, EDL-15, 3, p.100-102 (1994).

- M. Shima, T. Ueno, T. Kumise, H. Shido, Y. Sakuma, and S. Nakamura: <100> Channel Strained-SiGe p-MOSFET with Enhanced Hole Mobility and Lower Parasitic Resistance. Technical Digest of Symposium on VLSI Technology, p.94, 2002.

- B. Yu, H. Wang, A. Joshi, Q. Xiang, E. Ibok, and M.-R. Lin: 15nm Gate Length Planar CMOS Transistor. Technical Digest of IEDM, p.937, 2001.

- 5) M. Togo, K. Watanabe, T. Yamamoto, N. Ikarashi, K. Shiba, T. Tatsumi, H. One, and T. Mogami: Low-Leakage and Highly-Reliable 1.5 nm SiON Gate-Dielectric Using Radical Oxynitridation for Sub-0.1 μm CMOS. Technical Digest of Symposium on VLSI Technology, p.116, 2000.

- 6) N. Kimizuka, K. Yamaguchi, K. Imai, T. Iizuka, C. T. Liu, R. C. Keller, and T. Horiuchi: NBTI Enhancement by Nitrogen Incorporation into Ultrathin Gate Oxide for 0.10-μm Gate CMOS Generation. Technical Digest of Symposium on VLSI Technology, p.92, 2000.

- M. T. Takagi and Y. Toyoshima: Importance of Si-N Atomic Configuration at the Si/Oxynitride Interfaces on the Performance of Scaled MOSFETs. Technical Digest of IEDM, p.575, 1998.

- Y. Momiyama, H. Minakata, and T. Sugii: Ultra-Thin Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> Gate Insulator with TiN Gate Technology for 0.1 μm MOSFETs. Technical Digest of Symposium on VLSI Technology, p.135, 1997.

- D. Park, Q. Lu, T. -J. King, C. Hu, A. Kalnitsky, S. -P. Tay, and C. -C. Cheng: SiON/ Ta2O5/TiN Gate-Stack Transistor with 1.8nm Equivalent SiO<sub>2</sub> Thickness. Technical Digest of IEDM, p.381, 1998.

- K. J. Hubbard and D. G. Schlom: Thermodynamic Stability of Binary Oxides in Contact with Silicon. *J. Mater. Res.*, **11**, 11, p.2757-2775 (1996).

- S. Miyazaki: Photoemission Study of Energy-Band Alignments and Gap-State Distributions for High-k Gate Dielectrics. *J. Vac. Sci. Technol.*, **B19**, 6, p.2212-2216 (2001).

- 12) L. Manchanda, W. H. Lee, J. E. Bower, F. H. Baumann, W. L. Brown, C. J. Case, R. C. Keller, Y. O. Kim, E. J. Laskowski, M. D. Morris, R. L. Opila, P. J. Silverman, T. W. Sorsch, and G. R. Weber: Gate Quality Doped High K Films for CMOS Beyond 100 nm: 3 10nm Al<sub>2</sub>O<sub>3</sub> with Low Leakage and Low Interface States. Technical Digest of IEDM, p.605, 1998.

- J. Robertson: Band Offsets of Wide-Band-Gap Oxides and Implications for Future Electronic Devices. *J. Vac. Sci. Technol.*, **B18**, 3, p.1785-1791 (2000).

- 14) C. Hobbs, L. Dip, K. Reid, D. Gilmer, R. Hegde, T. Ma, B. Taylor, B. Cheng, S. Samavedam, H. Tseng, D. Weddington, F. Huang, D. Farber, M. Schippers, M. Rendon, L. Prabhu, R. Rai, S. Bagchi, J. Conner, S. Backer, F. Dumbuya, J. Locke, D. Workman, and P. Tobin: Sub-Quarter Micron Si-Gate CMOS with ZrO<sub>2</sub> Gate Dielectric. International Symposium on VLSI-TSA, p.204, 2001.

- 15) B. H. Lee, L. Kang, W.-J. Qi, R. Nieh, Y. Jeon,K. Onishi, and J. C. Lee: Ultrathin HafniumOxide with Low Leakage and Excellent Reli-

ability for Alternative Gate Dielectric Application. Technical Digest of IEDM, p.133, 1999.

- P. Alluri, S. Zafar, J. Conner, L. Prabhu, D. Roan, D. Gentile, B. Hradsky, J. Finder, R. Hegde, C. Hobbs, J. Schaeffer, D. Gilmer, H. Tseng, V. Kaushik, B. Y. Nguyen, P. Chu, and P. Tobin: Chemical Vapor Phase Grown High-k Gate Dielectrics. MRS High-k Gate Dielectric Workshop, p.27, 2000.

- 17) C. -L. Liu, Z. X. Jiang, R. I. Hegde, D. D. Sieloff, R. S. Rai, D. C. Gilmer, C. C. Hobbs, P. J. Tobin, and S. Lu: Theoretical and Experimental Investigation of Boron Diffusion in Polycrystalline HfO<sub>2</sub> Films. *Appl. Phys. Lett.*, **81**, 8, p.1441-1443 (2002).

- 18) E. P. Gusev, D. A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Callegari, S. Zafar, P. C. Jamison, D. A. Neumayer, M. Copel, M. A. Gribelyuk, H. Okorn-Schmidt, C. D'Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L-Å. Ragnarsson, P. Ronsheim, K. Rim1, R. J. Fleming, A. Mocuta, and A. Ajmera: Ultrathin High-K Gate Stacks for Advanced CMOS Devices. Technical Digest of IEDM, p.451, 2001.

- A. Shanware, J. McPherson, M. R. Visokay, J. J. Chambers, A. L. P. Rotondaro, H. Bu, M. J. Bevan, R. Khamankar, and L. Colombo: Reliability Evaluation of HfSiON Gate Dielectric Film with 12.8 Å SiO<sub>2</sub> Equivalent Thickness. Technical Digest of IEDM, p.137, 2001.

- 20) Y. Tanida, Y. Tamura, S. Miyagaki, M. Yamaguchi, C. Yoshida, Y. Sugiyama, and H. Tanaka: Effect of In-Situ Nitrogen Doping into MOCVD-Grown A1<sub>2</sub>O<sub>3</sub> to Improve Electrical Characteristics of MOSF'ETs with Polysilicon Gate. Technical Digest of Symposium on VLSI Technology, p.190, 2002.

- H. -J. Cho, C. S. Kang, K. Onishi, S. Gopalan, R. Nieh, R. Choi, E. Dharmarajan, and J. C. Lee: Novel Nitrogen Profile Engineering for Improved TaN/HfO<sub>2</sub>/Si MOSFET Performance. Technical Digest of IEDM, p.655,

2001.

- 22) C. S. Kang, H.-J. Cho, K. Onishi, R. Choi, R. Nieh, S. Goplan, S. Krishnan, and Jack C. Lee: Improved Thermal Stability and Device Performance of Ultra-thin (EOT<10Å) Gate Dielectric MOSFETs by using Hafnium Oxynitride (HfO<sub>x</sub>N<sub>y</sub>). Technical Digest of Symposium on VLSI Technology, p.146, 2002.

- 23) Y. Morisaki, T. Aoyama, Y. Sugita, K. Irino, T. Sugii, and T. Nakamura: Ultra-thin (T<sub>eff</sub><sup>inv</sup> = 1.7 nm) Poly-Si-gated SiN/HfO2/SiON High-k Stack Dielectrics with High Thermal Stability (1050°C). Technical Digest of IEDM, p.861, 2002.

- 24) S. Pidin, Y. Morisaki, Y. Sugita, T. Aoyama, K. Irino, T. Nakamura, and T. Sugii: Low Standby Power CMOS with HfO<sub>2</sub> Gate Oxide for 100-nm Generation. Technical Digest of Symposium on VLSI Technology, p.28, 2002.

- 25) E. H. Nicollian and A. Goetzberger: The Si-SiO<sub>2</sub> Interface-Electrical Properties as Determined by the Metal-Insulator-Silicon Conductance Technique. *Bell Syst. Tech. J.*, 46, 6, p.1055-1133 (1967).

- 26) E. M. Vogel, W. K. Hensen, C. A. Richter, and S. Suehle: Limitations of Conductance to the Measurement of the Interface State Density of MOS Capacitors with Tunneling Gate Dielectrics. *IEEE Trans. Electron Devices*, **ED-47**, 3, p.601-608 (2000).

- S. -I. Saito, K. Torii, M. Hiratani, and T. Onai: Analytical Quantum Mechanical Model for Accumulation Capacitance of MOS Structures. *IEEE Electron Device Lett.*, EDL-23, 6, p.348-350 (2002).

- 28) S. J. Lee, C. H. Lee, C. H. Choi, and D. L. Kwong: Time-Dependent Dielectric Breakdown in poly-Si CVD HfO<sub>2</sub> Gate Stack. Proc. of Int. Reliability Phys. Symp., p.409, 2002.

- 29) R. Choi, C. S. Kang, B. H. Lee, K. Onishi, R. Nieh, S. Gopalan, E. Dharmarajan, and J. C. Lee: High-Quality Ultra-Thin HfO<sub>2</sub> Gate Dielectric MOSFETs with TaN Electrode and

Nitridation Surface Preparation. Technical Digest of Symposium on VLSI Technology, p.31, 2001.

30) C. Hobbs, H. Tseng, K. Reid, B. Taylor, L. Dip,L. Hebert, R. Garcia, R. Hegde, J. Grant,D. Gilmer, A. Franke, V. Dhandapani,

Yoshihiro Sugiyama received the B.S., M.S., and Ph.D. degrees in Electronic Engineering from Tohoku University, Sendai, Japan in 1982, 1985, and 2000, respectively. He joined Fujitsu Laboratories Ltd., Atsugi, Japan in 1985. From 1985 to 2000, he was engaged in research of resonant tunneling devices, ultra-fast spectroscopy in low dimensional systems, and quantum dot optical memory. His recent interests include

SiGeC materials and high-k gate dielectrics. Dr. Sugiyama is a member of the Japan Society of Applied Physics, and the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan. He received a Paper Award from the IEICE of Japan in 1993.

Digest of IEDM, p.651, 2001.

Yusuke Morisaki received the B.S. and M.S. degrees in Applied Chemistry from the University of Tokyo, Tokyo, Japan in 1996 and 1998, respectively. He joined Fujitsu Laboratories Ltd., Atsugi, Japan in 1998, where he has been engaged in research and development of gate dielectrics for MOSFETs. He is a member of the Japan Society of Applied Physics.

M. Azrak, L. Prabhu, R. Rai, S. Bagchi,

J. Conner, S. Backer, F. Dumbuya, B.

Nguyen, and P. Tobin: 80 nm Poly-Si Gate

CMOS with HfO<sub>2</sub> Gate Dielectric. Technical

Sergey Pidin received the Ph.D. degree in Electronics Engineering from Tohoku University, Sendai, Japan in 1998. He joined Fujitsu Laboratories Ltd., Atsugi, Japan in 1998. He is currently involved in CMOS device development for 90 nm technology nodes at the Fujitsu Akiruno Development Center. He is a member of the Japan Society of Applied Physics.