# **Process and Device Technologies for** High-Performance 0.13 µm FCRAM

🕑 Yasuo Nara 🛛 🔵 Shunji Nakamura 🔍 Tetsu Tanaka 🔍 Koichi Hashimoto Daisuke Matsunaga

(Manuscript received February 3, 2003)

We have developed a novel integration scheme for FCRAM cores using a high-dielectric capacitor technology and low-temperature process technology so we can scale the design rule towards 0.13 µm and improve device performance. Ru/Ta<sub>2</sub>O<sub>4</sub>/Ru capacitor technology, which can provide a dielectric constant as high as 70 and an SiO<sub>2</sub>-equivalent thickness of 0.7 nm, has been established combined with a robust cylinder electrode fabrication process using a TiN liner. A self-aligned storage-node contact fabrication process with low-temperature (600°C) Si<sub>3</sub>N<sub>4</sub> deposition improves the transistor performance by more than 10%. These technologies have been applied to a 0.13 µm-generation device, and the functionality of this device has been confirmed. Also, this paper demonstrates the scalability of these technologies to the 0.1 µm generation.

### 1. Introduction

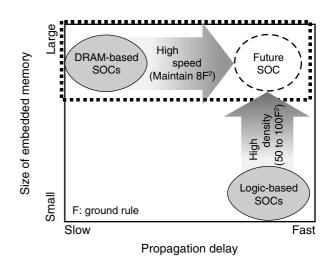

Demand for System-on-a-Chip (SOC) has increased recently for use in many products such as digital AV equipment and mobile phones.<sup>1)-4)</sup> SOC requires the implementation of both high-performance logic and high-density embedded memory, and these requirements will be accelerated for future systems as shown in **Figure 1**. In order to satisfy these requirements, scaling of the design rule and improvement of device performance (high-speed operation) combined with the integration of high-density memory in CMOS (Complementary Metal-Oxide-Semiconductor) technology should be simultaneously achieved. Fast Cycle RAM (FCRAM)<sup>5)</sup> is one of the promising devices used for such systems, because high-density memory is implemented by using DRAM (Dynamic Random Access Memory) technology and its architecture is expected to provide high-speed operation.

This paper describes two key technologies developed for the DRAM core of FCRAM that make it possible to scale down design rule to 0.13  $\mu m$  and improve device performance. The first of these is a new capacitor technology that meets the strong need to combine a high dielectric constant

Figure 1

Development scenario toward future System-on-a-Chip (SOC). Future SOC requires the implementation of both high-performance (high-speed) and high-density embedded memory. Approach from DRAM-based SOC, which is easy to integrate with large-size memory requires improvement of operation speed.

material with a three-dimensional electrode structure.<sup>6)-9)</sup> The new technology<sup>10)</sup> uses a Metal/ Insulator/Metal (MIM) capacitor with highly stable cylindrical electrodes and allows the cell size to be further reduced while maintaining the cell capacitance at around 30 fF/cell. The second key technology reduces the process temperature to prevent a degradation of MOSFET (Metal Oxide Semiconductor Field Effect Transistor) performance. A low-temperature  $Si_3N_4$  deposition process has been integrated into a self-aligned storage-node contact process,<sup>11)</sup> and a greater than 10% improvement of transistor performance has been achieved.<sup>12)</sup> These technologies have been fully integrated in a 0.13  $\mu$ m test device and their potential usefulness has been confirmed. This paper also describes the scalability of these technologies toward the 0.1  $\mu m$  generation.

# Ru/Ta<sub>2</sub>O<sub>5</sub>/Ru capacitor with liner-supported cylinder (LSC) technology

In the conventional capacitor technology for a DRAM core, the combination of a silicon oxynitride dielectric film and a doped poly-silicon electrode material has been widely utilized. Since the design rule has been scaled down, there has been a wide demand for a capacitor technology that uses a high dielectric constant material and a three-dimensional electrode capacitor.<sup>6)-9)</sup> One of the most promising capacitor structures with a high dielectric constant is the metal/Ta<sub>2</sub>O<sub>5</sub>/metal capacitor (MIM-Ta<sub>2</sub>O<sub>5</sub> capacitor) with Ru metal electrodes.<sup>13),14)</sup>

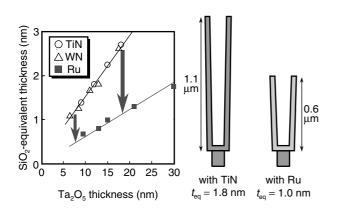

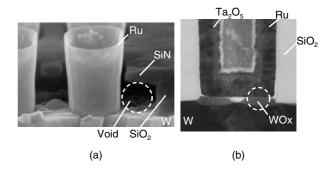

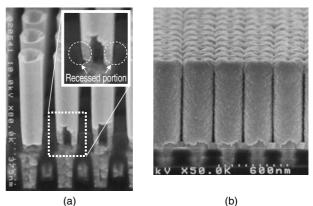

When Ru is used for the top and bottom metal electrodes of an MIM-Ta<sub>2</sub>O<sub>5</sub> capacitor, this system displays better performance than when TiN and WN electrodes are used, with a dielectric constant of around 70 and an SiO<sub>2</sub>-equivalent thickness of 0.7 nm (Figure 2).<sup>15)-18)</sup> However, until now, stable formation of cylindrical bottom electrodes with Ru has been impossible because of two reasons. Firstly, the adhesion of Ru and SiO<sub>2</sub> is so poor that wet-etchant penetrates along the interface during the sacrificial-SiO<sub>2</sub> strip process and severely attacks the stopper-Si<sub>3</sub>N<sub>4</sub> **(Figure 3 (a))**, causing the collapse of the cylinder electrodes. Secondly, oxygen can penetrate the Ru film so easily that the surface of the contact plug material would be oxidized in the oxidizing ambient of Ta<sub>2</sub>O<sub>5</sub> formation, causing contact failures {Figure 3 (b)}.

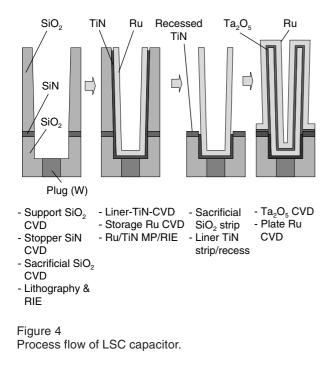

These problems were overcome by using the Liner-Supported Cylinder (LSC) technology with a TiN-liner formed in the shape of a calyx.<sup>10</sup> **Figure 4** shows the process flow of LSC tech-

Figure 2

Impact of electrode material selection in metal/Ta<sub>2</sub>O<sub>5</sub>/metal capacitor. By using Ru electrodes, SiO<sub>2</sub> equivalent thickness can be reduced and lower electrodes can be expected.

#### Figure 3

Difficulties with Ru cylinder electrodes. (a) Adhesion of Ru and SiO<sub>2</sub> is so poor that wet-etchant penetrates along the interface during sacrificial-SiO<sub>2</sub> strip process and voids and cylinder collapses occur. (b) Oxygen easily penetrates through Ru electrode; therefore, plug W is oxidized, causing a contact problem.

nology. TiN, Ru, and Ta<sub>2</sub>O<sub>5</sub> are deposited by CVD (Chemical Vapor Deposition) using TiCl<sub>4</sub>,  $Ru(EtCp)_2$ , and  $Ta(OC_2H_5)_5$  as the source materials, respectively. All processes are performed at a temperature below 600°C. The key processes of this technology are the formation of the thin TiN liner and its removal by well-controlled wet etching with diluted  $H_2SO_4/H_2O_2$ . After this wet etching, the liner TiN is slightly recessed below the surface of the support-SiO<sub>2</sub> to the designed depth so that the electrical characteristics of the capacitor are not affected. The TiN-liner acts both as an adhesion layer between the Ru and SiO<sub>2</sub> and as an oxidization barrier during Ta<sub>2</sub>O<sub>5</sub> formation. Figure 5 shows a cross-sectional view of a sample fabricated with a 0.13 µm ground rule and 550 nm-high cylinder capacitors that were successfully built without any collapses.

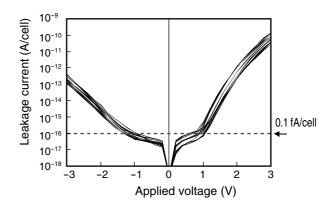

**Figure 6** shows the I-V characteristics of the LSC-Ta<sub>2</sub>O<sub>5</sub> capacitor. The leakage current of this capacitor is below 0.1 fA/cell over the range of -0.8 to 0.8 V, which is low enough for DRAM applications. The LSC technology was applied to a fully integrated 0.13 µm test device combined with other key technologies such as optimized

(

Figure 5

Cross-sectional view of LSC capacitor fabricated with 0.13  $\mu m$  rule. (a) Photograph after liner TiN strip and recess process. (b) Photograph after plate electrode formation.

Figure 6 Leakage current and applied voltage characteristics of LSC capacitor.

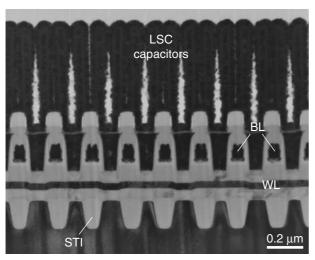

KrF (Krypton Fluoride) excimer laser lithography,<sup>19)</sup> a poly-metal gate transistor,<sup>20),21)</sup> and a dual-damascene bit-line process.<sup>11)</sup> A TEM image of the fully integrated device is shown in **Figure 7**. The DRAM functionality was confirmed on 256 kbit test devices.

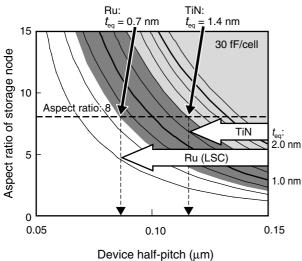

Next, we will discuss the scalability of LSC capacitor technology. To maintain a capacitance of 30 fF/cell, we plotted the required aspect ratios of the storage-node electrode as a function of the device design rule with various  $SiO_2$ -equivalent thicknesses of  $Ta_2O_5$  (**Figure 8**). The realistic aspect ratio was assumed to be less than 8,

considering the via-hole opening and filling by the sides of the capacitors. Compared with other bottom electrode materials such as TiN, Ru with the LSC technology is much better able to bring out

BL: Bit line WL: Word line STI: Shallow trench isolation

### Figure 7

Cross-sectional TEM image of a fully integrated 0.13 µm test DRAM.

### Figure 8

Scalability of LSC capacitor. Aspect ratio of the storage node is plotted as a function of device half-pitch (design rule). Required capacitance and realistic aspect ratio of storage node are assumed to be 30 fF/cell and 8, respectively. LSC technology with Ru electrodes will be scaled to below 0.1 µm generation.

2.0 nm

Bit line direction Word line direction Ru/Ta<sub>2</sub>O<sub>5</sub>/Ru MIM cylinder capacitor Bit line Self aligned contact W-polymetal wordline 100 nm

Figure 9

Cross-sectional images of device scaled down to 0.11 µm design rule.

the best Ta<sub>2</sub>O<sub>5</sub> performance, resulting in a scalability towards sub-0.10 µm generations. A crosssectional view of a device scaled down to a 0.11 µm design rule is shown in Figure 9, indicating that scaling is feasible.

# 3. Impact of thermal budget reduction on MOSFET performance and integration with low-temperature process

The high-temperature process after MOSFET fabrication leads to impurity deactivation in the source and drain regions, which eventually degrades MOSFET performance by reducing the drain current. Conventionally, the temperature has been highest in the capacitor fabrication process and the CVD Si<sub>3</sub>N<sub>4</sub> deposition process used in a self-aligned contact (SAC) formation. These high-temperature processes should be avoided in the processes for high-performance SOCs. The LSC capacitor technology presented in the previous chapter has lowered the process temperature to below 600°C, which is more than 100 to 200°C below that of the conventional capacitor process. The remaining high-temperature process is Si<sub>3</sub>N<sub>4</sub> deposition.

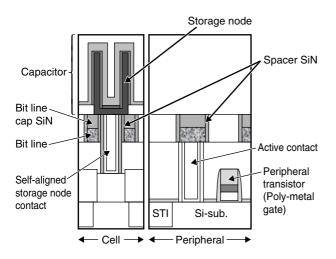

Figure 10 shows a schematic drawing of a DRAM structure after capacitor formation. A tungsten poly-metal gate and tri-layer barrier metal technology for a tungsten contact<sup>11</sup> were employed. To create a self-aligned storage node contact, CVD-Si<sub>3</sub>N<sub>4</sub> films with good step-coverage were used as an etching stopper for the bit-line cap and sidewalls. Although use of CVD-Si<sub>3</sub>N<sub>4</sub> is attractive because of its high step-coverage, its high-temperature and long-lasting thermal sequence drastically increases the thermal budget after final activation and degrades device performance. We overcame this problem by applying a low-temperature CVD-Si<sub>3</sub>N<sub>4</sub> technology together with a hexachlorodisilane (HCD) gas source<sup>22)</sup> instead of the conventional dichlorosilane (DCS) source. This approach lowered the process temperature from more than 700°C to less than 650°C. Table 1 compares the thermal budgets for different CVD-Si<sub>3</sub>N<sub>4</sub> deposition processes. By using HCD-Si $_3N_4$ , we can lower the process temperature to between 600 and 650°C without extending the treatment time.

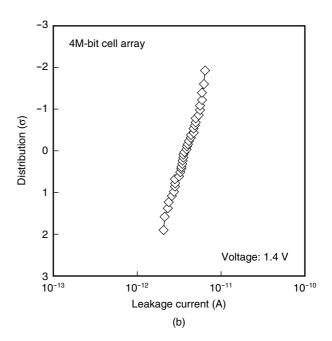

**Figure 11** shows the leakage current distribution between the bit line (BL) and the storage node (SN) as measured using a 4M-bit test vehi-

Figure 10

Schematic of DRAM structure after capacitor formation.

### Table 1

Comparison of thermal budgets for different CVD-Si $_3N_4$  deposition processes.

|                       | DCS-Si <sub>3</sub> N <sub>4</sub> | HCD-Si <sub>3</sub> N <sub>4</sub> |     |

|-----------------------|------------------------------------|------------------------------------|-----|

| Growth temp.<br>(°C)  | 700                                | 650                                | 600 |

| Process time<br>(min) | 541                                | 206                                | 304 |

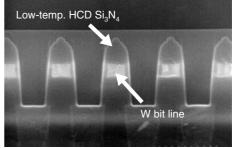

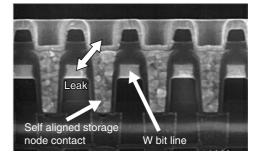

cle over all parts of a wafer to which the low-temperature HCD-Si $_3N_4$  was applied as an SAC etching stopper. No SN-BL shorts caused by the

After contact etching

After contact formation

### Figure 11

(a) Photograph of self-aligned storage node contact formation using low-temperature HCD-Si<sub>3</sub>N<sub>4</sub>. (b) Distribution of leakage current between bit line and storage node as measured by 4M-bit cell array monitor.

Figure 12

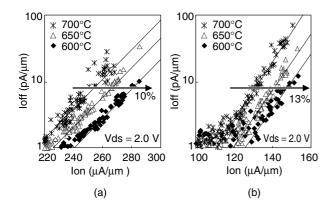

Relation between Ion and Ioff for different thermal process temperatures. More than 10% increase of Ion was observed for both the NMOSFET (a) and PMOSFET (b) at a fixed Ioff.

SAC process were observed, also indicating the adequate selectivity of the  $HCD-Si_3N_4$  film during SAC etching.

The impact of lowering the process temperature was clarified by measuring peripheral MOSFET devices with a 5.2 nm-thick gate dielectric. Figure 12 shows the Ion vs. Ioff characteristics for NMOSFET and PMOSFET devices at Vds = 2.0 V under different thermal process temperatures. In this figure, a process temperature of 600°C indicates that the maximum process temperature is limited by the MIM-Ta<sub>2</sub>O<sub>5</sub> capacitor fabrication process. Also, temperatures above 600°C indicate that the temperature is highest in the CVD-Si $_{3}N_{4}$  deposition process. It is clear that lowering the process temperature has a strong impact on performance. By using 600°C as the process temperature, the drive currents of the NMOSFET and PMOSFET devices at Ioff = 10 pA/µm were improved, respectively, by about 10% and 13%, compared to those of the conventional Si<sub>3</sub>N<sub>4</sub> process at 700°C. This improvement seems mostly due to the reduction of dopant deactivation.

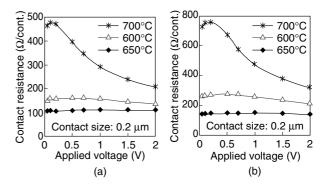

**Figure 13** shows the active contact resistance as a function of applied voltage. In the 700°C process, the contact resistance to the  $N^+$  and  $P^+$ diffusions increased drastically as the applied

Figure 13

Active  $N^+$  (a) and  $P^+$  (b) contact resistance as a function of applied voltage for different process temperatures. By reducing the process temperature, not only the contact resistance but also the non-linearity is improved.

voltage was decreased; that is, these contacts show strong non-linear characteristics even though a thermally stable metal-contact process was used.<sup>4)</sup> This non-linearity sometimes became a serious problem in circuit design. The non-linear characteristics originate from a low active-dopant concentration at the surface of the N<sup>+</sup> and P<sup>+</sup> diffusions. By lowering the process temperature from 700°C to below 600°C, we significantly improved not only the contact resistance but also the ohmic characteristics of the contacts, resulting in less deterioration of transistor performance. The sheet resistances of N<sup>+</sup> and P<sup>+</sup> diffusions also indicate less dopant deactivation when a lowtemperature process is used.

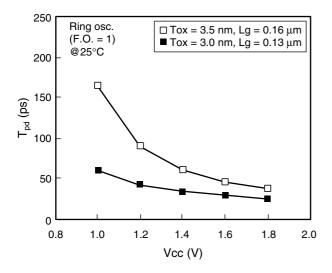

In order to evaluate circuit performance for a low-temperature nitride process, we measured the propagation delay time ( $T_{pd}$ ) of an inverter ring oscillator. A time of 125 ps was obtained for  $T_{pd}$  at a fan-out of 3, and this value meets the device target. We also checked the scalability of this low-temperature process to next-generation devices, which we assume will have a 0.11 µm design rule, by simulating the propagation delay time (**Figure 14**). In the next generation, we assume that the gate length (Lg) and gate oxide thickness (Tox) will be scaled down and the supply voltage (Vcc) will be reduced. Even if we reduce the supply voltage to 1.2 V, a propagation delay time of

Figure 14

Simulated propagation delay time ( $T_{pd}$ ) for scaled design rule. Gate length was scaled to 0.13 µm, and gate oxide thickness was scaled to 3.0 nm.

45 ps can be obtained at a fan-out of 1. This suggests that the technology presented here will also be usable in the next generation and is promising for device scaling.

# 4. Conclusion

This paper described some key technologies for a 0.13  $\mu$ m-rule FCRAM core with high-performance MOSFET characteristics. A newly developed LSC capacitor technology enables us to fabricate robust Ru/Ta<sub>2</sub>O<sub>5</sub>/Ru cylinder capacitors at low temperature. The impact of lower process temperatures on device performance was also clarified. By applying a low-temperature Si<sub>3</sub>N<sub>4</sub> deposition process to a self-aligned contact process, deterioration of peripheral MOSFET device performance was effectively suppressed. Furthermore, the scalability of these technologies to the 0.1  $\mu$ m era was also demonstrated. This technology is a promising candidate for application in future SOC fabrication.

### Acknowledgements

This work was performed by a joint development project (YBA/Yokohama Bay Alliance) between Toshiba Corporation, Winbond Electronics Corporation, and Fujitsu Limited. The authors wish to thank all the engineers of this project for their great contribution to this work. The authors would like to specially acknowledge Drs. K. Maeguchi, T. Kondo, A. Nitayama, K. Hieda, Y. Kohyama, and T. Hamamoto of Toshiba Corporation Semiconductor Company; H. H. Tsai, H. C. Chen, B. R. Sheu, and C. M. Shiah of Winbond Electronics Corporation; and T. Ito of Fujitsu Laboratories Ltd. for their support and contributions.

## References

- D. D. Buss: Technology in the Internet age. IEEE International Solid-State Circuits Conference, Digest of Technical Papers, 1, p.18-21 (2002).

- Y. Mochida, T. Takano, and H. Gambe: Future directions and technology requirements of wireless communications. International Electron Devices Meeting, Technical Digest, p.1.3.1-1.3.8 (2001).

- S. Kohyama: SoC solutions and technologies for digital hypermedia platform. International Electron Devices Meeting, Technical Digest, p.8-13 (1999).

- Y. Kushiki: Digital consumer electronics evolution in the multimedia and network age. Symposium on VLSI Technology, Digest of Technical Papers, p.1-4 (1999).

- Y. Sato, T. Suzuki, T. Aikawa, S. Fujioka, W. Fujieda, H. Kobayashi, H. Ikeda, T. Nagasawa, A. Funyu, Y. Fuji, K. Kawasaki, M. Yamazaki, and M. Taguchi: Fast cycle RAM (FCRAM); a 20-ns random row access, pipe-lined operating DRAM. Symposium on VLSI Circuits, Digest of Technical Papers, p.22-25 (1998).

- Y. K. Park, C. H. Cho, K. H. Lee, B. H. Roh, Y. S. Ahn, S. H. Lee, J. H. Oh, J. G. Lee, D. H. Kwak, S. H. Shin, J. S. Bae, S. B. Kim, J. K. Lee, J. Y. Lee, M. S. Kim, J. W. Lee, D. J. Lee, S. H. Hong, D. I. Bae, Y. S. Chun, S. H. Park, C. J. Yun, T. Y. Chung, and

Kinam Kim: Highly Manufacturable 90 nm DRAM Technology. International Electron Devices Meeting, Technical Digest, p.819 (2002).

- K. Hieda, K. Eguchi, J. Nakahira, M. Kiyotoshi, M. Nakabayashi, H. Tomita, M. Izuha, T. Aoyama, S. Niwa, K. Tsunoda, S. Yamazaki, J. Lin, A. Shimada, K. Nakamura, T. Kubota, M. Asano, K. Hosaka, Y. Fukuzumi, Y. Ishibashi, and Y. Kohyama: Low temperature (Ba,Sr) TiO<sub>3</sub> capacitor process integration (LTB) technology for gigabit scaled DRAMs. International Electron Devices Meeting, Technical Digest, p.789-792 (1999).

- K. Hieda, K. Eguchi, N. Fukushima, T. Aoyama, K. Natori, M. Kiyotoshi, S. Yamazaki, M. Izuha, S. Niwa, Y. Fukuzumi, Y. Ishibashi, Y. Kohyama, T. Arikado, and K. Okumura: All perovskite capacitor (APEC) technology for (Ba,Sr) TiO<sub>3</sub> capacitor scaling toward 0.10 μm stacked DRAMs. International Electron Devices Meeting, Technical Digest, p.807-810 (1998).

- C. M. Chu, M. Kiyotoshi, S. Niwa, J. Nakahira, K. Eguchi, S. Yamazaki, K. Tsunoda, M. Fukuda, T. Suzuki, M. Nakabayashi, H. Tomita, C. M. Shiah, D. Matsunaga, and K. Hieda: Cylindrical Ru-SrTiO<sub>3</sub>-Ru capacitor technology for 0.11 μm generation DRAMs. Symposium on VLSI Technology, Digest of Technical Papers, p.43-44 (2001).

- 10) Y. Fukuzumi, T. Suzuki, A. Sato, Y. Ishibashi, A. Hatada, K. Nakamura, K. Tsunoda, M. Fukuda, J. Lin, M. Nakabayashi, H. Minakata, A. Shimada, T. Kurahashi, H. Tomita, D. Matsunaga, K. Hieda, K. Hashimoto, S. Nakamura, and Y. Kohyama: Liner-supported cylinder (LSC) technology to realize Ru/Ta<sub>2</sub>O<sub>5</sub>/Ru capacitor for future DRAMs. International Electron Devices Meeting, IEDM Technical Digest, p.793-796 (2000).

- T. Miyashita, H. Nitta, H. Nomura, K. Nakajima, A. Sakata, T. Mizutani, H. Minakata, M. Tanaka, H. Tomita,

T. Kurahashi, Y. Watanabe, T. Kubota, A. Hatada, K. Hosaka, K. Hashimoto, and Y. Kohyama: A novel bit-line process using poly-Si masked dual-damascene (PMDD) for 0.13 μm DRAMs and beyond. International Electron Devices Meeting, IEDM Technical Digest, p.361-364 (2000).

- 12) E. Yoshida, T. Miyashita, H. Nitta, M. Tanaka, K. Ishii, Y. Akasaka, P. H. Chou, K. Hashimoto, Y. Kohyama, T. Tanaka, and Y. Nara: Impact of Thermal Budget Reduction on MOSFET Performance to Achieve High-speed and High-density DRAM-based System LSI. Extended Abstract of the 2002 International Conference on Solid State Devices and Materials, p.732-733 (2002).

- 13) W. D. Kim, J. H. Joo, Y. K. Jeong, S. J. Won, S. Y. Park, S. C. Lee, C. Y. Yoo, S. T. Kim, and J. T. Moon: Development of CVD-Ru/Ta<sub>2</sub>O<sub>5</sub>/ CVD-Ru capacitor with concave structure for multigigabit-scale DRAM generation. International Electron Devices Meeting, Technical Digest, p.12.1.1-12.1.4 (2001).

- 14) S. J. Won, W. D. Kim, C. Y. Yoo, S. T. Kim, Y. W. Park, J. T. Moon, and M. Y. Lee: Conformal CVD-ruthenium process for MIM capacitor in giga-bit DRAMs. International Electron Devices Meeting, Technical Digest, p.789-792 (2000).

- 15) T. Aoyama, S. Yamazaki, and K. Imai: Ultrathin  $Ta_2O_5$  Film Capacitor with Ru Bottom Electrode. *Journal of Electrochemical Society*, **145**, 8, p.2961-2963 (1998).

- 16) J. W. Kim, S. D. Nam, S. H. Lee, S. J. Won, W. D. Kim, C. Y. Yoo, Y. W. Park, S. I. Lee, and M. Y. Lee: Development of Ru/Ta<sub>2</sub>O<sub>5</sub>/Ru capacitor technology for giga-scale DRAMs. International Electron Devices Meeting, Technical Digest, p.793-796 (1999).

- S. Kamiyama, J. M. Drynan, Y. Takaishi, and K. Koyama: Highly reliable MIM capacitor technology using low pressure CVD-WN cylinder storage-node for 0.12 μm-scale embedded DRAM. Symposium on VLSI

Technology, Digest of Technical Papers, p.39-40 (1999).

- 18) W. D. Kim, J. W. Kim, S. J. Won, S. D. Nam, B. Y. Nam, C. Y. Yoo, Y. W. Park, S. I. Lee, and M. Y. Lee: Development of CVD-Ru/ Ta<sub>2</sub>O<sub>5</sub>/CVD-TiN capacitor for multigigabitscale DRAM generation. Symposium on VLSI Technology, Digest of Technical Papers, p.100-101 (2000).

- S. Inoue, M. Asano, K. Hosaka, T. Sutani, T. Azuma, D. Kawamura, M. Kobayashi, S. Miyoshi, H. Kanemitsu, S. Tanaka, T. Kotani, Y. Tabata, K. Tsuchida, Y. Kohyama, and E. Kawamura: Level-specific strategy of KrF microlithography for 130 nm DRAMs. International Electron Devices Meeting, Technical Digest, p.809-812 (1999).

- 20) F. Ohtake, Y. Akasaka, A. Murakoshi,

K. Suguro, and T. Nakanishi: A thin amorphous silicon buffer process for suppression of W polymetal gate depletion in PMOS. Symposium on VLSI Technology, Digest of Technical Papers, p.74-75 (2000).

- 21) M. Tanaka, S. Saida, F. Inoue, M. Kojima, T. Nakanishi, K. Suguro, and Y. Tsunashima: Realization of high performance dual gate DRAMs without boron penetration by application of tetrachlorosilane silicon nitride films. Symposium on VLSI Technology, Digest of Technical Papers, p.123-124 (2001).

- 22) M. Tanaka, S. Saida, T. Iijima, and Y. Tsunashima: Low-k SiN film for Cu interconnects integration fabricated by ultra low temperature thermal CVD. Symposium on VLSI Technology, Digest of Technical Papers, p.47-48 (1999).

Yasuo Nara received the B.S., M.S., and Ph.D. degrees in Physical Electronics from Tokyo Institute of Technology, Tokyo, Japan in 1980, 1982, and 1985, respectively. He joined Fujitsu Laboratories Ltd., Atsugi, Japan in 1985, where he has been engaged in research and development of CMOS process and device technologies. From 1998 to 2001, he was a project manager in the Fujitsu-Toshiba-Winbond DRAM devel-

opment project. He is a member of the IEEE Electron Devices Society, the IEEE Solid-State Circuits Society, and the Japan Society of Applied Physics.

Koichi Hashimoto received the B.S. and M.S. degrees in Chemical Energy Engineering from the University of Tokyo, Tokyo, Japan in 1983 and 1985, respectively. He joined Fujitsu Ltd., Kawasaki, Japan in 1985, where he has been engaged in research and development of ULSI processes and devices. He received the Outstanding Achievement Award from the International Symposium on Plasma Process Induced Damage in 1999.

Shunji Nakamura received the M.S. degree in Physics from Chiba University, Chiba, Japan in 1982. He joined Fujitsu Ltd., Kawasaki, Japan in 1982, where he was engaged in research and development of high-speed bipolar LSIs for mainframe computers. In 1993 he transferred to Fujitsu Laboratories Ltd., Atsugi, Japan, where he has been engaged in research and development of low-power and high-speed CMOS devices.

Daisuke Matsunaga received the B.S. and M.S. degrees in Physics from Sophia University, Tokyo, Japan in 1980 and 1982, respectively. He joined Fujitsu Ltd., Kawasaki, Japan in 1982, where since 1998 he has been engaged in research and development of dry etching processes. From 1998 to 2001, he was a process group manager in the Fujitsu-Toshiba-Winbond DRAM development project of the Yokohama Toshiba Micro Electronics Center.

Tetsu Tanaka received the B.S., M.S., and Ph.D. degrees in Electronic Engineering from Tohoku University, Sendai, Japan in 1987, 1990, and 2003, respectively. He joined Fujitsu Laboratories Ltd., Atsugi, Japan in 1990, where he has been engaged in research and development of scaled MOS devices including SOI devices. From 1994 to 1995, he was a Visiting Industrial Fellow at the University of California, Ber-

keley, where he studied the device modeling of MOSFETs. He is a member of the IEEE Electron Devices Society and the IEEE Solid-State Circuits Society.