# 高性能・低電力LTE対応ベースバンド LSI向けベクトルプロセッサ

## High-Performance and Low-Power Vector Processor for LTE Baseband LSI

● 葛 毅 ● 伴野 充 ● 伊藤真紀子 ● 廣瀬佳生

### あらまし

携帯端末の通信速度はLTE(Long Term Evolution)などの通信方式によりどんどん速くなってきており、それを送受信するベースバンドLSIの処理性能の向上が求められている。更に従来の第2世代、第3世代の通信方式も扱えるように、複数の通信方式への対応も必要となっている。これに対して、それぞれの通信方式の回路をLSIにそのまま搭載すると、回路面積が大きくなるため、ソフトウェアで通信方式を切り替えるソフトウェア無線(SDR: Software Defined Radio)による実現を進めてきた。このように携帯端末向けの無線信号処理をソフトウェアで行うには、高性能で低電力なDSP(Digital Signal Processor: デジタル信号処理に特化したマイクロプロセッサ)を開発することが課題となる。今回、低消費電力とアプリケーション開発でメリットのあるベクトル型スーパーコンピュータと同じアーキテクチャーをDSPに採用することにした。組込み向けに小型化の改良を加えることにより、250 MHz動作で12 GOPS(1秒間に120億個のデータ処理が可能)というピーク演算性能と、28 nmプロセス技術を用いたチップで平均30 mWという低消費電力を実現した。

本稿では、今回開発したベクトルプロセッサについて紹介する。

### Abstract

Recently, the transmission rate for handheld devices has been increasing by Long Term Evolution (LTE), and baseband LSI has come to need a higher performance. In addition, handheld devices will use the second- and third-generation communication method, so a baseband LSI will need to handle multiple communication methods. Because implementing all communication circuits results in a large area, we have been developing Software Defined Radio (SDR), which switches each communication method with software. To implement SDR for handheld devices, a high-performance and low-power Digital Signal Processor (DSP) is needed. We have developed a DSP which inherits the architecture of vector supercomputers, and the architecture has advantages of a low power consumption and application developments. We have downsized the vector architecture for embedded systems. The peak performance is 12 GOPS at 250 MHz, and the power consumption is relatively low at 30 mW for 28 nm process technology on average. This paper presents the vector processor that we developed.

## まえがき

近年, LTE (Long Term Evolution) が携帯端末の無線通信方式として主流となってきている。LTEのベースバンド処理は演算量が非常に多いことが知られている。加えて携帯端末向けLSIでは低電力かつ小面積が要求される。また、携帯端末ではHSPA+ (High Speed Packet Access Plus) など従来の無線方式も併存するため、複数の無線通信方式にソフトウェアで対応可能なソフトウェア無線 (SDR: Software Defined Radio) を実現することを進めた。SDR化により、回路を共用することで低コスト化でき、仕様変更や機能追加にも柔軟に対応できる。特に端末向けでは消費電力の都合からむやみにプログラマビリティだけを追求することはできず、消費電力や回路面積とのバランスを取る必要がある。富士通では、以上を踏まえたSDRベースバンドLSIを開発した<sup>(1)</sup>。

LTEの処理は、基地局の探索 (SEA: searcher), 復調 (DEM: demodulator), 復号 (DEC: decoder), 符号化 (COD: coder), 変調 (MOD: modulator) の五つに分類できる。ベースバンドLSI開発に当たり、必要以上の回路面積や消費電力を増加させないように、ベースバンド処理の中でもプログラマビリティが必要なDSP (Digital Signal Processor: デジタル信号処理に特化したマイクロプロセッサ) が適する処理と、ハードウェアアクセラレーターが適する処理 (例えば、DECのターボ復号処理) を大別している。

本稿ではこのDSPとして今回開発したベクトルプロセッサについて紹介する<sup>(2)</sup>。基本アーキテクチャーにはベクトル型スーパーコンピュータの方式を採用しており、携帯端末向けの要求を満たす処理能力と低消費電力化を実現している。なお、本ベクトルプロセッサはSEA, DEM, MODを処理対象としている。

まず最初に次章では、DSPの基本アーキテクチャーとしてベクトル構成を採用した経緯について述べ、次に本ベクトルプロセッサの説明をする。最後にベクトル方式をほかのSIMDアーキテクチャーと比較して議論する。

## 基本アーキテクチャーの方針

演算量が非常に多い無線信号処理のソフトウェア処理を考える場合、演算処理を並列に実行できる部分の把握が必要である。プログラムの並列性は、一般に、①データレベル並列性、②命令レベル並列性、③スレッドレベル並列性に分類でき、① $\subset$ ② $\subset$ ③という包含関係にあり<sup>(3), (4)</sup>、データレベルの並列性があるものはスレッドレベルでの並列処理も可能である。ただし処理に必要なハードウェア量と処理オーバーヘッドは① $<$ ② $<$ ③順に大きくなるため、より小さな並列性はそれに適した装置で行わせた方が良い。例えば、スレッド並列で処理できるマルチコアプロセッサは広い並列性に対処できるが、回路面積全体に占める演算器の割合が低く、面積あたりの演算性能が低い。このため処理のオーバーヘッドも大きくなる。

今回のベースバンドLSIは、前記の五つの処理間はスレッドレベル並列性を持つことから、システムレベルでは処理ごとにDSPを割り当てるようなマルチコア構成としている。一方、各処理内はデータレベル並列性が比較的多いことが分かっている。この並列性を処理する方式は一般にSIMD (Single Instruction Multiple Data) 方式が適している。SIMD方式は、一つの制御部に単純に複数の演算器を並べて複数のデータを一命令で一度に処理するもので、面積あたりの演算性能を高めやすい。このことからDSPの基本的なアプローチとしてはSIMD方式をとることにした。

一般にSIMD方式というと、Intel SSE (Streaming SIMD Extensions) のような固定長 SIMD構成と、ベクトル型スーパーコンピュータで用いられてきたベクトル構成がある。固定長SIMD構成では、1命令でSIMD幅のデータを1サイクルで処理して終了するのに対し、ベクトル構成では、ベクトル長のデータをSIMD幅のデータにハードウェアシーケンサが自動的に分割して複数サイクルにわたって演算を実行する。

ベクトル構成の利点としては、

(1) ベクトルを導入することによって、ハードウェア固有パラメーターであるSIMD幅を意識することなくプログラミングができアプリケーションの可搬性が高まること

- (2) 1命令でSIMD幅以上の配列長に対する演算を指示できるため命令圧縮効率が高まり命令を命令メモリから持ってくる回数（命令フェッチ回数）が減り低消費電力化につながること

- (3) 長年培われてきたデータ並列性抽出プラットフォームの流用が期待できること

- がある。また、富士通の過去のベクトル技術の蓄積を利用できることから、基本アーキテクチャーをベクトル構成とし、マルチコアで対応した。

### 本ベクトルプロセッサ

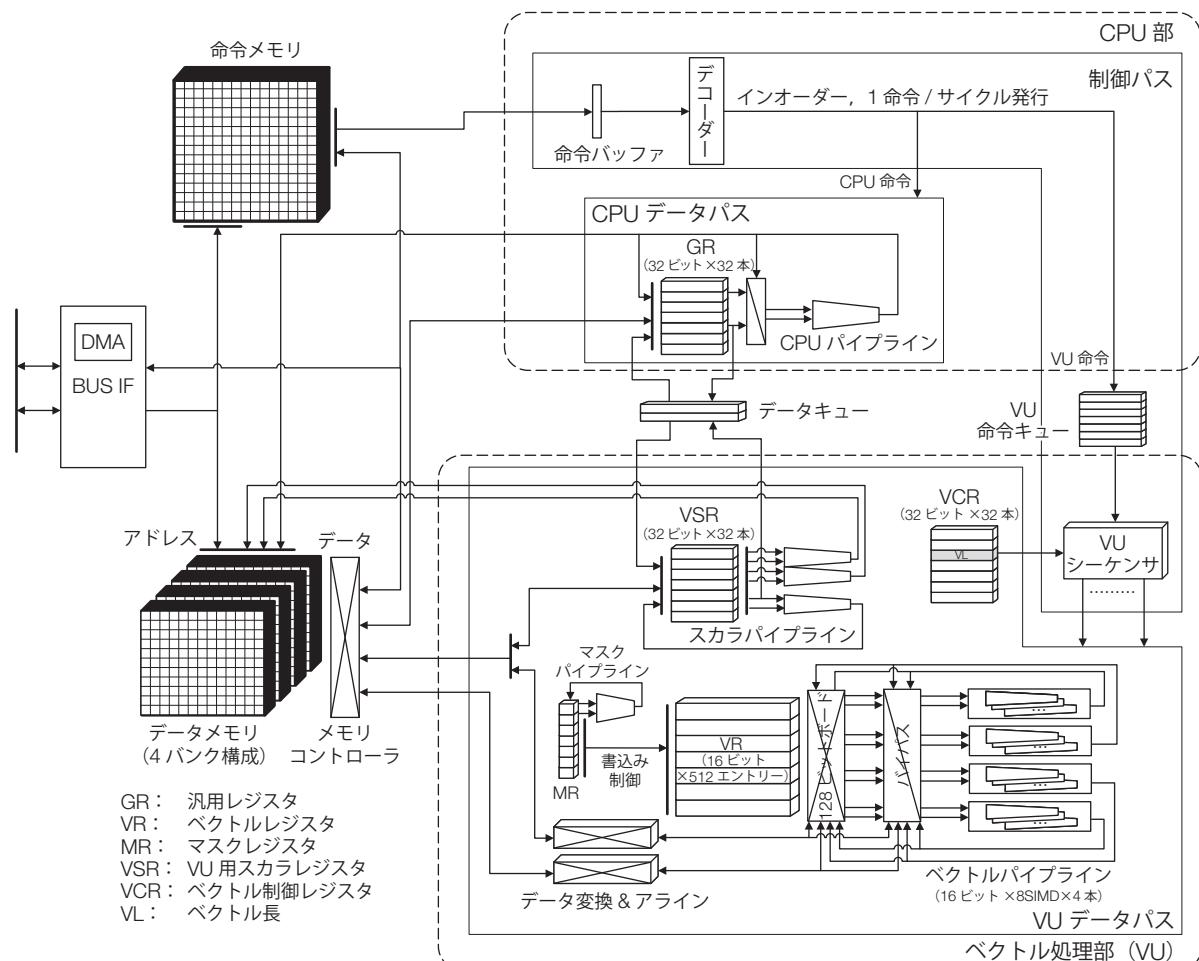

開発したベクトルプロセッサの概要を説明する。**図-1**は開発したDSPのブロック構成である。本ベクトルプロセッサはCPU部とベクトル処理部(VU: Vector Unit)により構成されている。CPUコアにはケイデンス・デザイン・システムズ社のLX3プロセッサを採用している。<sup>(5)</sup>

### ● スペック

**表-1**は本ベクトルプロセッサのVUの主なスペックである。4本あるベクトルパイプラインは乗算パイプラインとロードストアパイプラインが2本ずつで構成されており、ALU系命令は4本全てのパイプラインに発行可能であるが、乗算系とロードストア系命令はそれぞれ2本に制限されている。SIMD幅は8である（16ビットデータ命令時）。最大ベクトル長は対象アプリケーションの性質を考慮して64とした。命令発行性能はサイクルあたり1命令でインオーダー発行であるが、前後の命令間にレジスタ干渉がなければ連續発行が可能であり、レジスタ干渉があったとしてもフォワーディング機構により先行命令のレイテンシが1であれば連續発行が可能である。4本の実行パイプラインをフル回転可能である。命令のレイテンシはALU演算系は1、乗算系は2、ロード系は3（アラインメント処理を含

表-1 主なスペック

| 項目                  | スペック                                          |

|---------------------|-----------------------------------------------|

| 動作周波数               | 250 MHz                                       |

| 語長                  | 8ビット, 16ビット(メイン), 32ビット整数                     |

| パイプライン本数            | ベクトルロードストア・ALU×2本<br>ベクトル乗算・ALU×2本<br>スカラ×1本  |

| パイプライン段数            | 5                                             |

| 1パイプラインのSIMD幅       | 8(16ビットデータ時), 4(32ビットデータ時)                    |

| 命令発行性能              | 1命令/サイクル(インオーダー発行)                            |

| サポートするベクトル長         | 8から64                                         |

| ベクトルレジスタファイル        | 16ビット×512エントリー                                |

| ループ内分岐サポート          | マスクレジスタ内蔵                                     |

| データメモリ              | ~512 Kバイト(128 Kバイト×4バンク)                      |

| ピーク演算性能             | 48オペレーション/サイクル<br>{250 MHz動作で12 GOPS(ギガ命令/秒)} |

| ピーコロードストア性能         | 256ビット/サイクル                                   |

| 消費電力(DSP全体, メモリも含む) | ~30 mW(28 nmプロセスLSI)                          |

む)である。データメモリは資源競合を軽減するため128ビットデータ幅で4バンク構成とした。またベクトルロードストア命令は強力なアドレッシング機能として、一定間隔ごとのアドレスにアクセス可能なストライド機能や、任意の指定したアドレスにアクセス可能なインダイレクト機能を持ち、高速に実行することができる。

## ● 命令セット

表-2はベクトルプロセッサのVUの命令セットの概要である。命令セットはスカラ命令群(CPU命令ではない。命令は40種類)とベクトル命令群(命令は113種類)から構成され命令総数は153である。ベクトル命令には表記以外にターゲットアプリケーション向けの専用命令も存在する。命令長は32ビットである。ベクトル命令の扱うデータ語長は8, 16, 32ビットである。デフォルトのデータ語長はベースバンド処理向けに16ビットとしている。なお、低消費電力は無線処理向けのため、整数演算のみとしている。このほかに、無線信号処理向けの専用命令を持っている。

## ●マイクロアーキテクチャー

DSPの処理の流れについて説明する。まずプログラムは命令メモリ内に格納されている。命令はCPUコア側にのみフェッチされ、命令バッファに格納される。次にCPUコアのデコーダーにおいて命令が解釈される。プログラム列ではCPU命令と

VU命令とが混在している。CPU命令であればCPUデータバスに渡されてCPU側で実行される。分岐命令はCPU側のみにあり、命令流の制御はCPUでのみ行われる。VU命令であればVU命令キューを介してVUシーケンサに渡される。VUは突き放し制御のため、命令を受け取った後は、CPUとは独立に処理を行う。しかし、CPU命令とVU命令間の同期が必要な場合のため、バリア命令によりCPUとタイミングを合わせる仕組みを持っている。VUシーケンサではVU内での、資源競合、既発行命令とのレジスタ干渉を判断し、当該VU命令の発行制御を行う。発行された命令がベクトル命令であれば、ベクトル演算パイプラインに発行される。あらかじめベクトル制御レジスタ(VCR)に指定しておいたベクトル長と、SIMD並列度に応じて当該命令の繰返しサイクル数が決まり、ベクトルパイプラインにおいてそのサイクル数だけ繰り返される。ループ内分岐(条件によって演算結果を選択する機能)サポートのためにマスクレジスタ(MR)を内蔵しており、ほぼ全てのベクトル命令でベクトルの各要素のマスク処理(書き込み制御)を行うことができる。VUからCPUへの転送は転送命令を用いてVUのベクトルレジスタ(VR)からCPUの汎用レジスタ(GR)に移動される。

## ● 性能評価

無線信号処理のコアルーチンをいくつか用いて、

表-2 命令セット

| ベクトルプロセッサのVUが持つ命令 |                    | 命令が扱うデータ語長 |       |       |       |

|-------------------|--------------------|------------|-------|-------|-------|

|                   |                    | 8ビット       | 16ビット | 32ビット | 64ビット |

| スカラ命令             | スカラロード, ストア        | ○          | ○     | ○     | ○     |

|                   | スカラ加算              | —          | —     | ○     | —     |

|                   | スカラシフト             | —          | —     | ○     | —     |

|                   | スカラ論理              | —          | —     | ○     | —     |

|                   | スカラ移動, 即値セット, カット  | —          | —     | ○     | —     |

| ベクトル命令            | ベクトルロード, ストア       | ○          | ○     | ○     | —     |

|                   | ベクトル加算             | —          | ○     | ○     | —     |

|                   | ベクトル乗算, 積和, 内積     | —          | ○     | —     | —     |

|                   | ベクトルシフト, 比較        | —          | ○     | ○     | —     |

|                   | ベクトル論理             | —          | ○     | —     | —     |

|                   | ベクトル語長変換, ビット操作    | —          | ○     | ○     | —     |

|                   | ベクトル選択             | —          | ○     | —     | —     |

|                   | ベクトル最大, 最小値検索      | —          | ○     | ○     | —     |

|                   | ベクトル抽出, 総和         | —          | ○     | ○     | —     |

|                   | ベクトル移動, シャッフル, マージ | —          | ○     | —     | —     |

|                   | ベクトルマスク            | —          | —     | —     | —     |

|                   | ベクトルバリア制御          | —          | —     | —     | —     |

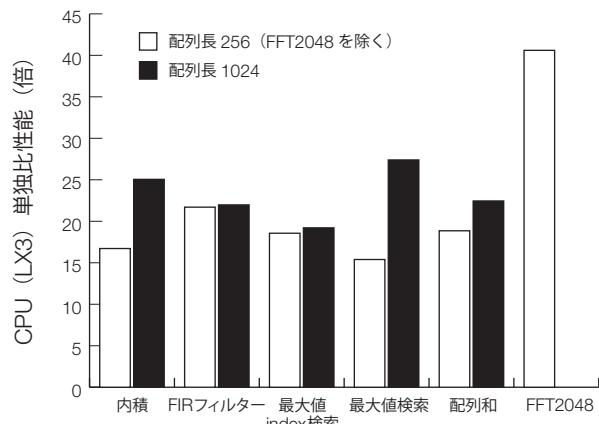

本ベクトルユニットを用いた場合の性能を、CPU (LX3) 単独の場合と比較した。評価にはサイクル精度シミュレーターを用いた。ベクトル化は手動アセンブルプログラミングである。対CPU比性能を図-2に示す。評価用プログラムは内積、最大値検索などの基本的な処理を行うもので、配列サイズは256と1024である (FFTは2048ポイント)。配列サイズが大きい方が性能向上が大きいことが分かる。対CPU比で最大40倍の性能である。対象処理のコアルーチンを大きく加速することで、所望の処理性能を実現している。

### 考 察

ベクトル構成のシステムには、富士通VPPシリーズやNEC SXシリーズ (地球シミュレーター)<sup>(6)</sup>、また、ベクトル部をコプロセッサとして切り出したものとして富士通μVPがある。<sup>(7)</sup> 富士通研究所が開発したベクトルプロセッサの基本アーキテクチャーはこれらを踏襲し、ベースバンド処理に適するように、データ語長や最大ベクトル長を制限したり、レジスタファイルをコンパクトにしたりしている。ベクトル構成をとることで、FORTRANなどの既存のプラットフォームの流用

図-2 対CPU比性能

が容易になる。今後また見直される有望なアーキテクチャーであると期待できる。

### む す び

本稿では富士通研究所が開発したベクトルプロセッサについて紹介した。基本アーキテクチャーはベクトル型スーパーコンピュータを踏襲している。ピーク演算性能は12 GOPS (ギガ演算/秒) である。また、28 nmプロセスLSIで平均30 mW程度の消費電力に抑えることができ、ターゲットであ

る端末用LTE対応ベースバンドLSI向けに所望の性能を得ることができた。本ベクトルプロセッサは富士通の商用ベースバンドLSIに採用されている。

## 参考文献

- (1) 佐々木 啓ほか：LTE対応Multi-RAT (Radio Access Technology) ベースバンドLSI. *FUJITSU*, Vol.63, No.5, p.598-602 (2012).

- (2) Y. Ge et al. : A vector coprocessor architecture for embedded systems. SoC Design Conference (ISOCC), 2011 International, p.195-198, 17-18 Nov. 2011.

- (3) C. Batten : Vector-thread architectures. Churchill College Graduate Student Seminar Series, University of Cambridge, Mar. 2004.

- (4) D. A. Patterson : Future of computer architecture. Berkeley EECS Annual Research Symposium 2006, Feb. 2006.

<http://www.eecs.berkeley.edu/BEARS/presentations/06/Patterson.ppt>

- (5) ケイデンス・デザイン・システムズ社.

<http://www.tensilica.com/>

- (6) T. Sato : The earth simulator : Roles and impacts Nuclear Physics B - Proceedings Supplements In Lattice 2003, Vol.129-130, p.102-108, Mar. 2004.

- (7) M. Awaga et al. : The  $\mu$ VP 64-bit Vector coprocessor : A New Implementation of High-Performance Numerical Computation. *IEEE Micro*, Vol.13, No.5, p.24-36 (1993).

## 著者紹介

葛 賢 (かつ たけし)

ユビキタスプラットフォームテクノロジー研究所エンベデッドプラットフォーム研究部 所属

現在、携帯端末用ベースバンドSoC向けDSPの開発に従事。

伊藤真紀子 (いとう まきこ)

ユビキタスプラットフォームテクノロジー研究所エンベデッドプラットフォーム研究部 所属

現在、携帯端末用ベースバンドSoC向けDSPの開発に従事。

伴野 充 (ともの みつる)

ユビキタスプラットフォームテクノロジー研究所エンベデッドプラットフォーム研究部 所属

現在、携帯端末用ベースバンドSoC向けDSPの開発に従事。

廣瀬佳生 (ひろせ よしお)

ユビキタスプラットフォームテクノロジー研究所エンベデッドプラットフォーム研究部 所属

現在、携帯端末用ベースバンドSoC向けDSPの開発に従事。