# 電源ノイズ解析のためのLSIノイズモデル

# LSI Noise Model for Power Integrity Analysis

#### あらまし

半導体プロセスの微細化に伴い,システムLSIの設計において,電源ノイズ対策のための設計が重要な課題となってきている。著者らはこの課題に応えるべく,電源ノイズを解析するためのLSIモデル作成およびシミュレーションのフローを開発した。このフローを用いてシミュレーションすることで,システムLSI内部で発生する様々なノイズ,例えば入出力回路の同時スイッチングノイズや,LSI内論理回路動作時に発生するノイズを求めることができる。さらにLSIの設計初期段階の電源設計に本モデルを用いることで,電源配線やパッケージ電源ピン数の最適化を実施して,システムLSIのコストを下げることも可能となる。本稿では,まず電源設計で考慮しなければならないノイズについて説明する。つぎにそ

本稿では,まず電源設計で考慮しなければならないノイズについて説明する。つぎにそのノイズを表現できるLSIノイズモデルの全体構成,作成フロー,精度確認のためのテスト回路の評価結果,および本モデルの商品開発への展開について述べる。

#### Abstract

Together with semiconductor technology scaling, power integrity inside System-on-Chips has become a major design issue. To investigate this issue, we created an LSI noise model and developed a simulation methodology to analyze power integrity. Using this methodology, we can simulate noise waveforms inside an LSI to obtain, for example, the simultaneous switching noise of I/O circuits and core noise caused by dynamic LSI currents. We can also use this model in the initial design stage to optimize the power wiring, minimize the power pin count, and thereby minimize System-on-Chip costs. In this paper, we describe the noise that must be taken into consideration when designing an LSI's power system. We then describe the overall configuration and generation flow of the LSI noise model, measurement results of the test chip we used for verifying the model's accuracy, and the application of the model in product development.

佐藤富夫(さとう とみお) システムLSI開発研究所SOC設計技 術研究部 所属 現在,システムLSIのノイズ解析に 関する研究に従事。

橋本鉄太郎(はしもと てつたろう) システムLSI開発研究所SOC設計技 術研究部 所属 現在,システムLSIのノイズ解析フローに関する研究に従事。

笹川隆平(ささがわ りゅうへい) システムLSI開発研究所SOC設計技 術研究部 所属 現在,システムLSIのノイズ解析・ モデル実証に関する研究に従事。

## まえがき

半導体プロセス技術の発展に伴い,システムLSI の高速化,高機能化が進んでいる。システムLSIは今や携帯電話やデジタルカメラなどの民生機器に広く使われており,キーデバイスとして不可欠の存在となってきた。

一方このプロセス技術の発展により, LSI設計分 野にはまったく新しい深刻な技術課題がもたらされ た。それは低ノイズ設計である。これは以下の二つ の理由による。第一は,発生側の要因としての,電 源ノイズ量そのものの増加である。LSIの高速化, 高機能化は,集積されるトランジスタ数の増加や入 出力ピン数の増加と動作周波数の向上を意味し,消 費電流の増加に直結する。消費電流が増加すれば、 それに伴う電源ノイズ量も必然的に増加し,極端な 場合にはLSI自身の出したノイズで,自分自身が誤 動作することもあり得る。第二は,受け側の要因と しての、ノイズ耐性の低下である。半導体素子が微 細化されると,素子特性を維持するために,電源電 圧を下げる必要が生ずる。これは低電力化というメ リットがある一方で、従来と同じレベルのノイズを 受けても誤動作しやすくなるというデメリットを併 せ持つことになる。このように,電源ノイズ量の増 加とノイズ耐性の低下という二つの現象の負の相乗 効果により、システムLSIのノイズ設計は、最重要 課題として急浮上してきた。

ノイズ設計に対する取組みには従来からいくつかの手法があり、特定の課題からとらえるのが一般的である。例えば不要電磁放射(EMI: Electromagnetic Interference)ノイズの観点からとらえた報告や、LSIの動作速度の観点から実測ベースで調査した報告(1)などがある。ノイズ設計の課題はこれら以外にも、入出力回路の同時スイッチングノイズ(SSN: Simultaneous Switching Noise)や、クロックジッタへの影響、システムLSI自身のノイズ源としての特性の表現など多岐にわたる。システムLSIの電源設計においては、当然のことながら、これらの課題をすべて同時に解決しなければならない。

LSIのノイズ設計は、ノイズの発生源、伝播経路、受け側の三つの側面がある。著者らは今回前者二つに着目した。ノイズの発生源と伝播経路が特定できれば、問題の所在を絞り込めるため、受け側でのノ

イズの影響を評価しやすい。また著者らは,一つですべてのノイズを表現できるLSIノイズモデルを提案,開発した。これにより,ある特定種類のノイズ課題に対する対策がほかの種類のノイズに与える影響を知ることができ,電源ノイズ全体像の把握の手助けとなる。

本稿では、まず電源設計で考慮しなければならないノイズについて説明する。つぎにそのノイズを表現できるLSIノイズモデルの全体構成、作成フロー、精度確認のためのテスト回路の評価結果、および本モデルの商品開発への展開について述べる。

#### LSIノイズモデルへの要請

LSIのノイズモデルで表現しなければならない項目は,つぎの二つである。

- (1) LSIコア内電源ノイズの空間分布とその時間 変化

- (2) 入出力回路(IO回路)の電源ノイズの空間分布とその時間変化

- (1)は、LSI内の論理回路動作に伴うノイズである。このノイズが発生すると、瞬間的にLSIコア内の電源電圧が低下し、LSI自身の速度性能も低下する。またクロック分配系にこのノイズが加わると、クロックジッタの増加を引き起こし、これも性能低下の原因となることが多い。本ノイズを表現できれば、コア内の論理回路やクロック分配回路の電源部への影響をシミュレートし、必要に応じて対策を打つことが可能となる。

(2)は,入出力回路の同時スイッチングに伴う ノイズである。このノイズが発生すると,論理反転 による誤動作が発生したり,IO回路自身の遅延増 大によるタイミング不足などの形で,動作不良を引 き起こしたりする。近年のDDRやRAMBUSなどの 高速インタフェースでは,IO回路のタイミング設 計が非常に厳しく,このノイズによる速度性能低下 は無視できない。

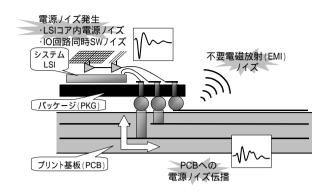

加えて上記二つのノイズモデル表現は,LSI内部の回路動作への影響を評価するのに有用なだけでなく,LSIが外部へ発するノイズの性質,つまりLSIのノイズ源としての性質を表すものとしても利用できる。これはプリント基板(PCB: Printed Circuit Board)を含んだシステム設計に有用である。図-1に示すようにシステム設計では,不要電磁放射

図-1 LSI電源ノイズの振る舞い Fig.1-Behavior of LSI power noise.

(EMI) ノイズや、PCB内の電源電位の変動が、ほかの電子回路に悪影響を及ぼす。PCB上のノイズ評価ツールはいくつかあるが、いずれもPCB単体の解析にとどまっており、ノイズ源のモデル化が大きな課題として残っている。システム設計上、最大のノイズ源はLSIであり、そのノイズの表現が、PCBを含んだシステム全体のノイズ設計において、強く求められている。

#### モデルの構成

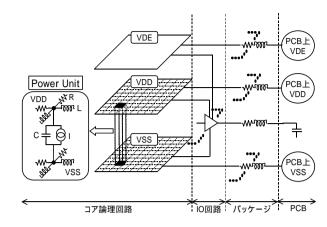

開発したLSIノイズモデルの全体構成を図-2に示す。ノイズモデルは,コア論理回路部,IO回路部,パッケージ(PKG)部の三つから構成される。以下,それぞれについて順に説明する。

#### コア論理回路部

従来手法を用いてLSI内コア部分の電源配線や容量,電流分布を抽出した場合,その素子数が膨大になり,計算機上でシミュレーションできないことはよく知られている。素子数圧縮についても検討されているが,十分な成果は得られていない。

そこで著者らはLSIの電源を、図-2に示すように電気的にモデル化した。この最小単位をパワーユニット(Power Unit、以下PU)と呼ぶ。このモデル化は、LSIコアをPUに分割し、その電気特性をPU単位の空間分布で表現するという手法である。この手法は、電源ノイズの空間分布の全体像を少ない素子数で表現できるという大きなメリットを持っている。PUのサイズは、必要となる空間分解能と計算機リソースのトレードオフで決める。典型的には、一辺100~200 μm程度の長方形を用いる。LSIコア内のノイズ伝播速度は10 mm/ns程度で、周波

図-2 LSI ノイズモデル全体構成 Fig.2-Structure of LSI noise model.

数5 GHzまでのノイズ成分は十分表現できると考えられる。

PUは図-2に示すように,インダクタンス(L),抵抗(R),容量(C),電流(I)の4種類の素子を,電源種別ごとに格子状に結合した構造を持っている。LとRは,電源配線の面内分布を表現する。一般にPUの大きさは実際の電源配線に比べて粗くなるのが普通であるが,PU内の電源配線をすべて合成したLR値で代表する。

Cは,LSIコア論理回路内の容量分布を表現する。 主な成分は,電源配線,容量セル,ロジック回路の 持つ容量,シリコン基板のウェル容量である。ここ もPU内の全容量を加算したものを用いる。

IはLSIコア論理回路内の消費電流の面内分布と時間変化を表現する。PU内の全論理回路の電流を合成したものである。

#### IO回路部

本モデルでは、LSIの信号と電源を1ピンごとに別々にモデル化している。IO回路部ではピン間のノイズカップリングで不具合を起こすケースが多い。本モデルの手法を使えば、ピンごとのノイズカップリングを解析でき、これによる不具合をLSI設計初期に回避可能である。IO回路のネットリストは、PCB設計で通常使用されているIBIS(IO Buffer Information Specification)などの線形モデルでは精度的に不十分で、トランジスタを含むネットリストを使用している。

#### パッケージ部

パッケージのモデルは市販の電気特性抽出ツール が作成するネットリストを使用する。IO回路部に

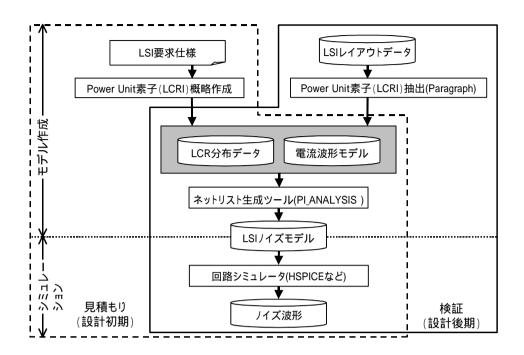

図-3 LSI ノイズモデル作成およびシミュレーションフロー Fig.3-LSI noise model generation and simulation flow.

合わせ,1ピン単位に電気特性が表現されているものを用いる。

#### モデル作成、シミュレーションフロー

本LSIノイズモデルでは、図-3に示すように、設計初期の見積もりと、設計後期の検証の双方に対して、モデル作成とシミュレーションを一連のフローに従い実行できる。見積もりフローと検証フローの違いは、PUを構成するLCRI素子の作成方法にある。見積もりでは、設計者がLCRIの素子値をLSI仕様書から概算で求め、検証では、レイアウトデータから自動抽出(ツール名:Paragraph)する。

いずれの場合にも格子状LCRIの値は,ネットリスト作成ツールPI\_ANALYSISによりLSIのノイズモデルに変換され,SPICE系の回路シミュレータ(注)を用いてシミュレーションされる。

一般にシステムLSIの電源設計は、PKGの種類やピン数、電源配線の面積など、チップコストに直接影響を与えることが多い。また電源は配置配線などの詳細物理設計の前提となるため、設計後半で変更することができないという性質も持っている。このため電源の設計では、設計初期に最終形態に近い精

度の設計をしなければならない。図-3に示した見積もリフローを用い、最終形態を意識した電源ノイズ評価を実施することで、コストの削減と、手戻りの少ない設計が可能となる。

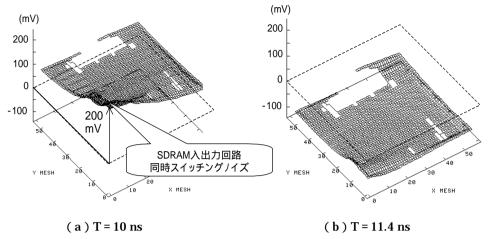

本フローを用いてシミュレーションした結果の一例を図-4に示す。図-4の(a)と(b)はLSI面内のグランド層VSSのノイズ分布が,時間的に変化する様子を示している。(a)のLSI周辺部でVSS電位が顕著に上昇している部分があるのは,SDRAM入出力回路の同時スイッチングによるものである。ノイズ量は約200 mVである。図-4の(a)と(b)を比べると,LSIのVSS電位全体も大きく揺れることが分かる。

なお,このシミュレーションでは,PCB上のグランドを電位の基準としている。

#### テスト回路と評価結果

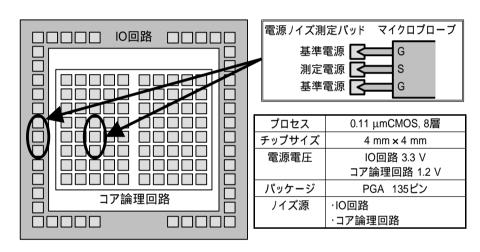

本稿で述べたLSIノイズモデルを実設計に適用するためには、電源ノイズの実測とシミュレーションの比較による精度確認が必要である。この比較を目的として、テスト回路を開発、評価した。テスト回路の構成を図-5に示す。テスト回路は、LSIのコア論理回路部とIO回路部を模擬する回路、チップ内の電源ノイズ波形を測定するための測定パッド、測

<sup>(</sup>注) SPICE系の回路シミュレータとしては,業界標準の HSPICEや,社内製のTCSなどがある。

# 電源ノイズ解析のためのLSIノイズモデル

図-4 シミュレーション結果 (VSS面) Fig.4-Simulation results of VSS plane.

図-5 テスト回路の構成 Fig.5-Structure of test chip.

定専用の基準電源から構成される。電源ノイズ波形は,LSI内の測定パッドにマイクロプローブを直接接触させて測定した。

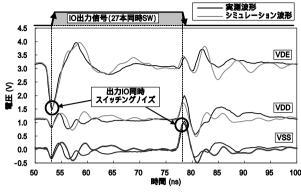

実測波形と、LSIノイズモデルを用いたシミュレーション波形の比較を図-6に示す。図-6(a)は、27本のIO出力信号が同時にスイッチングしたときのノイズを示したものである。信号の立上がりで、VDE電源に大きな負のノイズが乗っているのが分かる。このノイズピークが、誤動作やタイミング変動を引き起こすノイズであり、ピーク値の一致が本モデルをLSI電源設計で使用できるか否かの判断ポイントとなる。図から分かるように、実測波形とシミュレーション波形がよく一致している。同様に信号の立下り時はVSS電源に大きな正のノイズが乗っているが、ここでも実測波形とシミュレーション波

形の一致が良い。

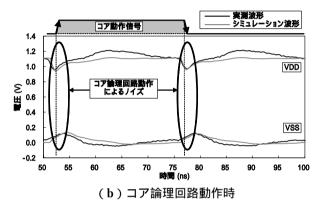

図-6(b)は,コア内論理回路の動作によるノイズ波形を示したものである。回路動作に合わせて,VDD電源には負の,VSS電源には正のノイズピークがそれぞれ発生している。ここでも10%以内の誤差で,実測波形とシミュレーション波形がよく一致している。

ノイズピーク後の振動波形については,実測波形とシミュレーション波形の差が大きい。この違いは,主にシミュレーションの振動波形の方が実測波形よりも低周波であることに起因する。このことは,PCBや電源装置を含んだ全体の詳細なモデル化の必要性を示している。

(a) IO回路同時スイッチング時

図-6 実測とシミュレーションの波形比較 Fig.6-Comparison of measurement and simulation.

# 商品開発への展開

開発したLSIノイズモデルの商品開発への展開として,つぎの二つに取り組んでいる。

#### (1) LSI開発期間の短縮とコスト削減

システムLSIの設計では開発期間の短縮が非常に 重要である。加えて電源設計は,LSIの面積やPKG のピン数の点でコストに大きく影響する。富士通で は今回開発したモデルを用いて電源設計ルールを作 り設計に適用することで,手戻りの少ないLSI設計 を実現している。またLSI設計初期段階でのコスト 見積もりおよびコスト削減にも併せて取り組んで いる。

#### (2) LSIとPCBの協調設計

PCBを含むシステム全体の設計では、LSIとPCB全体でノイズ削減することにより、不具合を起さないシステム設計が可能となる。富士通では既にPCB上のノイズ解析ツール<sup>(2)</sup>を開発しており、これに本モデルを組み込むことで、LSIとPCBの協調設計ソリューションを提供している。

# む す び

本稿では,今後重要となるシステムLSI設計の電源ノイズ解析に使用されるLSIノイズモデルを紹介した。

半導体プロセスの微細化に伴って急浮上してきた電源ノイズ対策設計という課題を解決するために,少ない素子数で複数種類のノイズを表現できるLSIノイズモデル,および設計初期見積もりと検証の双方に対応した解析環境を開発した。加えてテスト回路を作成し,電源ノイズの実測とシミュレーションの比較をすることで,本モデルの精度が十分であることを確認した。

## 参考文献

- (1) T. R. Arabi et al.: Design & Validation of the Pentium III and Pentium 4 Processors Power Delivery. in Dig. Tech. Papers, 2002 Symposium on VLSI Circuits, 16-4.

- (2) 平井天道ほか:高速伝送基板における電源ノイズ 解析システム:SIGAL-PI. FUJITSU, Vol.55, No.3, p.257-261 (2004).