# 90 nm CMOSテクノロジの概要

# Overview of Fujitsu's New 90 nm CMOS Technologies

## あらまし

本稿では,富士通の90 nm CMOSテクノロジCS100,CS100Aの概要について解説する。膨大なデジタルデータが飛び交うネットワーク社会において,サーバの高性能化や携帯端末の小型化が進み,その中枢となる技術としてLSIの小型化,高性能化,低消費電力化が要求されている。CS100,CS100Aはこれらの要求に対応するために開発されたテクノロジである。CS100は,サーバなどの高性能重視のハイエンド商品向けに開発され,最先端の半導体技術を駆使し世界トップレベルの性能を達成している。一方,CS100Aは低消費電力を要求するモバイル機器から膨大な画像データを高速処理するデジタルAV機器まで広範囲なコンシューマ市場をカバーするために開発され,CS100で培われた技術を部分的に取り込み,コストパフォーマンスに優れたテクノロジである。

#### Abstract

Huge volumes of digital data are constantly being exchanged in today's network-oriented society. To keep up with demands, servers are becoming more powerful and mobile communication terminals are becoming smaller. Consequently, LSIs, which are the core components of these devices, need to be more compact and have a higher performance and lower power consumption. In response, Fujitsu has developed two new series of 90 nm CMOS LSIs: the CS100 and the CS100A. The CS100 series makes full use of cutting-edge semiconductor technologies and attains the world's top level of performance. This series is intended for use in servers and other high-end equipment. The CS100A series uses some of the new technologies developed for the CS100 series and provides cost-effective performance. This series is intended to cover the extensive consumer markets for low power consumption mobile devices and digital multimedia equipment (which must process vast amounts of image data at high speed). This paper gives an overview of the CS100 and CS100A series.

甲斐睦章(かい むつあき) 次世代LSI開発事業部第一テクノロ ジ開発部 所属 現在,次世代LSIの開発に従事。

久保田勝久(くぼた かつひさ) 次世代LSI開発事業部 所属 現在,次世代LSIの開発に従事。

木本雅義(きもと まさよし) 次世代LSI開発事業部第一テクノロ ジ開発部 所属 現在,次世代LSIの開発に従事。

## まえがき

ブロードバンド,ユビキタス時代を迎え,膨大な情報がインターネット上を飛び交う現在において,その流通を支えるサーバの高性能化と,いつでもどこでも情報を引き出せる各種携帯端末の高性能化,低消費電力化および小型化が求められてきている。また,デジタル放送やDVDの普及などデジタル化が急速に進み,膨大な画像データの高速処理も必要となっている。

このような市場の要求にいち早く対応するため, 富士通は「90 nm CMOSテクノロジ」と総称される最先端製造技術を駆使し, サーバなどのハイエンド市場を主ターゲットとした超高性能な "CS100"テクノロジと,携帯端末やデジタルコンシューマ市場をターゲットとした低消費電力かつ高性能な "CS100A"テクノロジの開発に取り組み,世界に先駆けその量産技術の確立に成功した。

本稿では,その90 nm CMOSテクノロジCS100 およびCS100Aの概要について紹介する(1)-(4)

## CS100, CS100Aの開発コンセプト

本章では, CS100, CS100Aの開発のねらいと特徴について説明する。

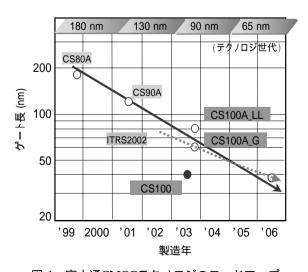

広範囲な市場をカバーするトランジスタ技術図-1は,富士通CMOSテクノロジのロードマップである。

一般的に,テクノロジを代表するキーパラメタと

図-1 富士通CMOSテクノロジのロードマップ Fig.1-Fujitsu CMOS technology roadmap.

して,トランジスタのゲート長(Lgate)が用いら れる。このゲート長が小さいほどトランジスタのス イッチング性能は良くなり、また高集積化(微細 化)の指標ともなる。これまで約2年ごとに0.7倍の 縮小率で微細化が継続されてきたが、年々そのスピー ドは加速し,国際機関であるITRS (International Technology Roadmap for Semiconductors ) が規定 するロードマップも毎年の見直しを余儀なくされて いる。これに対し富士通は,ハイエンド市場をター ゲットとするCS100では,最先端技術を駆使して, ロードマップより微細で量産技術としては世界最小 レベルのLgate = 40 nmトランジスタを開発・実現 した。また、コンシューマ市場をターゲットとする CS100Aにおいては,コストを重視しCS100よりも廉 価な技術で製造できるLgate = 60 nm (CS100A\_G) を採用した。これは90 nm CMOS世代標準値と なっている。さらに携帯電話などの低消費電力重視 の商品向けに、トランジスタリーク電流を最小限に 抑えたLgate = 80 nm (CS100A LL) の低リーク トランジスタも用意した。

これによって,ギガヘルツ動作の高性能チップから,待受時間500時間以上を実現できる携帯電話向けチップまで広範囲な市場をカバーすることが可能となる。

## 3世代で培った銅配線技術

テクノロジ開発においてはトランジスタ開発と同様に多層配線技術開発も重要となる。前述したゲート長同様,テクノロジ世代の進歩とともに0.7倍の縮小率で微細化が進み,CS100, CS100Aの90 nm CMOS世代では,配線幅0.12 μm, 間隔0.12 μmの 微細加工が必要となる。

微細化に伴い配線抵抗の増加と配線容量の増加が問題となるが、配線材料には、より比抵抗の低い銅を使用した。また、これまで部分的に使用してきた低誘電率膜を多層間全面に使用し低容量化を図った。銅配線技術においては信頼性の確保が重要な課題となっているが、富士通では180 nm世代からいち早く採用し、3世代にわたる実績と技術の積上げによって高信頼性を確保している(図-2)。

SMIF方式の最先端工場と研究所との連携強化これらのテクノロジでデバイスを生産するのが、あきる野テクノロジセンターにある最先端工場である。90 nm CMOS世代以降の次世代テクノロジ開

188 FUJITSU.55, 3, (05,2004)

## 90 nm CMOSテクノロジの概要

CS80シリース Cu-6層 絶縁材料:FSG 配線ピッチ:0.6 μ m

CS91シリーズ Cu-7層 絶縁材料: Hybrid Low-k 配線ピッチ: 0.36 μ m

CS100/101シリーズ Cu-10層 絶縁材料:Full Low-k 配線ピッチ: 0.24 μ m

0.18 μ m / ード 0.13 μ m / ード テク / ロジ世代

90 nm ノード

図-2 3世代のCu配線技術 Fig.2-Fujitsu copper interconnect technology.

発と初期量産を担うラインとして2001年から稼働した。工場稼働と同時に研究所との連携も強化するために、あきる野テクノロジセンターに開発技術者を集約し、効率的な開発を進めてきた。装置も微細化のためにArFと呼ばれる最先端露光装置をはじめとした最新鋭の装置を配備し、またクリーンルーム構築においては、SMIF(Standard Mechanical Interface)方式を採用した。これにより、SMIFポッドと呼ばれる密閉容器内のクリーン度を上げればよいため、製品製造と設備工事が同時に可能となり、工場施工からテクノロジ開発までの期間を大幅に短縮することができた。またクリーンルーム内のクリーン度も従来ほど上げる必要もないため、投資額の抑制にもつながっている。

#### ハイエンド商品向けCS100の概要

本章では,ハイエンド商品向けに開発した CS100の概要について説明する。

世界トップクラスの40 nm高性能トランジスタ 前述したようにCS100は高性能サーバをはじめ とした高速性を重視するハイエンド市場向けのテク ノロジである。そのキーテクノロジとなるのが, Lgate = 40 nmの高性能トランジスタである。

他社ハイエンドトランジスタとの特性比較を図-3に示す。他社データは学会などの発表資料を参考にした。スピード性能に最も重要なパラメタはオン電流値(Ion)である。この値が大きいほどスピード性能は良くなる。また,オフ電流値(Ioff)はチップのパワーに対してキーとなる特性である。最先端のCPUチップにおいては,消費電力も100Wを超

| Affiliation            | FUJITSU      | Samsung                 | Intel     | TSMC      |

|------------------------|--------------|-------------------------|-----------|-----------|

| Conference             | SPARC64<br>V | 2003 Symp<br>VLSI Tech. | 2002 IEDM | 2002 IEDM |

| Lgate (nm)             | 40           | 50                      | 50        | 45/50     |

| Vdd (V)                | 1            | 1                       | 1         | 1         |

| lon (n) ( μ A/ μ m)    | 960          | 870                     | 1,000     | 830       |

| lon (p) ( μ A/ μ m)    | 390          | 390                     | 480       | 380       |

| loff $(n/p)(nA/\mu m)$ | 70           | 75                      | 100       | 75        |

TEM photo shows the high-quality finished form of CS100 MOSFET

図-3 CS100と他社ハイエンドトランジスタとの比較 Fig.3-High-end transistor comparison.

え,実装時の冷却,信頼性の面でも問題となってきており,このオフ電流をいかに抑制するかも大きな課題となっている。

問題は,このオン電流値とオフ電流値がトレードオフの関係にあることであり,オフ電流を下げるとオン電流値が下がってしまう。いかにオフ電流を抑えつつ,オン電流を上げていくかがトランジスタ開発の大きな課題であり,各社その点でしのぎを削っている。CS100はオフ電流を70 nA/μmと他社並に抑えつつ,オン電流値960 μA/μmといった高電流値を確保し,ゲートスピードでは標準インバーター段あたり7 psの世界トップのスピード性能を量産レベルで達成している。

トランジスタの微細化においては,その加工技術も大きな課題となる。現在最先端の露光装置はArFエキシマレーザと呼ばれる波長193 nmの光源を使用している。数年前までは安定して加工できるのは光源波長と同じ寸法までと言われており,その5分の1の寸法である40 nmを安定して作る困難さが分かると思う。これに対して半導体メーカは露光装置メーカやマスク製造メーカと共同してこの問題に取り組み,いかに微細化のトレンドを維持し,さらに他社との差別化を図るために微細化を進めるといった開発競争を続けている。

富士通では,40 nmのゲート加工技術として,OPC(Optical Proximity Correction)と呼ばれる 光近接効果補正とハーフトーン位相シフトレチクル およびレベンソン位相シフトレチクルと呼ばれるレ チクル技術を駆使し,さらにAPC(Advanced Process Control)と呼ばれる製造の後工程への フィードバック技術と併せてゲート寸法の安定化を 図っている。

#### 銅配線10層 + アルミ配線1層の多層技術

配線技術の開発においてキーとなるのは,低抵抗化,低容量化,信頼度確保である。定性的には微細化に伴い配線は細くなり抵抗は上昇し,配線間隔は狭くなり容量が上昇するためスピード性能へのインパクトが大きくなる。また,配線が細くなることに加え高性能化により配線に流れる電流密度が増大するため,信頼性の維持が課題となる。その対策として,従来のアルミ配線から,より低抵抗で電流密度耐性の良い銅配線への移行が行われてきた。それとともに低容量化のために配線層間絶縁膜の低誘電膜への変更も行われてきているが,銅配線特有の課題をかかえ量産化に苦労している半導体メーカも少なくない。

富士通では,他社に先駆け0.18 µm CMOS世代から銅配線を採用し,CS100の配線は3世代目となる。これまでのノウハウの積み重ねから比較的スムーズに立上げが完了した。

積層構造は,銅配線10層 + アルミ配線1層を採用し,それぞれの配線層の構造は以下のような配線構造となっている。

(1) Metal1層 材料Cu

幅/間隔 0.12 µm/0.12 µm

(2) Metal2-4層 材料Cu

幅/間隔 0.14 µm/0.14 µm

(3) Metal5-8層 材料Cu

幅/間隔 0.28 µm/0.28 µm

(4) Metal9-10層 材料Cu

幅/間隔 0.42 µm/0.42 µm

(5) Metal11層 材料Al

幅/間隔 0.84 µm/0.84 µm

Metal1-4の下層配線は,主に基本セル設計および基本セル間の比較的短い配線用途に使用され,集積度を重視し,この世代での最小加工寸法の配線となっている。また,Metal5-8は,基本セルを組み合わせて作成した機能ブロック間を結線する比較的長い配線用途に使用されるため,低抵抗化を重視し,下層の配線よりも配線厚を厚くした配線となっている。Metal9-10の上層配線は電源配線,クロック配線などのチップ全体に引き回される配線に利用され,さらに低抵抗化が必要となるため,非常に厚い配線

となっている。信号配線に使われるMetal1-8の配線は,信号伝播時間の短縮のために低容量化も重要となり,富士通では配線間の絶縁材料に比誘電率の低いLow-k材料を配線層間全体に使用し低容量化を図っている。

これらの高度なトランジスタ技術と,高度な配線 技術を組み合わせることによって,世界トップレベ ルの性能を達成している。

## コンシューマ商品向けCS100Aの概要

本章では,コンシューマ商品向けに開発した CS100Aの概要について説明する。

廉価で幅広い市場ニーズへの対応

コンシューマ向けのテクノロジでは,ハイエンドテクノロジ以上に,廉価で幅広い市場ニーズへの対応が必要となる。ハイエンド商品向けCS100の開発によって得られた要素技術を取り入れながら,レベンソン位相シフトレチクルなどのコストの掛かる部分をカットし,廉価版のCS100Aテクノロジを開発した。

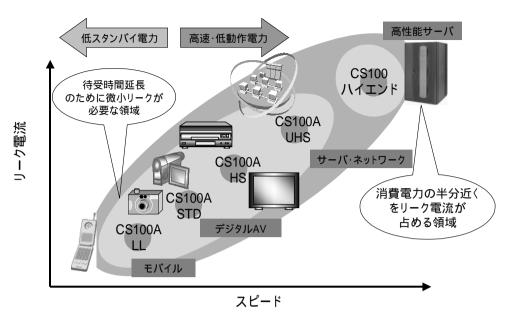

CS100Aがカバーする市場は幅広い。携帯電話などのバッテリ駆動の携帯機器から、デジタル映像処理やPC・サーバ周辺機器などの高速性を重視する商品までをカバーする。

それぞれの市場によって,要求されるトランジスタが異なってくるが,幅広い要求に対応するためCS100Aでは,Lgate = 60 nm,電源電圧1.0 Vの90 nm世代標準のCS100A\_G(Generic)に加えLgate = 80 nm,電源電圧1.2 Vの低リークで高性能を維持したCS100A\_LL(Low Leak)テクノロジを用意した。ここでは,後者のCS100A\_LLについての概要を中心に説明する。

ハイエンド商品向けのCS100の説明でも述べたが、トランジスタ特性ではオン電流とオフ電流はトレードオフの関係になる。携帯電話のような待機時の消費電流を重視する商品にはオフ電流の少ないトランジスタが必要となるが、このようなトランジスタではオン電流が小さくなり、処理性能が上げられない。またDVDデコーダなど膨大な画像データを処理するような商品では高速処理のためにオン電流の大きいトランジスタが必要となるが、このようなトランジスタではオフ電流を下げることが難しくなる。さらに、最近のSOC(System-on-a-Chip)化

図-4 CS100とCS100Aの幅広い適用分野 Fig.4-Extensive market of CS100 and CS100A.

に伴い,機能マクロごとに高速性を重視するもの,低リーク電流を重視するものが同チップ内に混載するようにもなってきている。このように多様化する商品へ対応するためにオン電流とオフ電流のバランスを変えた四つのトランジスタを用意し,用途に応じた使い分けができるようにしている(図-4)。

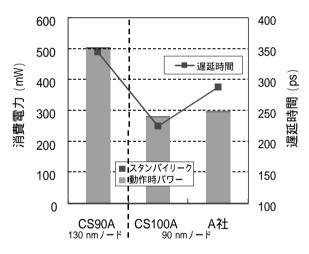

図-5は性能(遅延時間)と消費電力のベンチマーク結果である。CS90Aは,前世代の130 nmテクノロジである。CS90Aで開発されたチップをCS100Aで作成した場合を想定して比較している。前世代からは消費電力,遅延時間ともに半減することが分かる。他社との比較では,消費電力においては,ほぼ同等であるが,遅延時間は約20%程度優位となっている。これはハイエンド向けCS100の開発で培われた技術を一部採用することによって低リークを維持しつつオン電流の大きいトランジスタを実現できているためで,富士通デバイスの差別化要素になっている。

配線層にもバリエーションを持たせた。コンシューマ商品においては、チップサイズの大きいものから小さいものまで商品によってまちまちである。そのため必要とされる層数も異なってくる。当然、廉価なチップを作るためには必要最低限の配線層数だけを積層することが大事であり、CS100Aでは7層~10層までの積み方を7種の組合せで可能としている。配線の要素技術はハイエンド向けCS100と

図-5 CS100A\_LLの消費電力と遅延時間比較 Fig.5-Chip-power and path-delay comparison.

同じであるが、この積層の仕方が変っている。とくに下層の狭ピッチ配線はCS100が4層に対してCS100Aは5層にした。これは、チップサイズ(ハイエンド商品より小さい)、性能要求(ハイエンド商品より緩い)、高集積化(狭ピッチ配線が多い方が優位)といったことを総合的に判断して決めている。

## 1.14 µm²のSRAMメモリセル

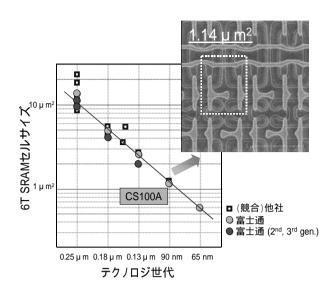

半導体開発の使命である「高集積・小チップ化」はコスト、性能、消費電力の面で優位になるが、その重要なかぎを握る技術としてSRAMメモリセルの縮小化が挙げられる。

FUJITSU.55, 3, (05,2004)

図-6 SRAMセルサイズのロードマップ Fig.6- SRAM cell size roadmap.

図-6は,富士通SRAMメモリセルの微細化トレンドである。他社ベンチマークなどの結果から90 nm CMOS世代の初期量産では,1.2 μm²前後が一般的であるが,富士通のメモリセルは1.14 μm²まで縮小化し量産レベルまで技術確立できている。ただし,メモリセル縮小化の競争は著しく,学会などでは1 μm²以下のメモリセルも報告され始め,優位性を維持するために更なる縮小化を目指して開発を継続している。

## む す び

90 nm CMOSテクノロジとして,サーバなどの

ハイエンド向けテクノロジCS100と,携帯電話,デジタル家電などのコンシューマ市場向けのCS100Aについて紹介した。CS100は最先端のトランジスタ技術と配線技術を駆使し,世界トップレベルの高性能テクノロジとして量産技術を確立した。CS100Aは低消費電力から高速処理まで幅広い市場をカバーする技術として開発し,ユーザ選択の範囲を広げ,技術的にはCS100の技術を取り込みながら低消費電力,高性能の両立を図り,結果としてコストパフォーマンスに優れたテクノロジに仕上がった。

#### 参考文献

- (1) T. Maruyama: SPARC64 VI: Fujitsu's Next Generation Processor. Microprocessor Forum 2003.

- (2) Y. Kim et al.: Robust Process Integration of 0.78 µm<sup>2</sup> Embedded SRAM with NiSi Gate and Low- K Cu Interconnect for 90nm. Samsung, Symposium on VLSI Technology 2003, p.69-70.

- (3) S. Thompson et al .: A 90nm Logic Technology Featuring 50nm Strained Silicon Channel Transistors, 7 layers of Cu Interconnects, Low k ILD, and 1  $\mu$ m<sup>2</sup> SRAM Cell . Intel , IEDM 2002 03\_02 , p.61-64 .

- (4) C. C. Wu et al.: A 90-nm CMOS Device Technology with High-speed, General-purpose, and Low-leakage Transistors for System on Chip Applications. TSMC, IEDM 2002 03\_03, p.65-68.

192 FUJITSU.55, 3, (05,2004)