# 超高速CMOSインタフェース技術

# **Ultra-High-Speed CMOS Interface**

### あらまし

2.5 Gビット/秒以上の超高速でデータの送受信,データからのクロックリカバリを行う技術を紹介する。本技術の用途としては,LSIと光モジュールとのインタフェース,ボード上でのチップ間のインタフェース,バックプレーンを通してのボード間のインタフェースなどである。

本技術では特別なプロセスを要求しないCMOS回路のみで高データレートに対応が可能である。チャネルあたりの消費電力は約150 mWと小さいことも特長で,化合物半導体やSiGeデバイスを使用した場合に比べて大幅に消費電力を低減でき,単一チップ上で多数のチャネルを使用できる。またASICのマクロとしても使えるので,チップ上に多くのチャネルを集積でき,信号本数や消費電力の削減,パッケージコスト,ボードコストの削減などを実現でき,システムの高性能化,低価格化に対応が可能である。

さらに10 Gビット/秒以上の高データレート化 ,ソースシンクロナス対応などを進めている。

#### Abstract

This paper introduces an ultra-high-speed CMOS interface that can transmit data at speeds faster than 2.5 Gbps and execute clock recovery from data. It is used for interfacing between LSIs and optical modules, between LSIs on PC board, and between boards via a backplane. This interface can handle high data rates using only CMOS circuits. No special process options are required. The interface also features a low power consumption of approximately 150 mW per channel. Compared with interfaces that use compound semiconductors or SiGe devices, this CMOS interface has a significantly lower power consumption. In addition, multiple channels can be used on a single chip. Moreover, the CMOS interface can also be used as an ASIC macro, which enables multiple channels to be integrated onto a single chip and a reduction in power consumption, package and board costs, and the number of signals. As a result, high-performance, low-cost systems can be configured. Another development is now in progress to achieve source clock synchronization and data rates faster than 10 Gbps.

酒井敏昭(さかい としあき) 第一システムLSI事業部第一設計 部 所属 現在,高速インタフェース関連の 開発に従事。

後藤公太郎(ごとう こうたろう) システムLSI開発研究所第一開発 プロジェクト部 所属 現在,高速インタフェース関連の 研究に従事。

# まえがき

インターネットの急速なブロードバンド化(ADSL、光ファイバ、無線、ケーブルTVなど)に伴い、ネットワークやプロセッサに要求されるデータバンド幅が著しく高くなってきている。その増加の割合はいわゆる「ムーアの法則」で表される半導体のプロセステクノロジの進歩に伴う速度向上の割合をはるかに上回る。このようなネットワークの高速化に対応するためには、高速アナログ回路設計技術が必須である。

高データレート、多ビットでボード間・チップ間や光 モジュールとのインタフェースを行うことがシステムの 高性能化、低価格化のために重要になってくる。

本稿では、2.5 Gビット/秒(以下、bps)×16チャネル(以下、ch)=40 Gbpsのパラレルデータ転送速度を実現するCMOSインタフェース技術について報告する。

#### 開発の背景

チップ間などのインタフェースのデータバンド幅は, データバンド幅 = 動作周波数 × ビット幅 で表される。これを向上させるには動作周波数を上げる か,ビット幅を増やすかのいずれかが必要となる。ビッ ト幅を増やす方法は既に限界にきており,これ以上は物 理的にもコスト的にも現実的ではない。また動作周波数 を上げる場合に、PCIのような従来から使われているバ ス接続方式では200 MHz程度が限界とされ,これ以上の動作周波数ではポイント・ツー・ポイント接続方式でないと現実的には使用できない。

データを取り込むためには、データとクロックとを同 期させる必要があるが、動作周波数が上がると、グロー バルクロックではスキュー(データ同士あるいはデータ とクロックとの時間的なずれ)を抑えるのが困難になる。 このため、データに併走して同期したクロックを送る方 式 (ソースシンクロナスと呼ばれ, RapidIO, HyperTransportなどで使用されている) やデータにク ロックを重複させる方式(CDR:クロックデータリカ バリと呼ばれ、3GIO、InfiniBandなどで使用されてい る)が取られる。1 Gbps程度までは単純なソースシン クロナスでも機能するが、それ以上の周波数になると長 い距離を伝送するにはスキューを抑えるのが物理的にか なり難しくなり、高度な技術や高価な材料が要求される。 これ以上の周波数では、データ同士やデータとクロック との位相関係をそれほど考慮しなくても済むクロック データリカバリ方式が何らかの形で使われている(2)

#### インタフェース回路の概要

本インタフェース回路では、信号線あたり2.5 Gbps 以上のデータレートを実現するためにクロックデータリ カバリ方式を使用している。

本回路では低ジッタのクロックを生成するPLL (Phase Locked Loop) とフェーズインタポレータ,符

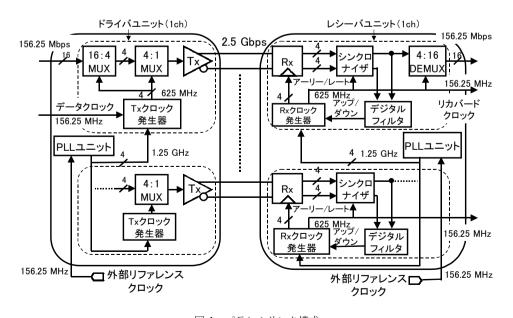

図-1 パラレルリンク構成 Fig.1-Parallel link block diagram.

号間干渉を除去するDPRD (Differential Partial Response Detector)レシーバ,十分なジッタトレランスを実現するデュアルループPLLによるCDRを使用している。

本回路は,PLLユニット,16chのドライバユニット, レシーバユニットで構成される(図-1)。ドライバの各 chは,156.25 Mbps×16ビットの入力データを16:1に MUX(multiplex) し2.5 Gbps×1ビットで送信する。レ シーバの各チャネルは,2.5 Gbpsのデータを受信し,1: 16にDEMUX(demultiplex)して156.25 Mbps×16ビットのデータを出力する。

各チャネルの基準クロック(1.25 GHz/4相)は,外 部リファレンスクロック156.25 MHzをPLLユニットの アナログPLLで逓倍し作られる。

SONET/OC-48規格では、レシーバのジッタトランスファ特性(カットオフ周波数120 kHz、ピークジッタ利得0.1 dB以下)とジッタトレランス特性(最大0/1連72ビット以上)とが要求される。2.5 GbpsでアナログPLLを使いCDRを実現するには、LPF(Low Pass Filter)のカットオフ周波数を120 kHzまで下げる必要がある。一方、カットオフ周波数を下げると、VCO(Voltage Controlled Oscillator)起因のノイズによるエラートランスファの帯域が広がり、出力クロックのジッタが増加する。したがって、アナログPLLのみではカットオフ周波数は約1 MHz程度までしか下げられない。対策としてレシーバの各チャネルにデジタルPLLを

搭載するデュアルループPLL方式を採用した。アナロ

グPLLとデジタルPLLのカットオフ周波数を独立に最適な値に決められ,カットオフ周波数をOC-48規格のジッタトレランスに合わせられる。入力データにジッタが入ってきても,デジタルフィルタで決まるカットオフ周波数によりフィルタリングされる。

#### 要素回路技術

アナログPLL

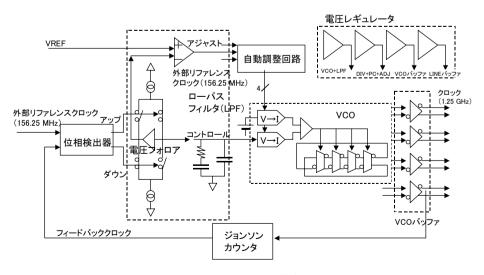

PLLは図-2に示すような構成になっている。外部リファレンスクロック (156.25 MHz) を逓倍し,1.25 GHz/4相のクロックを出力する。

本PLLでは,ジッタを抑えるためにVCOゲインを下げた状態で,中心周波数だけをコントロールし,サンプルに最適なゲインを選択する手段を採用した。

自動調整回路の入力はLPFの出力電圧,出力は4ビットのVCOのバイアス制御信号となる。同期は外部リファレンスクロックでとる。外部リファレンスクロックはPLLのロック時間よりも十分に遅いくらい(6~7µs)まで分周され,その速度でLPFの電圧と外部参照電圧(図中VREF)の逐次比較動作を行う。比較された結果は,LPFの出力電圧が外部参照電圧に近づくように,VCOバイアス電流を制御する。VCOのバイアス電流は発振レンジの中心でロックがかかるので自動調整回路を動かすと,4ビット分解能をもつVCOゲインから最適なゲインカーブが一つだけ選び出され,ロック外れしにくい,安定した動作が保証される。

VCOはpMOSシンメトリックロード型4段の回路に

図-2 PLLユニット構成 Fig.2-PLL unit block diagram.

なっている。シンメトリックロードを採用することにより,p-chロード部で線形性のよいI-Vカーブを得ることができ,VCOゲインの線形性が向上する。VCOのバイアス部はカレントミラーで構成されており,カレントミラーの電流量は自動調整回路の4ビットレジスタの値で制御される。

#### ドライバユニット

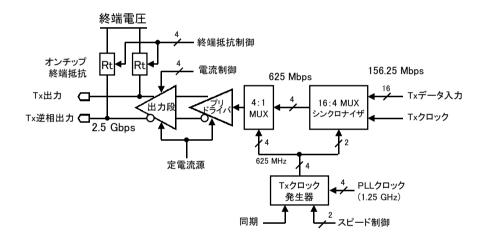

ドライバユニットは,Txクロック発生器,シンクロナイザ,4:1 MUX,プリドライバと出力段,オンチップ終端抵抗より構成される(図-3)。156.25 Mbps  $\times$  16 ビットの入力データは16:4 MUXで,外部クロックから内部クロックに乗り換える。4:1 MUXは,625 MHzの4相クロックに同期するラッチで構成される。

出力段回路はnMOS差動ペアの電流モード駆動型を用

いた。ロード部はpMOSのシンメトリックロードで,カレントステアリングロード兼終端抵抗である。出力電流は,nMOSカレントソース型DACで,4ビットのバイナリコードにより10~24 mA間で制御され,最小限の消費電流でレシーバ端における最適振幅が得られる。

#### レシーバユニット

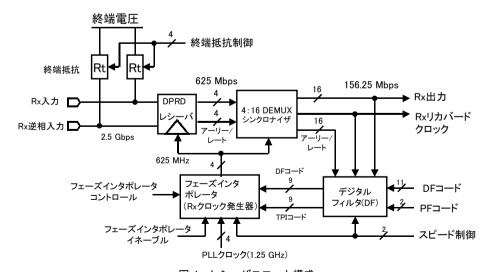

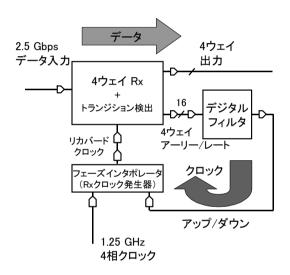

レシーバユニットは,DPRDレシーバ,シンクロナイザ,Rxクロック発生器フェーズインタポレータ,デジタルフィルタより構成される(図-4)。入力信号はオンチップ終端抵抗を通して,二つのDPRDレシーバに入力される。

DPRDレシーバはリカバードクロックを使用して,入 カデータとバウンダリデータ(アーリー/レート)をそれぞれ4ウェイのインタリーブで受信する。シンクロナ

図-3 ドライバユニット構成 Fig.3-Driver unit block diagram.

図-4 レシーバユニット構成 Fig.4-Receiver unit block diagram.

イザではこれらのデータを4:16にDEMUXし, 156.25 Mbps×16ビットのデータにする。これらのデータはデジタルフィルタの入力部にあるPDC (Phase to Digital Convert)回路でデータとクロックの位相量をデジタル値に変換する。デジタルフィルタはこの位相量をもとに,Rxリカバードクロックの位相調整信号(DF\_CODE,TPI\_CODE)を発生する。つぎにフェーズインタポレータがこの位相調整信号で制御された4相クロック(リカバードクロック)を生成する。

#### DPRDレシーバ

長いケーブルやプリント板のパターン,コネクタなどを通して高速データ転送を行うと,高周波口スのためにISI(Inter-Symbol Interference:符号間干渉)が発生する。このISIを除去する様々なイコライズ方式が提案されている。<sup>(3),(4)</sup> 本技術では,イコライズにPRD(Partial Response Detector)方式を採用している。信号線に重畳するコモンモードノイズをキャンセルするため差動型(DPRD)レシーバを用いた。

DPRDでは、レシーバ側で1次遅れの成分を取り除き ISIの除去を行う。 xを1以下の係数、Dを1ビットタイムのディレイ演算子とすれば、1ビット前のデータを差し引くことで、ISIの除去が可能となる(1-xD操作)。 複数のDPRDレシーバがインタリーブ動作することにより実質上レイテンシの増加はない。

フェーズインタポレータ(位相補間器,Rxクロック発生器)

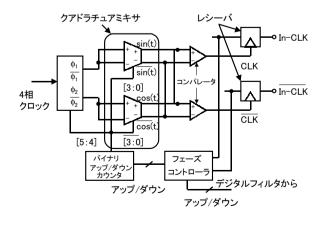

フェーズインタポレータは図-5に示すようにフェーズ コントローラ,6ビットバイナリアップ/ダウンカウンタ (UDC),クアドラチュアミキサ,コンパレータより構

図-5 フェーズインタポレータ構成 Fig.5-Phase interpolator block diagram.

成され,2 を6ビット分解能で位相制御し,クロックを出力する。クアドラチュアミキサの定電流ドライバはUDCで振幅制御された定電流クロックを出力し,この電流をキャパシタで積分して三角波の電圧波形を生成する。二つのクアドラチュアミキサには, /2位相差の入力クロックから2相の三角波が出力される。各位相の出力電流(係数y)は4ビットDACの出力電流値により制御され,二つのドライバ出力が接続されることで,出力電流が $y \times \cos(t) + (1-y) \times \sin(t)$ で加算される。yの値を変化させることにより任意の位相が出力できる。

位相検出には、入力クロックに対するエッジ検出方式を採用した。レシーバのラッチデータからフェーズインタポレータクロックと入力クロックの位相状態を判定し、UDCコードがカウントアップ/ダウンすることで出力クロックの位相制御を行う。

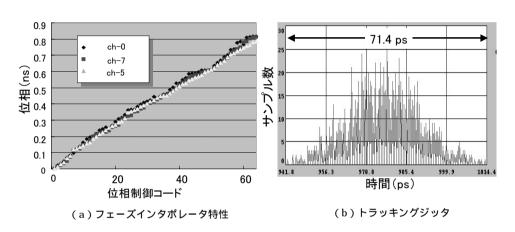

本技術では、1クロックサイクル(800 ps)を6ビットのバイナリコードで制御することにより、 $800 \text{ ps} \div 64 = 12.5 \text{ ps}$ の精度での位相制御が可能となる。

#### デジタルフィルタ

クロックリカバリのループ特性はデジタルフィルタによって制御される。デジタルフィルタは2次のループを構成しており,周波数オフセット積分回路におけるゲイン要素,位相積分回路のゲイン要素の調整により,ループのカットオフ周波数を制御することができる。フィルタの入力は,16ビットのデータと16ビットのバウンダリ(アーリー/レート)からなる。外部から入力されたクロックと内部クロックの位相差は,それぞれのクロックの遷移か所で計算され,アップ/ダウン信号としてフェーズインタポレータのミキサ部の電流量をコントロールする。フィルタのクロックは,フェーズインタポレータで生成された625 MHzのリカバードクロックを4分周して入力している。データのダイナミックな位相変化にもトラッキングできる特性を確保している(図-6)。

#### テストチップ

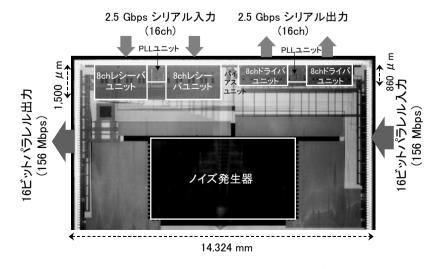

0.18  $\mu$ m標準CMOSプロセスによって作成した2.5 Gbps × 16chのパラレルテストチップを図-7に示す。テストチップは,ドライバユニット,レシーバユニット,バイアスユニット,雑音解析のためのノイズジェネレータから構成される。ドライバ,レシーバの面積はそれぞれ $0.86 \times 6.00 \ \mathrm{mm}^2$ , $1.50 \times 6.00 \ \mathrm{mm}^2$ である。標準電源電圧 $1.8 \ \mathrm{V}/3.3 \ \mathrm{V}$ での消費電力は $16\mathrm{ch}$ 全動作, $2.5 \ \mathrm{Gbps}$ 時で約 $2.5 \ \mathrm{W}$ である。

#### 評 価 結 果

このテストチップをループバック評価 (ドライバの出力を同じチップのレシーバに外部で接続しデータの送受信を確認する方法) した結果ビットエラーレートが $1 \times 10^{-15}$ 以下であることを確認した (121時間エラーなし)

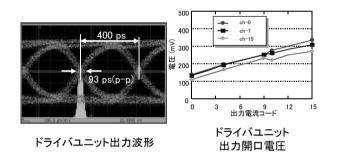

ドライバ出力のアイパターンと出力制御4ビットコードによる出力振幅変化のグラフを図-8に示す。ジッタはp-p(peak to peak)で93 psであり、データアイの十分な開きが確認できる。またアイの開口電圧は最大300 mV(シングルエンド)を測定ボード端で確保できバックプレーン伝送にも使用できる。

PLLは800 MHz~1.7 GHzまでの広い発振レンジを,

図-6 クロックリカバリ構成 Fig.6-Clock recovery block diagram.

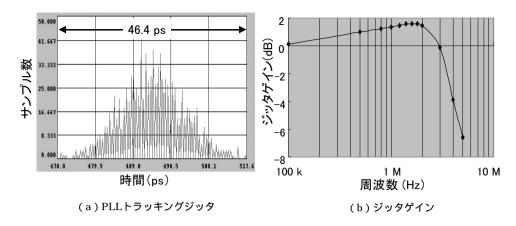

低いVCOゲイン(約350 MHz/V)でカバーした。PLLのトラッキングジッタは46.4 ps (p-p),カットオフ周波数は約3.5 MHz,ピークジッタゲインは約1.5 dBである(図-9)。これによりPLLのVCOノイズを少なくし、ジッタトランスファも良い特性を出せるような設計値を実現している。この値はリカバードクロックシステムとは関係ない(リカバードクロックシステムのカットオフ周波数とピークジッタゲインはデジタルフィルタで決まってくる)。

CDRのジッタはフェーズインタポレータのステップ  $\pm 1$ ビット分のデジタルノイズ25 psとPLLのジッタを 含んで,71.4 ps (p-p) である。フェーズインタポレータは良好な線形性を示している(図-10)

## むすび

バックプレーン向けの高速データ転送を実現する CMOSインタフェースを開発した。低ジッタ,高精度

図-8 2.5 Gbpsドライバユニット出力 Fig.8-2.5 Gbps driver unit output.

図-7 2.5 Gbps × 16chパラレルテストチップ Fig.7-2.5 Gbps × 16ch parallel test chip.

図-9 PLL特性 Fig.9-PLL characteristics.

図-10 フェーズインタポレータ, CDR特性 Fig.10-Phase interpolator and CDR characteristics.

のデータサンプリングクロックを生成するPLLとフェーズインタポレータ,低レイテンシでケーブルの高周波ロスによりISIを除去するDPRDレシーバ,またSONET/OC-48規格のジッタトレランスを実現するデュアルループPLLによるCDR回路を開発することにより,2.5 Gbpsの高速データを低レイテンシで転送することが可能となる。0.18 μ m標準CMOSプロセスにより,作成したテストチップにおいて,2.5 Gbps×16chのデータ転送を確認した。

今後はソースシンクロナス (OIF SFI-5など)への対応,5 Gbps~12.8 Gbpsへの高速化を進めていく。

#### 参考文献

- (1) 枝洋樹ほか:バスよりシリアルGHz伝送への決断.日経エレクトロニクス, No.798, p.101-127 (2001).

- (2) 姫野明ほか: DWDM用光デバイスの研究開発動向.電子情報通信学会誌, Vol.82, No.7, p.713-717 (1999).

- (3) W. Dally et al.: Transmitter Equalization for 4Gb/s signaling. Proceedings of Hot Interconnets IV, p.29-39 (1996).

- (4) R. Gu et al.: A 0.5-3.5Gb/s Low Power Low Jitter Serial Data CMOS Transceiver . ISSCC Digest of Technical Papers , p.352-353 (1999).

- (5) H. Tamura et al.: Partial Response Detection Technique for Driver Power Reduction in High-Speed Memory-to-Processor Communications . ISSCC Digest of Technical Papers , p.342-343 (1997).

- (6) K. Gotoh et al.: A 2B Parallel 1.25Gb/s Interconnect I/O Interface with Self-Configurable Link and Plesiochronous Clocking . ISSCC Digest of Technical Papers , p.156-157 (1999).

- (7) T. Lee et al.: A 2.5V CMOS delay-locked loop for an 18Mbit , 500MB/s DRAM . IEEE J. Solid-State Circuits , vol.29 , p.1491-1496 ( 1994 ) .