# 次世代LSIを支える材料技術

# **Material Technology for Creating Next Generation LSIs**

#### あらまし

情報機器の処理速度の向上を支えるCMOSデバイスの高速化は年々伸展し,21世紀には1GHz以上のクロック周波数が汎用デバイスで実現されようとしている。富士通研究所では,この高速化を支える材料として,微細加工用レジスト材料と多層配線に用いるための低誘電率層間絶縁材料の開発を進めている。レジスト材料では,0.15 μ mの解像能力をもつArF(フッ化アルゴン)エキシマレーザ用レジストの開発,そして層間絶縁材料では,3.0以下の低い比誘電率を持つ材料(HSQ:水素シルセスキオキサン)の製品適用に世界に先駆けて成功した。本稿では,これら0.18 μ m 以降の次世代LSIのために開発したレジスト材料技術および層間絶縁材料技術について紹介し,さらに今後の展望について述べる。

#### **Abstract**

The steady increase in the speed of information processing devices is largely due to the everincreasing operating speeds of CMOS LSIs. At the beginning of the 21st century, operating frequencies exceeding 1 GHz will become possible in commercially available LSIs for personal use.

Fujitsu Laboratories Ltd. has been developing resist materials for microlithography and low-dielectric materials for insulation in multi-level interconnections. We believe that these materials are the key technologies for supporting the high operating speeds mentioned above. We have developed a new resist material for the ArF eximer laser lithography which can resolve a pattern of 0.15  $\mu m$  lines and spaces. We have also become the first in the world to produce a product using the insulation material, Hydrogen Silsesqui Oxane ( HSQ ) which has a relative dielectric constant of 3.0 or less.

This paper introduces resist and insulator technologies developed for next generation LSIs that have a resolving power better than 0.18  $\mu m$  and describes the future prospects of these technologies.

究部

矢野 映(やの えい)

1985年北海道大学大学院理学研究科博士課程了。同年(株)富士通研究所 人社。以来、光反応性材料、半導体散 個加工用レジスト材料の研究に従事。 フォトポリマーコンファレンス実行委員,高分子学会光反応・電子用材料研 究会委員。1996年The Photopolymer Science and Technology Award受賞。 材料技術研究所無機・高分子材料研 究部

福山俊一(ふくやま しゅんいち)

1983年横浜国立大学工学部応用化学 科卒。同年(株)富士通研究所入社。 以来半導体用層間絶縁材料の開発に 従事。 材料技術研究所無機・高分子材料研

朽網道徳(くたみ みちのり)

1978年東京都立大学工学研究料電子 工学修士課程了。同年(株)富士通研 究所入社。以来ブリンタデバイス材 料技術,LSI用材料技術の研究開発に 従事。 材料技術研究所無機・高分子材料研

# まえがき

大型コンピュータから携帯電話まで,情報機器の処理 速度は年々目を見張る勢いで速くなっている。この情報 機器の高速化は、CMOSデバイスの高速化に支えられ、 1990年初め100 MHz以下であったCMOSのクロック周波 数は,1998年には500 MHzを超え,さらに21世紀に入る と,1GHz以上の周波数が汎用デバイスにおいて実現さ れようとしている。高速化を実現するためには、これま での微細加工技術によりトランジスタを小さくし,ゲー トのスイッチング時間を短くする方法に加えて、最近で は,微細化により逆に問題となってくる配線遅延を抑え るため,低抵抗配線技術や低誘電率層間絶縁材料技術が 重要になっている。富士通研究所では,このCMOSの高 速化を実現するために、微細加工用のレジスト材料と多 層配線に用いるための低誘電率層間絶縁材料の開発をLSI 用材料の二つの柱として進めてきた。ここでは,0.18 µ m 以降の次世代LSIデバイスへの適用を目指して開発した ArF(フッ化アルゴン)エキシマレーザ用レジスト材料と比 誘電率3.0以下の低い誘電率をもつHSQ(水素シルセスキ オキサン)層間絶縁材料について紹介するとともに,今後 の展望について述べる。

# ArF レジスト材料の開発

光リソグラフィにおいて,解像可能な最小の配線幅は,露光光源の波長に比例するため,LSIの高集積化,微細化に向けた露光光源の短波長化が進んでいる。

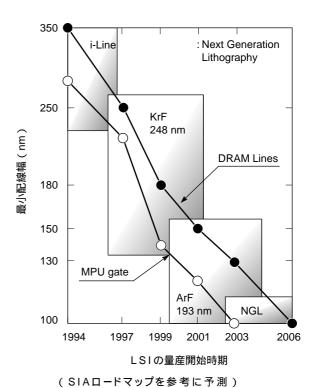

図-1に示すように、ここ数年で最先端リソグラフィの光源は水銀ランプのi線(露光波長365 nm)から,KrFエキシマレーザ(248 nm)となり,DRAMの配線幅で150 nm,MPUのゲート長で120 nmが要求される150 nm世代のLSIには,ArFエキシマレーザ(193 nm)が適用されると考えられる。さらに,最小配線幅が100 nm以下の世代に向けたリソグラフィ(NGL: Next Generation Lithography)として, $F_2$ エキシマレーザ(157 nm)や,等倍X線,電子線,極端紫外線(EUV: 13 nm)などの技術が有力候補と予想されている。

ここでは,これまでのi線,KrFエキシマレーザに代わり21世紀初頭に主流になると考えられるArFエキシマレーザリソグラフィの実用化に向け,世界に先駆けて開発した150 nmの解像力をもつArFレジスト材料について述べる。

ArFレジストの開発課題と基本コンセプト

レジスト材料に要求される基本特性としては,解像性,感度,ドライエッチング耐性の三つが挙げられる。

,

図-1 LSI**の微細化と露光技術** Fig.1-LSI microfabrication and lithography technology.

これまでに量産に適用されたi線やKrFレジストは,いずれも基材であるフェノール樹脂の,アルカリ現像液への高い溶解性と,樹脂中に含まれるベンゼン環の優れたドライエッチング耐性が,その性能を支える大きな要因となっていた。しかし,波長193 nmのArFエキシマレーザリソグラフィにおいては,フェノール系樹脂中のベンゼン環が193 nmに強い吸収を持つため,レジスト内部に露光光が届かず,全く新しい材料の開発が必要であった。今回開発したArFレジスト材料は,193 nmに対する高い透過率と,既存レジストと同等のドライエッチング耐性を持ち,かつ標準的に用いられているアルカリ現像液が適用可能な新しいレジスト材料である。

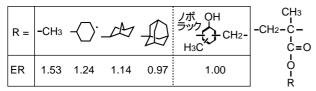

レジストの材料設計においては,透過率の確保が極めて重要であるが,従来のレジストで使用してきたノボラックやポリビニルフェノールは,193 nmのArFエキシマレーザを全く透過しない。193 nmを透過する樹脂としては,PMMAなどの飽和脂肪族系樹脂があるが,ドライエッチング耐性に乏しいことが実用上の大きな問題であった。富士通は,1992年に脂環族メタクリレート樹脂が,193 nmへの透過性と,ドライエッチング耐性を両立できることを見出した(1).(2) 図-2に示すように,側銭(図中のR)の異なるメタクリレート樹脂のドライエッチング耐性は,基準として示したノボラックなどの芳香族系樹脂

:フッ素系プラズマに対する相対エッチング速度(ノボラック基準)

#### 図-2 メタクリレート樹脂のドライエッチング耐性 Fig.2-Dry etching resistance of methacrylate.

図-3 AdMA/tBMA共**重合体** Fig.3-AdMA/tBMA copolymer.

に比べて低い傾向にあるが,側鎖に環状構造を導入するとドライエッチング耐性は向上し,さらに環の数が増すほど,耐性は高くなる。

以上の結果に基づき、最もドライエッチング耐性に優れたアダマンチルメタクリレート(AdMA)と、KrFレジストの反応性基として広く用いられているt-ブチルメタクリレート(tBMA)の共重合体の組み合わせをレジストの基本構造として採用した。構造を図-3に示す。分子内に共役系の二重結合がないため、193 nmに対して実用上十分な透過率(樹脂として1 μm膜厚で約70%)を示し、ArF化学増幅型ポジレジストとして機能することが確認された。

高性能化に向けた樹脂分子の改良

AdMA/tBMA共**重合体を基材とするレジストは**,実用 **化の上で以下のような課題があった**<sup>(3). (4)</sup>

- (1) 標準的なアルカリ現像液(2.38 wt% 水酸化テトラメ チルアンモニウム: TMAH水溶液 が使用できない。

- (2) 基板への密着性に乏しいため,200 nm以下の微細パターンの形成ができない。

標準現像液が使用できない原因は、露光後にも反応しないで樹脂中に存在する疎水性のアダマンチル基が、アルカリ現像液への溶解性を阻害することであると考えられた。アダマンチル基に反応性を付与し、露光時に脱離して樹脂中のアダマンチル基の量を減少させることがで

図-4 MAdMA/MLMA共**重合体** Fig.4-MAdMA/MLMA copolymer.

きれば、標準現像液への溶解性を改善できると考え、樹脂の分子構造の見直しを行った。炭素が3原子結合した3級の炭素は、安定な反応中間体を形成しやすく、反応性が高いことが知られている。そこで、アダマンチル基にメチル基を導入し、樹脂骨格と結合する炭素を3級化することでアダマンチル基に反応性を付与することを試みた。メチル基を導入した2・メチルアダマンチル基(MAdMA)は、露光後、脱離して酸性のカルボン酸を生成することが確認され、当初の目的どおり標準現像液への溶解性を著しく改善することができた。⑤

基板への密着性が不足する原因については、樹脂側鎖のアダマンチル基とt・ブチル基が、ともに双極子モーメントの値が2.0 Debye以下と強い疎水性を示し、さらに結晶性が強く柔軟性に欠けるためであると考えられた。t・ブチルに変わる極性の高い側鎖の探索を行った結果、反応性の3級炭素を持ち、強い電子吸引性を持つ酸素を含むため、双極子モーメントの値が約3.5 Debyeと極性の高いメバロニックラクトン(MLMA)が、密着性の改善に極めて有効であることが明らかになった。

以上の結果に基づき合成されたMAdMA/MLMA共**重**合体の化学構造を図-4に示す。

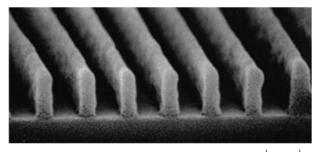

ArFレジストの特性

開発したArFエキシマレーザレジストの150 nm L&S現像パターンを図-5に示す。このパターンは開口数(NA)= 0.55のNikon製ArFエキシマレーザマイクロステッパにより得られたものである。このレジストは,露光装置の限界に相当する150 nmの解像性,10 mJ/cm²以上の実用上十分な感度,KrFエキシマレーザレジストと同等のドライエッチング耐性,さらに汎用アルカリ現像液が適用可能な優れたプロセス適合性を達成した。

今後は量産適用に向けて、材料の大量合成技術の確立

200 nm

図-5 開発レジストの性能 150 nm Line & Space )

Fig.5-Performance of developed resist 150 nm Line & Space )

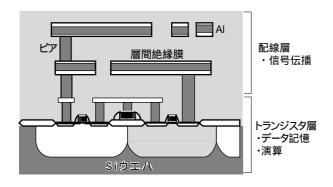

図-6 LSI断面の模式図 Fig.6-Structure of LSI.

を進めるとともに,プロセスからの要求に合わせて材料 の合せ込みを進めていく。

#### 層間絶縁材料の開発

LSI断面の模式図を図-6に示す。LSIは,トランジスタ層と配線層から構成されており,層間絶縁材料は配線層で配線間の絶縁を行うために使用される材料である。配線の配置が複雑になると配線層を上に重ねていく多層配線を用いる。これを実現するためには,配線によって生じた凹凸を絶縁膜により平坦にする必要がある。さらに,上下配線の間隔に比べて同層に配置された配線の間隔が狭くなるゲート長0.18μm世代以降では,配線間の絶縁膜に電荷がたまり易くなることで容量が増大し,配線層を電気信号が伝わる時間を表す配線遅延が増加してLSIの高速化の障害となっている。この障害を取り除くには,絶縁層に電荷の蓄積を少なく抑えられる誘電率の低い材料を適用する必要がある。

したがって,これからの多層配線中に用いられる層間 絶縁材料には,

(1) 配線間の半導体製造プロセスで用いられる高温 (400 以上)の熱処理に耐え得る耐熱性,

表-1 低誘電率化のトレンド

| 出荷時期 (年) | テクノロジ(μm) | 要求値( ) |

|----------|-----------|--------|

| 1997     | 0.25      | 3.5    |

| 1999     | 0.18      | 3.0    |

| 2001     | 0.15      | 2.7    |

| 2003     | 0.13      | 2.5    |

| 2006     | 0.10      | ~2.0   |

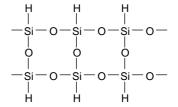

図-7 水素シルセスキオキサン( HSQ )の分子構造 Fig.7-Molecular structure of HSQ.

- (2) 配線が形成された段差基板上に配線層を重ねて形成 するための平坦性,

- (3) 配線間の容量を小さく抑えられる低誘電率化のすべてを満足することが要求される。従来,層間絶縁材料には高耐熱性のSiO2が用いられてきた。しかし,富士通ではSiO2系材料で平坦化が困難となった0.5 μ mから0.35 μ mの世代にかけて耐熱性,平坦性に優れた新しいポリシラザン系材料<sup>(8)</sup>を開発しデバイスに適用した。さらに,0.25 μ m世代以降になると低誘電率化が開発のポイントになっている。各世代のLSIで要求される絶縁材料の誘電率を表-1に示す。トランジスタの微細化とともに配線間隔が狭くなるため,容量の増加を防ぐには0.25 μ m世代で比誘電率3.5 , 0.18 μ m世代で3.0 , 0.13 μ m世代で2.5 , さらに0.10 μ m世代になると2.0以下の低い比誘電率が必要になってくる。

#### 低誘電率材料HSQの開発

0.18 µ m以降の次世代デバイスでは,比誘電率として3.0以下が必要となる。この比誘電率を実現するために,耐熱性,平坦性に優れ,また材料自身の誘電率が低い水素シルセスキオキサン(HSQ)をベースに,この材料を低誘電率層間絶縁材料として利用する技術を開発した。

HSQの分子構造を図-7に示す。HSQは,梯子型のシロキサン骨格を有し,各Siに1個の水素が結合した構造となっている。骨格構造はシロキサンからなり,耐熱性が400 以上と高いことが特徴の一つである。また,HSQは有機溶剤に可溶であり,基板を高速回転することで均一

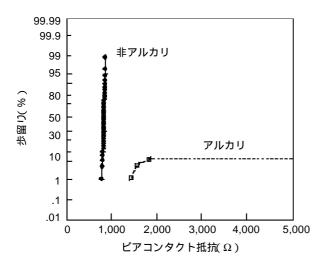

図-8 洗浄液と歩留りとの関係 Fig.8-Probability with different wet cleaning.

な膜が得られるスピンコート法により成膜でき、さらに 200 から300 で熱処理することにより、溶融し、流動性が良くなることから、平坦化に適した材料である。さらに、HSQは対称性の高い分子構造とSiO2に比べて密度が低い膜が得られるという特徴を持ち、材料本来の誘電率は3.0以下の材料である。しかし、LSIの多層配線を形成するプロセスでHSQの水素が酸化や加水分解を受けて、SiO2に近い分子構造に変わると、膜の疎水性が失われ、水(比誘電率80以上)を吸収しやすい膜となり、結果として誘電率が高くなってしまう問題があった。そこで、水素の多層配線プロセスでの減少を防ぎHSQ本来の材料物性を引き出すために、

- (1) HSQを熱処理して焼き固める工程で酸化を抑えられる熱処理条件の開発,

- (2) HSQの加水分解の原因となる従来のアルカリ洗浄を 用いない新しい多層配線プロセスの開発

を行い、全プロセスをとおして比誘電率3.0以下に維持できる技術を確立した。また、この技術は実用化にあたって問題となる上下配線を繋いだときの抵抗(ピアコンタクト抵抗)が上昇する現象を防止する効果がある。非アルカリの洗浄を適用した場合の100万個の連続したピアを有する配線の歩留りを図-8に示す。この結果から、洗浄液を変えることで、歩留りを大きく改善できることが分かる。

#### HSQ層間絶縁材料の特性

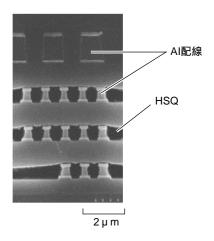

HSQを用いて試作した多層配線の断面を図-9に示す。 平坦化に優れたHSQを用いることで配線によって生じた 段差を均一に埋めることができている。また,高速化へ の寄与については,富士通のゲート長0.22 μ m ロジック LSIの多層配線に比誘電率3.0のHSQプロセスを適用する

図-9 HSQ**を用いた多層配線の断面写真** Fig.9-Cross-sectional view of multi-layer with HSQ.

ことで,従来のSiO(に) 比誘電率4.2 を適用したデバイスに 比べて配線遅延を最大20%低く抑えられることが確認で きた。

現在,富士通では,今回開発したHSQ材料技術を,携帯電話などに用いられているフラッシュメモリや最先端 CMOSデバイスの層間絶縁膜に採用している。

#### 今後の展望

#### レジスト材料

次世代以降のフォトリソグラフィ技術の候補として 種々の技術が検討されている。現状のKrFエキシマレーザ 技術,次世代のArFエキシマレーザ技術以降のリソグラ フィとしては,光リソグラフィの延長上にある波長157 nm のF。エキシマレーザ技術、解像度が高くデバイスの先行 開発やマスク製造において、すでに実績のある電子線プ ロセス・レジストの透過率の問題がなく現状の電子線用 レジストでも高い解像度が得られている等倍X線技術, さらに70 nm以下の超微細配線を形成できる唯一の技術で あり,米国を中心に開発が行われている波長13 nmのEUV 技術が挙げられる。しかし,いずれの技術も,装置や材 料などについては、まだ基礎検討の段階であり、量産技 術として立ち上げるには, さらに時間を要すると考えら れる。以上のような背景から100 nmレベルのデバイス製 造まで, ArFリソグラフィを延命する必要があると予想さ れ、今回の材料のさらなる高性能化に加えて、位相シフ トマスクなどの超解像技術に対して最適化されたネガレ ジストや、表面イメージングプロセスの開発が重要に なってくると考えられる。

#### 層間絶縁材料

0.13 µ m以降の将来の世代に向けて, さらに低い誘電率

の層間絶縁材料が必要となるが、材料そのものの低誘電率化以外に、見掛けの誘電率を下げる技術の一つとしては、絶縁膜中に空洞を設ける方法がある(空気の比誘電率約1を利用)。例えば、直径数十nmのSiO2微粒子を並べてその粒子間にできる隙間を利用した材料(9)、(10)がその一つの方法である。この構造では、一般に誘電率は、粒子径を大きくすると下がるものの、密着性や膜強度が低下する。この課題を改善して、膜強度と低誘電率の材料の実現が期待される。

一方で、配線材料は、AIから低抵抗のCuへ移行しようとしている。(\*1)、(\*12) そのため、将来の層間絶縁材料は、低い誘電率を追求するだけでなく、このCu配線との整合性も重要となってくる。比誘電率3.0以下で配線材料のCuが絶縁層に拡散することを防止できる材料としてポリアリルエーテル系の材料(\*13)などが有望であり、今後の開発が期待されるところである。

# む す び

次世代の高速CMOSロジックLSI用に開発したArFレジスト材料と比誘電率3.0をもつ層間絶縁材料であるHSQについて紹介した。今後もLSIの高速化は,微細加工技術によるトランジスタの縮小と新たな低誘電率層間絶縁材料技術やCu配線技術による配線遅延の低減により支えられる。そのため,これらLSI要素材料の開発は,新しい世代にとってますます重要となってくる。デバイスの要求性能を実現するためには,多くの材料的課題があるが,21世紀の超高速LSIの実現に向けて,今後も先端材料の開発を進めていく。

## 参考文献

- (1) S. Takechi et al.: Alicyclic Polymer for ArF and KrF Excimer Laser Resist Based on Chemical Amplification. J. Photopolym. Sci. Technol., 5, 3, pp.439-445 (1992).

- (2) Y. Kaimoto et al.: Alicyclic Polymer for ArF and KrF

- Excimer Resist Based on Chemical Amplification. Proc. SPIE , 1672 , 1992 , pp.66-73.

- (3) K. Nozaki et al.: Molecular Design and Synthesis of 3-Oxocyclohexyl Methacrylate for ArF and KrF Excimer Laser Resist. Chem. Mater., 6, 9, pp.1492-1498 (1994).

- (4) M. Takahashi et al.: Lithographic Characteristics of Alicyclic Polymer Based ArF Single Layer Resists. J. Photopolym. Sci. Technol., 7, 1, pp.31-39(1994)

- (5) K. Nozaki et al.: A New Single-Layer Resist for 193-nm Lithography. Jpn. J. Appl. Phys., 35, Pt.2, pp.L528-530(1996)

- (6) K. Endo et al.: Low-k Fluorinated Amorphous Carbon for ULSI Multilevel Interconnection. Dielectrics for ULSI Multilevel Interconnections Conference, pp.40-49(1999)

- (7) W. Volksen: Characterization and processing Considerations for Methylsilsesquioxane based Dielectrics. Dielectrics for ULSI Multilevel Interconnections Conference, pp.83-90(1999)

- (8) K. Nagashima et al.: SOG Non-Etch-Back Process Using Perhydrosilazane for Half-Micron Devices. VLSI Multilevel Interconnections Conference, p.217(1993).

- (9) A. Nakashima et al.: Development of a Novel Low-k( <2.5) Hydrophobic Porous SOG. Dielectrics for ULSI Multilevel Interconnections Conference, pp.303-309(1997).

- (10) A. Nakashima et al.: Low Dielectric Constant Porous SOG Material. Dielectrics for ULSI Multilevel Interconnections Conference, pp.25-31(1998)

- (11) K. Ikeda et al.: Integration of Organic Low-k Material with Cu-Damascene Employing Novel Process. International Interconnect Tecnology Conference, pp.131-133(1998)

- (12) S. Venkatesan et al.: A High Performance 1.8V, 0.20 µm CMOS Technology with copper Metallization. International Electron Devices Meeting, pp.769-772(1997)

- (13) D. Edelstein et al.: Full Copper Wiring In a Sub-0.25 µ m CMOS ULSI Technology. International Electron Devices Meeting, pp.773-776(1997).