# サプ0.1 µm CMOS技術

# CMOS Scaling beyond 0.1 µm

#### あらまし

LSIは市場の要求から,サブ0.1 µm世代に向けて急速なデバイスの微細化と低電圧化 が行われている。トランジスタを微細ゲート長で正常に動作させること,そして低電圧 においても微細ゲート長に見合った高性能を実現することが開発の基本目標である。

本稿は、この目標に向けて行ったトランジスタ設計指針の検討と実験結果について述 べる。検討した内容は低しきい値化、短チャネル効果抑制と寄生抵抗および寄生容量の 低減技術である。これらの検討の結果,基本ゲート遅延時間で11 ps/ゲートの超高速性 能を実現できた。この動作速度は、これまでに報告されたSOIデバイスを含む微細 CMOSの中でもトップレベルの性能である。

#### Abstract

To meet the market's demand for LSIs with even higher performances, device scaling and reduced power supply voltages have been aggressively pursued in order to develop sub-0.1 micron CMOS devices. The main goals of the new technologies that have been developed are to enable CMOS devices to operate normally with shorter gates and to obtain a high performance from these shorter gates even at a low voltage.

This paper describes a new CMOS device that meets the above goals and describes some of its experimental results. The new CMOS device incorporates technologies for threshold voltage reduction, short-channel effect suppression, parasitic resistance reduction, and parasitic capacitance reduction. Experiments have shown that this device has an ultra-fast gate delay of 11 ps, which is very competitive with already reported CMOS devices such as SOI CMOS devices.

杉井寿博(すぎい としひろ)

1981年東京工業大学総合理工学研究 科卒。同年(株)富士通研究所入社。 以来半導体デバイス,プロセスの研究,開発に従事。1991年東京工業大 学より学位を授与される。 基盤技術研究所機能デバイス研究部

後藤賢一(ごとう けんいち)

1991年東北大学工学部電子工学科卒。 同年(株)富士通研究所入社。以来, 微細CMOS用サリサイドプロセス 浅い接合の研究開発に従事。1998年

籾山陽一(もみやま よういち)

1992年新潟大学大学院工学研究科電 子工学専攻了。同年(株)富士通研究 所入社。以来微細CMOSデバイスの 研究 , 開発に従事。 基盤技術研究所機能デバイス研究部

# まえがき

飛躍的に増大する画像データの処理やネットワークを 介した高速通信の需要と,急拡大している各種携帯情報 機器の要請から、プロセッサやシステムLSIの低電源電圧 での高速性能の要求は今後ますます増大していく。今日 までLSIはスケーリング則により集積度,性能,コストを 飛躍的に向上させてきた。このLSIの進歩を制限してきた のは,従来は微細加工技術,とくにリソグラフィであっ たが,サブ0.1 µmに向けては制限要因がLSIの基本要素で あるトランジスタにまで広がる。これは,従来から高速 化,低消費電力化を阻害してきた寄生抵抗,寄生容量の 影響が微細化とともに増大するだけでなく、キャリアの 速度飽和によりオン電流が制限されたり、リーク電流の 増大のためにしきい値をスケーリングしにくくなること から,今まで我々がスケーリングにより享受してきた高 性能化が厳しい状況になりつつあるためである。これに 対処するため、従来のペースを上回る微細化と、SOI基板 やCu配線,低誘電率層間膜などの新規テクノロジの導入 が活発になっている。とくに,速度性能を決定するゲー ト長の微細化はここ数年加速してきている。(1) 1999年,半 導体各社から出荷され始める0.18 µ m世代のLSIには,ト ランジスタのゲート長が1世代分程度さらに縮小したもの を使用している場合が多い。研究, 開発レベルではその先 のサブ0.1 µmのゲート長がターゲットになりつつある。

このような状況の中,トランジスタおよびプロセス開発に要求されることは,急速なデバイススケーリングと低電圧化に対応できるテクノロジの提供である。トランジスタを微細ゲート長で正常に動作させること,そして低電圧においても微細ゲート長に見合った高性能を実現することが開発の基本目標である。

本稿では、サブ0.1 µm世代に要求される低電圧動作かつ高速性能化に対して、予想される課題の解決に向けてのトランジスタ設計指針と検討結果を述べる。

#### トランジスタの課題と設計指針

サブ $0.1 \mu m$ トランジスタを開発する上での基本指針は,低しき11値における短チャネル効果の抑制(オフ電流低減)と,高速化および低消費電力化を阻害する抵抗ならびに容量の低減である。

低しきい値化と短チャネル効果抑制

スケーリング則から,短チャネル効果の抑制にはトランジスタ内部の電界分布をスケーリングの前後で一定に保つ必要があり,電源電圧の低下だけでなく,トランジ

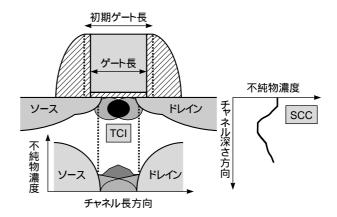

図-1 サブ0.1 μ m用に提案したチャネル不純物構造 Fig.1-Concept of channel engineering for sub-0.1 μ m MOSFETs.

スタのチャネル部の不純物濃度の増大が必要である。これはしきい値( \/\_\_,)が増大(逆スケーリング)することになり,トランジスタが流すことができる電流 {オン電流( \/\_\_, - \/\_\_, ), \/\_\_, : 電源電圧}の低下,したがって速度性能の低下を引き起こす。低しきい値化と短チャネル効果抑制のトレードオフを回避する必要がある。このため,チャネルの不純物分布を均一分布ではなく,2次元的に分布を設計する必要が生じてきた。これは,短チャネル効果の原因であるソース/ドレインのチャージシェアが2次元的に生じるためである。

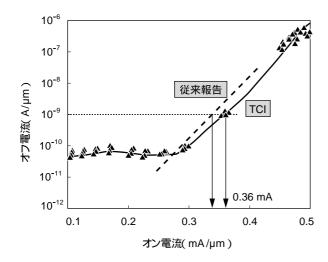

著者らが提案するチャネル部の二次元不純物分布の模 式図を図-1に示す(2) 単純にチャネル濃度を高くするのでは なく、短チャネル効果が現れる短いゲート長近傍でのみ チャネル濃度を高くする必要がある。このコンセプトを 実現するため,ゲート電極となるポリSiを加工後に,Si基 板に対して角度をつけてチャネルの不純物をイオン注入 するプロセス(TCI: Tilted Channel Implantation )を開発 した。このプロセスでチャージシェアによるしきい値低 下が顕著になるゲート長領域においてのみ、ゲート電極 の両側からの斜めチャネル注入のオーバラップにより チャネル不純物量を増やすことができる。低しきい値化 と短チャネル効果抑制を両立できる。この斜めチャネル 注入プロセスで試作を行ったPMOSFETのオン電流とオ フ電流の関係を図-2に示す。3 短チャネル効果を十分に抑 制したため,より短い実効チャネル長( └ผ : ソース ,ド レイン間の冶金学的距離)での動作が可能になり,オフ電 流 1 nA/μmにおけるオン電流は0.36 mA/μmが得られ, 最高性能を実現できた。

抵抗の低減

トランジスタの高性能化に大きく貢献するのが,トランジスタが流すことができるオン電流の増大である。こ

図-2 斜めチャネル注入プロセスで試作したPMOSFETのオン電流とオフ電流の関係

Fig.2-Ion-Ioff characteristics of PMOSFETs with tilted channel implantation.

れはトランジスタの抵抗を低減することにほかならない。抵抗はトランジスタの真性領域の抵抗(オン抵抗)と 真性部以外の抵抗(寄生抵抗)に分けることができる。

オン抵抗( $L_{eff}/C_{ox}$ ,  $C_{ox}$ : ゲート容量)低減には実効 ゲート長の短縮のほかに,ゲート酸化膜の薄膜化による チャネル部のキャリア数の増大を図ることが有効であ る。ゲート酸化膜の薄膜化は電源電圧の低下と適合する こと,また短チャネル効果抑制にも有効であることか ら,世代とともに指数関数的に行われてきた。0.13 µ mの 世代では3nm前後が予想されている。しかし,膜厚がこ れくらい薄くなると,ゲート電極の空乏化と反転層容量 の影響で電気的な実効膜厚が,物理的に薄くした割には 薄くならず、オン電流増大への寄与が小さくなる。さら に , 2 nm以下の膜厚が必要になるサブ0.1 μ m世代では , 電子がゲート酸化膜を直接トンネルすることによるオフ 電流が増大し、これまでSi-LSIの大規模化を支えてきたSi 酸化膜系のゲート絶縁膜のスケーリングは終焉を迎える 状況である。このため, それに代わる新しいゲート絶縁 膜の開発が急務である。その絶縁膜の物性には、Si基板 と電気的に良好な界面を有し、かつ高い誘電率であるこ とが要求される。

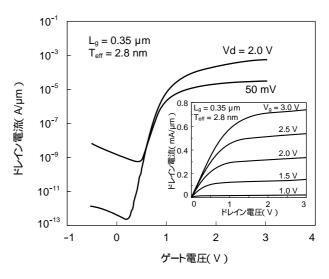

ゲート電極の空乏化とトンネル電流の増大に対処するため、高誘電率のタンタル酸化膜(Ta<sub>2</sub>O<sub>5</sub>)のゲート絶縁膜と、従来のポリSiに代わる窒化チタン(TiN)からなるメタルゲート電極を検討している。DRAMのキャパシタへの適用と異なり、トランジスタのゲート絶縁膜に用いるためには界面準位の低減が必要である。著者らはTa<sub>2</sub>O<sub>5</sub>堆積前に非常に薄いSi酸化膜(2.1 nm)を形成することで、ト

図-3 Ta<sub>2</sub>O<sub>5</sub>をゲート絶縁膜に用いたトランジスタのI-V特性 Fig.3-I-V characteristics of NMOSFETs with Ta<sub>2</sub>O<sub>5</sub> gate insulator.

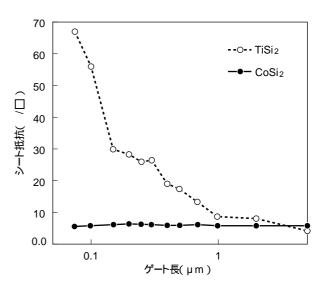

**図**4 コバルトおよびチタンシリサイドのシート抵抗のゲート長 依存

Fig.4-Gate sheet resistance of conventional Ti salicide and Co salicide as function of gate length.

#### ランジスタの正常動作を実現している(図-3)(4)

トランジスタの寄生抵抗は、前述のオン抵抗に対して無視できる大きさにすることが理想である。サブ0.1 µmのゲート長の場合、実効ゲート長は0.05 µm程度になり、そのときのオン抵抗は数百・µmになる。そのため、寄生抵抗の目標値は数十・µm以下である。寄生抵抗は、大きくソース/ドレイン部のコンタクト抵抗と、ソース/ドレイン部の拡張領域(エクステンション部)の抵抗に分けることができる。コンタクト抵抗を下げるためには、決められた素子面積でできるだけ広いコンタクト領域を確保できる、セルフアラインでシリサイド層を形成する

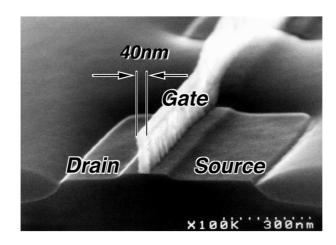

図-5 ゲート長40 nmのトランジスタの電子顕微鏡像 Fig.5-Cross-sectional SEM image of device with 40 nm gate length after side-wall removing.

サリサイドプロセスが必須である。またオン電流の大小には影響しないが、AC特性(回路特性)に大きな影響を与えるゲート抵抗の低減も必須で、サブ0.1 μ mのゲート長で数 / 以下にする必要がある。従来、サリサイド用の材料としてチタンシリサイド(TiSi₂)が用いられていたが、ゲートが細くなるとシート抵抗が上昇してしまう、いわゆる細線効果(図-4)が生じるため、サブ0.1 μ m世代での使用が困難であった。著者らはこの細線効果がないコバルトシリサイド(CoSi₂)をソース/ドレイン/ゲート上に、セルフアラインで一括して形成するサリサイドプロセスを開発し、サブ0.1 μ m世代への適用を可能にした。⑤

エクステンション部は低抵抗化が必要であるが,短 チャネル効果の抑制のために接合を深くすることはでき ない。高濃度でチャネル方向に急峻かつ領域を短くする 必要がある。サブ0.1 μ m世代ではエクステンション部を 浅くしないとチャネル部への不純物の回り込みが大きく なり,必要な実効ゲート長の確保が困難になる。著者ら は,浅い接合形成に関して特に形成が困難なPMOSにつ いて、その不純物であるボロンの実効的なイオン注入時 の加速エネルギーを, 従来の約1/10の200 eVにまで下げ ることにより,ゲート長40 nmで正常かつ高オン電流の実 現に成功した。回-5は試作したPMOSの電子顕微鏡像で ある。この浅い接合形成のために,従来のポロン単体の イオン注入と異なり、ボロン原子を塊(クラスタ)の状態 でイオン注入を行う技術を開発した。著者らが半導体プ ロセスに初めて用いたデカボラン(B10H14)の分子構造を 図-6に示す。このクラスタイオン注入の特徴は,

(1) クラスタのサイズに応じて,ボロン単体の場合と比べて実効的に低加速エネルギーのイオン注入が可能

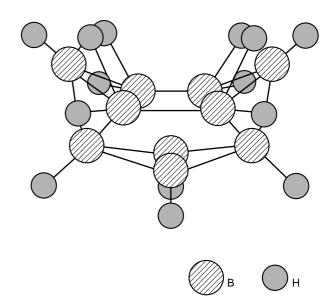

図-6 デカボラン(B<sub>10</sub>H<sub>14</sub>)の分子構造 Fig.6-Decaborane molecular structure.

で,デカボランの場合では1/10以下の実効加速エネル ギーとなる,

(2) 1価のイオンでクラスタサイズに応じた多数の原子を注入できるため、ボロンイオンに比べて低ドーズ量でよく、スループットの向上とチャージダメージを低減できる。

などである。

容量の低減

抵抗の場合と同様に、容量についても真性領域の容量 (ゲート容量)と真性部以外の容量(寄生容量)に分けるこ とができる。ゲート容量の低減はロジックゲートにおい て次段の入力容量の低減になり,高速化に大きく貢献す る。低減法はポリSiゲート長の微細化とゲート酸化膜の 厚膜化である。しかし、後者はオン抵抗の増大となるた め、現状は各社ともゲート長の微細化を加速しているわ けである。寄生容量はトランジスタにぶら下がる全く不 要の容量で、その充放電に費やす時間とエネルギーのた めに,速度低下と消費電力の増大を引き起こす。CMOS で回路を構成する場合,その動作上,ゲートとドレイン 間の容量がミラー効果のために2倍の影響力を持つた め、その低減が特に重要である。著者らは、ゲートとド レイン間の容量低減のために,ポリSiゲートを加工した 後、その側壁を酸化してからエクステンション部へのイ オン注入を行うことで,その容量の低減を実現している (図-1)(2) またサブスレショルド領域におけるオン電流の ゲート電圧依存(§値)を急峻にすることによるオフ電流の 低減と,低電圧での接合容量増大を抑制するために,基

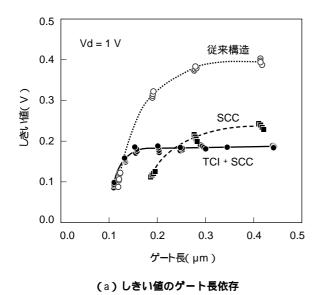

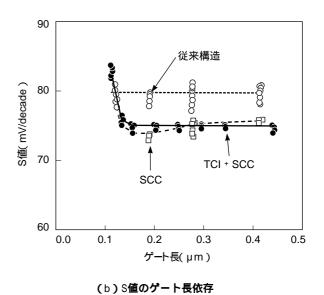

図-7 TCIとSCC構造を導入したNMOSFETのしきい値とS値のゲート長依存 Fig.7-Effects of TCI and SCC on Vth roll-off and S-factor.

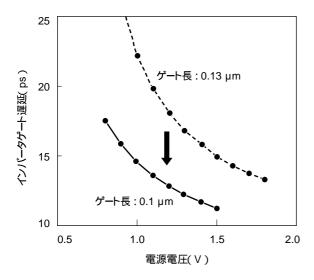

図-8 インパータゲート遅延時間の電源電圧依存 Fig.8-Propagation delay time for unloaded inverter ring oscillator with 0.13 µ m and 0.1 µ m gate length.

板表面にチャネル濃度のピークを形成すること(SCC: Surface Concentrated Channel)が低電圧動作のサブ0.1 μm世代では必要である。図-1にはその概念も示した。図-7は従来構造のトランジスタと、TCIとSCCを導入したトランジスタのしきい値とS値のゲート長依存である。低電圧で必要とされる低しきい値、短チャネル効果抑制、S値低減が実現できている。また、接合容量は従来チャネルと比べて16%低減できた。

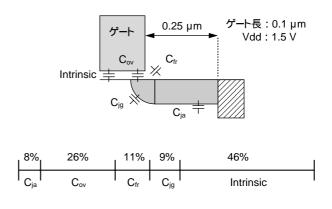

図-9 ゲート遅延時間の要素解析結果 Fig.9-Delay time classification of 0.1 μ m CMOS devices.

#### 回路性能

前述した低しきい値化,短チャネル効果抑制,低抵抗化,低容量化の技術を取り入れて,回路性能の評価を行った。図-8はインバータからなるリング発振器を試作してゲート遅延時間の電源電圧依存を評価した結果である。ゲート長を0.1 μ mにシュリンクすることで11 psの高速性能が電源電圧1.5 Vで得られた。この速度はこれまでに報告されたSOIデバイスを含む微細CMOSの中でもトップレベルの性能である。図-9にはこのゲート遅延時間の内訳を容量について解析した結果も示した。これからゲート容量の感度がまだ大きいことが分かり,さらにゲートの微細化を行えばいっそうの高性能化が実現でき

### ることが予想される。

# む す び

ゲート長0.1 μm, およびそれ以下での低電圧, 高速動作のための課題と,著者らが検討を続けているデバイス設計指針とその具体的実験結果について述べた。回路動作の評価から,サブ0.1 μmにゲートを微細化していくことで,CMOSゲートレベルではさらに高性能な特性が得られることを示した。このテクノロジにCu配線と低誘電率層間膜を組み合わせることで,システムレベルでの高性能,低消費電力化が可能と予想される。

#### 参考文献

- National Technology Road map for Semiconductor, 1997

Edition (SIA)

- (2) Y. Momiyama et al.: Channel Engineering of 0.13  $\mu$  m

- nMOSFET for 1.0 V CMOS Using Gate Poly-Si Oxidation and Laterally Profiled, Surface Concentrated Channel Technologies. Digest Tech. Papers Symp. VLSI Tech., p.78 (1998)

- (3) K. Goto et al.: A Study of Ultra Shallow Junction and Tilted Channel Implantation for High Performance 0.1 μ m pMOSFETs. Tech. Digest IEDM, p.631(1998).

- (4) Y. Momiyama et al.: Ultra-Thin Ta2O5/SiO2 Gate Insulator with TiN Gate Technology for 0.1  $\mu$  m MOSFETs. Digest Tech. Papers Symp. VLSI Tech., p.135(1997)

- (5) K. Goto et al.: Leakage Mechanism and Optimized Conditions of Co Salicide Process for Deep-Submicron CMOS Devices. Tech. Digest IEDM, p.449(1995)

- (6) K. Goto et al.: A High Performance 50 nm PMOSFET using Decaborane B10H14 Ion Implantation and 2-step Activation Annealing Process. Tech. Digest IEDM, p.471 1997 Inc.