# SPARC64<sup>TM</sup> IXfx Extensions

Fujitsu Limited

Ver 12, 2 Dec. 2013

Copyright© 2009-2013 Fujitsu Limited, 4-1-1 Kamikodanaka, Nakahara-ku, Kawasaki, 211-8588, Japan. All rights reserved.

This product and related documentation are protected by copyright and distributed under licenses restricting their use, copying, distribution, and decompilation. No part of this product or related documentation may be reproduced in any form by any means without prior written authorization of Fujitsu Limited and its licensors, if any.

The product(s) described in this book may be protected by one or more U.S. patents, foreign patents, or pending applications.

#### TRADEMARKS

SPARC® is a registered trademark of SPARC International, Inc. Products bearing SPARC trademarks are based on an architecture developed by Sun Microsystems, Inc.

SPARC64<sup>TM</sup> is a registered trademark of SPARC International, Inc., licensed exclusively to Fujitsu Limited.

Fujitsu and the Fujitsu logo are trademarks of Fujitsu Limited.

This publication is provided "as is" without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose, or noninfringement. This publication could include technical inaccuracies or typographical errors. Changes are periodically added to the information herein; these changes will be incorporated in new editions of the publication. Fujitsu Limited may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

# History

| Date       | Descriptions | Page |

|------------|--------------|------|

| 2013/12/02 | 第 12 版発行     |      |

Ver 12, 2 Dec. 2013

# Contents

1. Overview 1

|    | 1.1<br>1.2 | _        | ing the SPARC64™ IXfx Extensions 1<br>ad Notational Conventions 1 |

|----|------------|----------|-------------------------------------------------------------------|

| 2. | Defini     | itions 3 |                                                                   |

| 3. | Archi      | tectural | Overview 7                                                        |

|    | 3.1        | SPARC    | 54 IXfx プロセッサ 7                                                   |

|    |            | 3.1.1    | コア内部のコンポーネント 9                                                    |

|    |            | 3.1.2    | 命令制御ユニット (IU) 11                                                  |

|    |            | 3.1.3    | 命令実行ユニット(EU) 11                                                   |

|    |            | 3.1.4    | ストレージ制御ユニット(SU) 12                                                |

|    |            | 3.1.5    | 二次キャッシュユニット (SXU) 12                                              |

|    | 3.2        | プロセ      | ッサパイプライン 13                                                       |

|    |            | 3.2.1    | 命令フェッチステージ 13                                                     |

|    |            | 3.2.2    | 命令発行ステージ 15                                                       |

|    |            |          | 実行ステージ 15                                                         |

|    |            | 3.2.4    | 命令完了ステージ 16                                                       |

| 4. | Data l     | Formats  | 17                                                                |

| 5. | Regist     | ters 19  |                                                                   |

|    | 5.1        | Nonpriv  | rileged Registers 20                                              |

|    |            | 5.1.1    | General-Purpose r Registers 20                                    |

|    |            | 5.1.4    | Floating-Point Registers 20                                       |

|    |            |          |                                                                   |

Ver 12, 2 Dec. 2013 Contents i

- 5.1.7 Floating-Point State Register (FSR) 22

- 5.1.9 Tick (TICK) Register 25

- 5.2 Privileged Registers 25

- 5.2.6 Trap State (TSTATE) Register 25

- 5.2.9 Version (VER) Register 26

- 5.2.11 Ancillary State Registers (ASRs) 26

- 5.2.12 Registers Referenced Through ASIs 34

- 5.2.13 Floating-Point Deferred-Trap Queue (FQ) 38

- 5.2.14 IU Deferred-Trap Queue 38

#### 6. Instructions 39

- 6.1 Instruction Execution 39

- 6.1.1 Data Prefetch 39

- 6.1.2 Instruction Prefetch 40

- 6.1.3 Syncing Instructions 40

- 6.2 Instruction Formats and Fields 40

- 6.3 Instruction Categories 41

- 6.3.3 Control-Transfer Instructions (CTIs) 41

- 6.3.7 Floating-Point Operate (FPop) Instructions 42

- 6.3.8 Implementation-Dependent Instructions 42

#### 7. Traps 43

- 7.1 Processor States, Normal and Special Traps 43

- 7.1.1 RED state 43

- 7.1.2 error state 44

- 7.2 Trap Categories 44

- 7.2.2 Deferred Traps 44

- 7.2.4 Reset Traps 44

- 7.2.5 Uses of the Trap Categories 45

- 7.3 Trap Control 45

- 7.3.1 PIL Control 45

- 7.4 Trap-Table Entry Addresses 45

- 7.4.2 Trap Type (TT) 45

- 7.4.3 Trap Priorities 49

- 7.5 Trap Processing 49

- 7.6 Exception and Interrupt Descriptions 50

|    |        | 7.6.4 SPARC V9 Implementation-Dependent, Optional Traps That Are Mandatory in SPARC JPS1 50 |

|----|--------|---------------------------------------------------------------------------------------------|

|    |        | 7.6.5 SPARC JPS1 Implementation-Dependent Traps 51                                          |

| 8. | Memo   | ry Models 53                                                                                |

|    | 8.1    | Overview 54                                                                                 |

|    | 8.4    | SPARC V9 Memory Model 54                                                                    |

|    |        | 8.4.5 Mode Control 54                                                                       |

|    |        | 8.4.7 Synchronizing Instruction and Data Memory 54                                          |

| A. | Instru | ction Definitions 57                                                                        |

|    | A.4    | Block Load and Store Instructions (VIS I) 66                                                |

|    | A.9    | Call and Link 68                                                                            |

|    | A.24   | Implementation-Dependent Instructions 69                                                    |

|    |        | A.24.1 Floating-Point Multiply-Add/Subtract 70                                              |

|    |        | A.24.2 Suspend 76                                                                           |

|    |        | A.24.3 Sleep 77                                                                             |

|    |        | A.24.4 Integer Multiply-Add 78                                                              |

|    | A.25   | Jump and Link 80                                                                            |

|    | A.26   | Load Floating-Point 81                                                                      |

|    | A.27   | Load Floating-Point from Alternate Space 85                                                 |

|    | A.30   | Load Quadword, Atomic [Physical] 88                                                         |

|    | A.35   | Memory Barrier 90                                                                           |

|    | A.41   | No Operation 92                                                                             |

|    | A.42   | Partial Store (VIS I) 93                                                                    |

|    | A.48   | Population Count 94                                                                         |

|    | A.49   | Prefetch Data 95                                                                            |

|    | A.51   | Read State Register 97                                                                      |

|    | A.59   | SHUTDOWN (VIS I) 99                                                                         |

|    | A.61   | Store Floating-Point 100                                                                    |

|    | A.62   | Store Floating-Point into Alternate Space 104                                               |

|    | A.68   | Trap on Integer Condition Codes (Tcc) 107                                                   |

|    | A.69   | Write Privileged Register 108                                                               |

|    | A.70   | Write State Register 111                                                                    |

Traps Defined by SPARC V9 As Mandatory 50

SPARC V9 Optional Traps That Are Mandatory in SPARC JPS1 50

7.6.1

7.6.2

Ver 12, 2 Dec. 2013 Contents iii

| A.71 | Deprecated Instructions 113   |

|------|-------------------------------|

|      | A.71.10 Store Barrier 113     |

| A.72 | Floating-Point Conditional Co |

| A.73 | Floating-Point Minimum and I  |

| A.74 | Floating-Point Reciprocal App |

|      |                               |

- impare to Register 114

- Maximum 116

- proximation 118

- A.75 Move Selected Floating-Point Register on Floating-Point Register's Condition 122

- A.76 Floating-Point Trigonometric Functions 123

- A.77 Store Floating-Point Register on Register Condition

- A.78 Set XAR (SXAR) 131

- A.79 Cache Line Fill with Undetermined Values 133

#### B. IEEE Std. 754-1985 Requirements for SPARC-V9 139

- B.1 Traps Inhibiting Results 139

- B.6 Floating-Point Nonstandard Mode 139

- B.6.1 fp\_exception\_other Exception (ftt=unfinished\_FPop) 140

- B.6.2 Behavior when FSR.NS = 1 143

#### C. Implementation Dependencies 147

- C.4 List of Implementation Dependencies 147

- D. Formal Specification of the Memory Models 159

- E. Opcode Maps 161

#### F. Memory Management Unit 173

- F.1 Virtual Address Translation 173

- F.2 Translation Table Entry (TTE) 174

- F.4 Hardware Support for TSB Access 177

- F.5 Faults and Traps 178

- F.5.1 Trap Conditions for SIMD Load/Store 180

- F.5.2 Behavior on TLB Error 180

- F.8 Reset, Disable, and RED\_state Behavior 182

- F.10 Internal Registers and ASI Operations 183

- F.10.1 Accessing MMU Registers 183

- F.10.2 Context Registers 187

- F.10.3 Instruction/Data MMU TLB Tag Access Registers 191

|    |       | F.10.4    | I/D TLB Data In, Data Access, and Tag Read Registers 192              |

|----|-------|-----------|-----------------------------------------------------------------------|

|    |       | F.10.6    | I/D TSB Base Registers 193                                            |

|    |       | F.10.7    | I/D TSB Extension Registers 194                                       |

|    |       | F.10.8    | I/D TSB 8-Kbyte and 64-Kbyte Pointer and Direct Pointer Registers 194 |

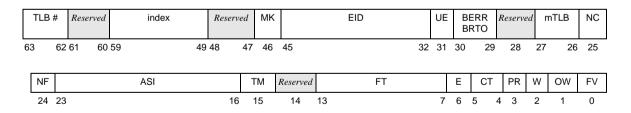

|    |       | F.10.9    | I/D Synchronous Fault Status Registers (I-SFSR, D-SFSR) 194           |

|    |       | F.10.10   | Synchronous Fault Addresses 201                                       |

|    |       | F.10.11   | I/D MMU Demap 201                                                     |

|    |       | F.10.12   | Synchronous Fault Physical Addresses 202                              |

|    | F.11  | MMU E     | Sypass 202                                                            |

|    | F.12  | Translat  | ion Lookaside Buffer Hardware 203                                     |

|    |       | F.12.2    | TLB Replacement Policy 203                                            |

| G. | Assen | nbly Lan  | guage Syntax 205                                                      |

|    | G.1   | Notation  | u Used 205                                                            |

|    |       | G.1.5     | Other Operand Syntax 205                                              |

|    | G.4   | HPC-A     | CE 拡張機能の表記法 206                                                       |

|    |       | G.4.1     | HPC-ACE 拡張のサフィックス 206                                                 |

| н. | Softw | are Cons  | iderations 209                                                        |

| т  | Exton | ding the  | SPARC V9 Architecture 210                                             |

| 1. | Exten | uing the  | SPARC V9 Architecture 210                                             |

| J. | Chan  | ges from  | SPARC V8 to SPARC V9 211                                              |

| K. | Progr | amming    | with the Memory Models 212                                            |

| L. | Addr  | ess Space | Identifiers 213                                                       |

|    | L.2   | _         | ues 213                                                               |

|    | L.3   |           | 64 IXfx ASI Assignments 214                                           |

|    |       | L.3.1     | Supported ASIs 214                                                    |

|    |       | L.3.2     | • •                                                                   |

|    |       | L.3.3     | ASI と命令の組み合わせと例外 221                                                  |

|    |       | L.3.4     | 内部レジスタの更新タイミング 222                                                    |

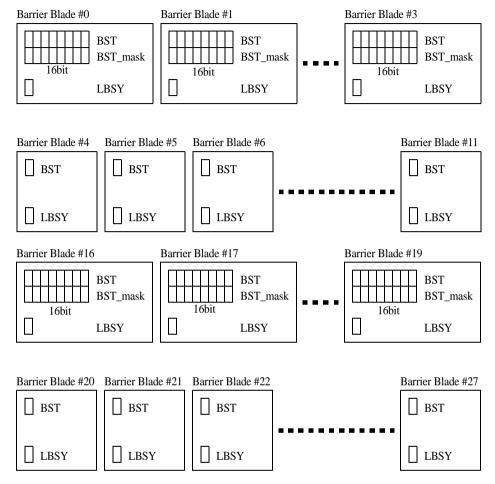

|    | L.4   | ハード       | ウェアバリア 222                                                            |

|    |       | L.4.1     | バリア資源の初期化と状態獲得 224                                                    |

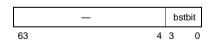

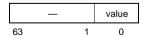

|    |       | L.4.2     | BST ビット位置の取得 226                                                      |

|    |       | L.4.3     | バリア資源の割り付け 227                                                        |

|    |       | L.4.4     | バリア操作用 ASI 228                                                        |

Ver 12, 2 Dec. 2013 Contents v

#### M. Cache Organization 231

- M.1 キャッシュタイプ 231

- M.1.1 L1 命令キャッシュ (L1I キャッシュ ) 232

- M.1.2 L1 データキャッシュ (L1D キャッシュ ) 233

- M.1.3 L2 キャッシュ 233

- M.2 キャッシュコヒーレンシプロトコル 234

- M.3 キャッシュ制御 ASI 235

- M.3.1 命令キャッシュフラッシュ (ASI\_FLUSH\_L1I) 235

- M.3.2 キャッシュデータの無効化 (ASI\_CACHE\_INV) 235

- M.3.3 セクタキャッシュ設定(SCCR) 236

- M.4 ハードウェアプリフェッチ 239

#### N. Interrupt Handling 241

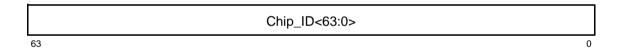

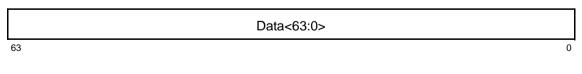

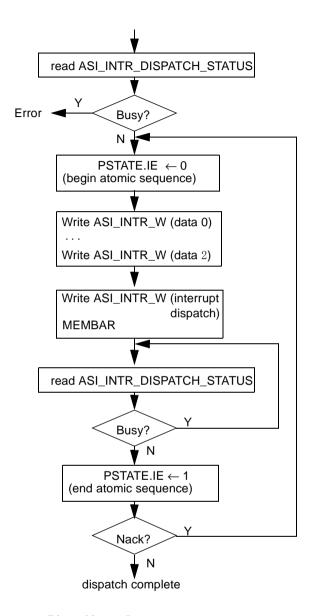

- N.1 Interrupt Vector Dispatch 241

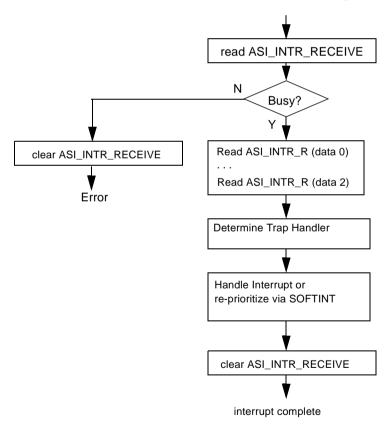

- N.2 Interrupt Vector Receive 243

- N.4 Interrupt ASI Registers 244

- N.4.1 Outgoing Interrupt Vector Data<7:0> Register 244

- N.4.2 Interrupt Vector Dispatch Register 244

- N.4.3 Interrupt Vector Dispatch Status Register 244

- N.4.4 Incoming Interrupt Vector Data Registers 244

- N.4.5 Interrupt Vector Receive Register 245

- N.6 インタラプト配送先の識別法 245

#### O. Reset, RED\_state, and error\_state 247

- O.1 リセット種類 247

- O.1.1 パワーオンリセット(POR) 247

- O.1.2 ウォッチドッグリセット(WDR) 248

- O.1.3 外部指示リセット(XIR) 248

- O.1.4 ソフトウェア指示リセット(SIR) 248

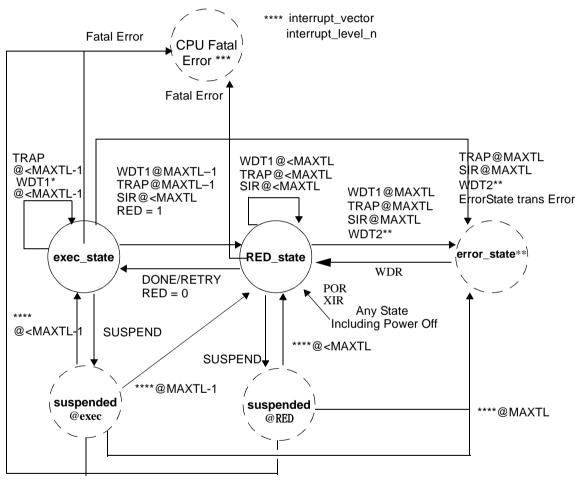

- O.2 RED state \( \geq \) error state 249

- O.2.1 RED\_state 250

- O.2.2 error\_state 250

- O.2.3 CPU Fatal Error 250

- O.3 リセット、RED\_state 後のプロセッサ状態 251

- O.3.1 Operating Status Register (OPSR) 255

#### P. Error Handling 257

- P.1 エラーの分類 257

- P.1.1 致命的エラー 258

- P.1.2 error state 遷移エラー 258

- P.1.3 緊急エラー 259

- P.1.4 抑止可能エラー 261

- P.1.5 instruction\_access\_error 262

- P.1.6 data\_access\_error 262

- P.2 エラー処理とエラー制御 263

- P.2.1 エラー処理に必要なレジスタ 263

- P.2.2 エラー検出時の動作 263

- P.2.3 CE 発見時に元データを自動で訂正できる限界 268

- P.2.4 キャッシャブルデータのエラーマーキング 269

- P.2.5 ASI EIDR 272

- P.2.6 エラー検出の制御 (ASI ERROR CONTROL) 272

- P.3 致命的エラーと error state 遷移エラー 274

- P.3.1 ASI\_STCHG\_ERROR\_INFO 274

- P.3.2 サスペンド中のスレッドでの error state 遷移エラー 276

- P.4 緊急エラー 276

- P.4.1 緊急エラーステータス (ASI UGESR) 277

- P.4.2 async data error (ADE) トラップ発生時の処理 280

- P.4.3 ADE トラップ発生した時の命令の実行状況 283

- P.4.4 ADE トラップハンドラの処理例 284

- P.5 Instruction Access Errors 286

- P.6 Data Access Errors 286

- P.7 抑止可能エラー 287

- P.7.1 ASI ASYNC FAULT STATUS (ASI AFSR) 287

- P.7.2 抑止可能エラーに対するソフトウェア処理 288

- P.8 レジスタで起きたエラーの処理方法 288

- P.8.1 特権・非特権レジスタの処理方法 289

- P.8.2 ASR レジスタの処理方法 290

- P.8.3 ASI レジスタの処理方法 291

- P.9 キャッシュで起きたエラーの処理方法 294

- P.9.1 キャッシュタグで起きたエラーの処理方法 295

- P.9.2 L1I キャッシュデータで起きたエラーの処理方法 295

- P.9.3 L1D キャッシュデータで起きたエラーの処理方法 296

Ver 12, 2 Dec. 2013 Contents vii

- P.9.4 L2 キャッシュデータで起きたエラーの処理方法 297

- P.9.5 L1I,L1D,L2 キャッシュの自動ウェイ縮退 298

- P.10 TLB で発生したエラー 300

- P.10.1 TLB エラーの処理 300

#### Q. Performance Instrumentation 303

- O.1 PA 概要 303

- Q.1.1 サンプル擬似コード 303

- O.2 PA イベントの説明 305

- O.2.1 命令種類、トラップ種類毎の統計情報 308

- Q.2.2 MMU と L1 キャッシュ関連のイベント計測 316

- O.2.3 L2 キャッシュ関連のイベント計測 317

- O.2.4 バストランザクションの計測 320

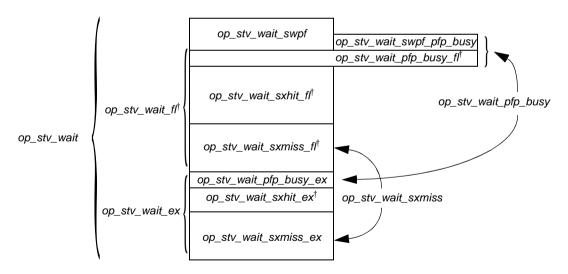

- Q.3 サイクルアカウンティング 321

#### R. System Programmer's Model 325

- R.1 System Config Register 325

- R.2 STICK Control Register 326

- S. Summary of Specification Differences 329

# Overview

# 1.1 Navigating the SPARC64<sup>TM</sup> IXfx Extensions

SPARC64 IXfx は、JPS1 に準拠したアーキテクチャのプロセッサである。JPS1 では、 仕様を共通仕様と実装依存仕様に分けて記述するようになっており、本仕様書は実装 依存仕様を定義する。本仕様書では原則として、共通仕様で定義済の事項については 再掲しない。

本書の章・節番号と見出し名は、基本的に JPS1 Commonality に合わせてあり、英語のままにしてある。各章・節では JPS1 Commonality の実装依存仕様や未定義仕様、あるいは SPARC64 IXfx で変更された仕様について説明している。 JPS1 Commonality にない章・節には日本語の見出しがついており、 SPARC64 IXfx 独自に追加された仕様を説明している。本書は JPS1 Commonality の定義を前提としているので、必要に応じて "SPARC Joint Programming Specification 1 (JPS1): Commonality で参照されたい。

# 1.2 Fonts and Notational Conventions

本仕様書の表記法は JPS1 Commonality に準ずる。

Ver 12, 2 Dec. 2013 F. Chapter 1 Overview

#### Reserved フィールドの扱い

命令語およびレジスタ中の使用されていないビットは、将来のために予約されている。そのようなフィールドを Reserved フィールドと呼び、Reserved または — と表記している。

JPS1 Commonality では Chapter 2 で、命令語およびレジスタの Reserved フィールドの扱いを以下のように定義している。

- 命令語の*Reserved*フィールドは0であるべき。0以外の値が入っていた場合の動作は 未定義 (Chapter 2)。

- レジスタの *Reserved* フィールドにソフトウェアが書く値は、そのフィールドの読み 出しで得られた値か 0。ハードウェアは 0 を出力すべき。

なお、命令語の *Reserved* に関しては、JPS1 **Commonality** の Section 6.3.9 と Appendix I.2 にも記述がある。

SPARC64 IXfx では、Reserved を以下のように扱う。

- 命令語の Reserved フィールドは、仕様に動作と値が明記されているものはその通り。 Reserved フィールドが 0 以外の値のときの動作が明記されていない命令は、そのフィールドを無視して実行する。

- レジスタの Reserved フィールドは、仕様に動作と値が明記されているものはその通り。動作と値が明記されていないフィールドは、書き込みは無視され、読み出しには不定値が返る。書き込んだ際の副作用が書かれていないものの動作は未定義である。

#### レジスタフィールドの読み書き属性

この論理仕様書では、レジスタのフィールドの読み書き属性を以下のように記述する。

TABLE 1-1 レジスタフィールドの読み書き属性

| Type 属性 | Description 意味                                             |  |

|---------|------------------------------------------------------------|--|

|         | 読み出しには不定値が返され、書き込みは無視される。<br>値が明記されていない Reserved はこれに相当する。 |  |

| R       | 読み出しにはフィールドの値が返され、書き込みは無視される。                              |  |

| W       | 読み出しには不定値が返され、書き込みにはその値が書き込まれる。                            |  |

| RW      | 読み出しにはフィールドの値が返され、書き込みにはその値が書き込まれる。                        |  |

| RW1C    | 読み出しにはフィールドの値が返され、 $1$ を書き込むとフィールドに $0$ が書かれる。             |  |

# **Definitions**

この章では SPARC64 IXfx に固有の概念・用語を定義する。JPS1 に共通の用語の定義は、JPS1 Commonality の Chapter 2 を参照。

#### basic floating-point

register

HPC-ACE で拡張されたレジスタのうち、SIMD の basic 側演算で使われる f[0] - f[254] レジスタ。

#### (SIMD の )basic 側演

算

SIMD 動作時の2演算のうちのひとつ。命令で指定したレジスタ番号を使う。

#### extended floating-point

register

HPC-ACE で拡張されたレジスタのうち、SIMD の extended 側演算で使われる f[256] - f[512] レジスタ。

#### (SIMD の )extended 側演

算

SIMD 動作時の 2 演算のうちのひとつ。命令で指定したレジスタ番号 +256 を使う。

#### HPC-ACE

High Performance Computing - Arithmetic Computational Extensions の略で、SPARC64 IXfx 独自に拡張された論理仕様の総称。レジスタ本数の増加、HPC用途の命令、浮動小数点演算の SIMD 拡張などを含む。

#### mTLB

メイン TLB。命令用 (I) とデータアクセス用 (D) に分かれており、それぞれ mITLB,mDTLB と呼ばれることもある。uITLB,uDTLB に載せるアドレス変換情報を保持している。uITLB,uDTLB がアドレス変換情報を持っていないとき、mTLB が検索される。mTLB にアドレス変換情報があれば、対応する uTLB に送られる。mTLB にアドレス変換情報がないときは、例外が発生しソフトウェアにトラップが通知される。ソフトウェアによりアドレス変換情報を mTLB に載せた後、ハードウェアが命令を再実行する。

#### syncing 命令

マシン sync を起こす命令。 syncing 命令の **発行**は、プログラム順で syncing 命令 よりも前の命令がすべて **完了**してから行われ、 syncing 命令が**爰行**してから後続命令が**爰行**される。 つまり syncing 命令は単独で**発行、実行、完了**される命令である。

Ver 12, 2 Dec. 2013 F. Chapter 2 Definitions 3

uTLB マイクロ TLB。命令用 (I) とデータアクセス用 (D) に分かれており、それぞれ uITLB, uDTLB と呼ばれることもある。ハードウェアは uTLB に載っているア ドレス変換情報にもとづいてアドレス変換を行う。uTLB にアドレス変換情報 がなければ、mTLB から補充される。

**XAR 対象命令** XAR レジスタで指定される、レジスタフィールドの上位ビット情報を結合して 実行される命令。

**アウトオブオーダ実行** 命令の**実行**が、プログラム順序を追い越して行われるマイクロアーキテクチャ。 入力ソースデータが揃っていない命令を、後続の入力ソースデータが揃った命 令が追い抜いて**実行**する。

演算器 (functional

unit) 演算命令を処理する資源。

(資源の)解放 命令 実行のために割り当てられた資源が、次の命令により使用可能になること。

**コア** コアとは、実行パイプラインと命令実行に関連する資源(演算器やL1キャッシュなど)を含んだ実体。一つまたはそれ以上の*スレッド*を持つことがあるが、SPARC64 IXfx では1コアは1スレッドからなる。

コミット(完了) ある命令について、その命令より前のすべての命令*実行*が正常に*完了*した後、 当該命令の実行結果を確定すること。ある命令がコミットすると、その命令の 実行結果はソフトウェアから見える資源に反映される。それ以前の状態は失わ れる。

コンプリート(終了) ある命令の*実行が終了*し、正常終了したことが命令発行ユニットに通知される こと。命令の終了により実行結果が一時的に反映されるが、*完了*するまではま だ永続的な状態にはなっておらず、元の状態に復旧することが可能である。

> **実行** 命令が実行ユニットに送られ、演算が行われること。命令が演算器にある間は 実行中である。

**実行終了** 演算器での命令の実行が終了し、結果が出力バスに出力されること。出力バス の結果はレジスタファイルや他の演算器へと送られる。

サイクル アカウンティング 性能阻害要因を分析する手法。

> サスペンド スレッドが命令実行を一時中止している状態。サスペンド中は命令は実行されないが、キャッシュ上のデータに矛盾が起きないようメンテナンスされている。 スリープと異なり、サスペンド中のスレッドを命令実行状態に復帰させるには、 割り込みやタイマによるトラップ発生が必要である。

**スーパースカラ** 1 サイクルに複数の命令を**発行、実行、完了**する CPU の機構。

スキャン CPU チップ内のラッチやレジスタを読み書きする方法。スキャン可能なように 設計されたラッチやレジスタはスキャンリングで読み出し・書き込みができる。

**ストール** *命令発行*ができないこと。資源の空き状態やプログラム上の制約から、必ずし も毎サイクル命令が*発行*できるとは限らない。 ストロング

**プリフェッチ** プロセッサ内部の資源が不足していても捨てられずに実行されることが保証されたデータプリフェッチ命令。

スレッド ソフトウェア命令列を実行するハードウェアの単位。ソフトウェアから見える 資源 (PC、レジスタなど)や、直接見えないが命令実行に必要なマイクロアー キテクチャを含んでいる。

**投機的命令実行** 命令実行が投機的であるとは、条件分岐の分岐方向が未確定な時点で、または 割り込みやトラップなどの発生有無が未確定な時点で、後続の命令を**実行**する こと。また、投機的な実行により得られた結果を使い、さらに後続の命令を**実** 行すること。

**プロセッサモジュール** 情報処理用の独立した実体で、外部との接続バスを共有するひとつまたはそれ 以上の**コア**が入った部品。

**命令ディスパッチ** ある命令の実行に必要な資源が全部使用可能になり、演算器に送られること。

**命令発行** 命令が **リザベーションステーション**に送られること。

**命令フェッチ** 命令が命令キャッシュまたは**コア**内部のバッファから読み出され、命令発行ユニットに送られること。

メモリマネジメントユ ニット (MMU)

**コア**内にある、64 ビットの論理アドレスを物理アドレスに変換するハードウェア機構。MMU には *mITLB*, *mDTLB*, *uITLB*, *uDTLB* およびアドレス変換を制御するための ASI レジスタがある。

リザベーション ステーション

**発行**された命令が、実行パイプラインに投入されるまで格納されるキュー(バッファ)。演算器が使用可能であった場合に、入力データが揃った命令は、演算器が使用可能になると、リザベーションステーションから取り出され演算器に投入される。**アウトオブオーダ実行**の制御はこのキューで行う。

**リネーミングレジスタ** 命令の実行結果を、コミットしてレジスタに格納されるまで一時的に保持する バッファ。ユーザが直接操作することはできない。

Ver 12, 2 Dec. 2013 F. Chapter 2 Definitions 5

# **Architectural Overview**

この章では、SPARC64 IXfx プロセッサの概要について説明する。この章は JPS1 Commonality の章立てには沿っていない。

# 3.1 SPARC64 IXfx プロセッサ

SPARC64 IXfx プロセッサは、1 つの CPU チップに 16 個のコアと L2 キャッシュ、さらにメモリコントローラ (MAC) を統合した、マルチコア・プロセッサである。アーキテクチャは SPARC V9 に準拠しながら独自の拡張を行い、サーバ用途の高性能・高信頼性に加え、HPC 分野でも高性能を追求したプロセッサである。

# 高性能を実現するマイクロアーキテクチャ

SPARC64 IXfx は、1 サイクルに最大 4 命令まで発行するアウトオブオーダ実行のスーパースカラプロセッサである。アウトオブオーダの処理では、命令フェッチ部は実行パスを予測しながら命令をフェッチし、その命令列をその順番に従い発行する。発行された命令は、実行可能になるまで一時的にリザベーションステーションに格納される。命令が実行可能になると、元の命令列の順序とは関係なく実行ユニットへ送られ、実行される。実行が終了 (complete) した命令は、元の命令列の順序に従い完了 (commit) 処理される。つまり、ある命令の完了処理は、その命令に先行する命令がすべて完了してから行われる。完了処理が終わると命令の実行結果がレジスタ・メモリ等に反映されプログラムから見えるようになる。アウトオブオーダ実行はSPARC64 IXfx の高性能に大きく貢献している。

SPARC64 IXfx は、分岐命令の実行方向を予測するためにブランチヒストリバッファを実装している。ブランチヒストリバッファは、DBMS のような大規模アプリケーションで高い予測的中率を維持するよう、また SPARC64 IXfx の高度な命令フェッチ機構をサポートするよう、十分な大きさを備えている。この命令フェッチ機構は、分

岐履歴に従い、複数の条件分岐を含む命令列の実行方向を予測し、命令をフェッチする。これにより、命令キャッシュミスによって生じる性能ペナルティの影響を可能な限り小さくできる。

SPARC64 IXfx はまた、HPC (High Performance Computing) 用途にふさわしい機能を備えている。それはたとえば、SPARC V9 の命令仕様を独自に拡張した HPC-ACE 拡張や、チップ内コア間で高速な同期を実現するハードウェアバリア機能などである。HPC-ACE 拡張では整数レジスタを 192 本、浮動小数点レジスタを 256 本に拡張し、浮動小数点演算命令を中心に 7 つの新規命令を追加したほか、2 並列の SIMD(Single Instruction Multiple Data) 演算も可能にした。SIMD の採用により、1 サイクルで最大8 つの浮動小数点演算を実行することができ、HPC 分野の高性能を実現している。

#### チップ内に集約された高機能

SPARC64 IXfx は、CPU チップ上に L2 キャッシュを持っている。L2 キャッシュは、命令、データ共用で、16 コアに共有されている。SPARC64 IXfx では L2 キャッシュが最外層のキャッシュである。L2 キャッシュを CPU チップに統合したことで、SPARC64 IXfx の性能と信頼性は向上し、アクセス時間が短くウェイ数の多いキャッシュを実装することができている。また、L2 キャッシュに対する外部接続が不要なため、高信頼性にも貢献している。

さらに SPARC64 IXfx は、メモリコントローラも CPU チップに内蔵している。DIMM は CPU に直結され、メモリアクセスのレイテンシは劇的に短縮された。

HPC の高性能を約束する重要な機能の一つがハードウェアバリアである。マルチスレッドのジョブを高速に処理するためには、スレッド間の同期にかかる時間を可能な限り減らすことが重要である。この問題に対し SPARC64 IXfx は、ハードウェアによるバリア同期機構という解決策を提供する。SPARC64 IXfx のハードウェアバリアは、複数コアでのバリア同期用に加え、全コアによるマスター/ワーカーモデルを可能にする、post/wait 型のプリミティブも用意している。

## 高信頼性

SPARC64 IXfx は以下の高度な RAS 機能を実装している。

- 1. キャッシュの RAS 機能

- 強固なキャッシュエラー保護:

- L1D キャッシュデータ、L2 キャッシュデータ、L2 キャッシュタグに対する ECC 保護。

- LII キャッシュデータに対するパリティ保護。

- LII キャッシュタグと LID キャッシュタグに対するパリティ保護と二重化。

- すべての種類の1ビットエラーの自動訂正:

- ECC 保護されたデータに対する自動1ビットエラー訂正。

- LII キャッシュデータパリティエラーに対する LII キャッシュデータの無効化と 再読み込み。

- L1IキャッシュタグおよびL1Dキャッシュタグのパリティエラーに対する二重化 されたタグからのコピー。

- キャッシュの一貫性を維持したまま行われる動的なウェイ縮退。

- キャッシュデータの訂正不能エラーのマーキング:

- 最初に訂正不能エラーを発見したモジュールが、特殊なパターンでマークす

- 一つの故障で何度もエラーが報告されないよう、エラーマークで故障モジュー ルを識別して隔離する。

- 2. 命令実行ユニットの RAS 機能

- 強固なエラー保護・

- 全てのデータパスのパリティ保護。

- ほとんどのソフトウェア可視レジスタ、内部、一時レジスタに対するパリティ

- 演算結果のパリティまたは剰余チェック。

- ハードウェアによる命令再実行。

- (ハードウェア命令再実行の失敗の後の)ソフトウェア命令再実行のサポート。

- ソフトウェアリカバリのための エラー分離:

- どのレジスタがエラーしたか(被疑レジスタ)の明示。

- エラーした命令が再実行可能かどうかを示す。

- エラーの度合いによりトラップを使い分ける。

- 3. 充実したソフトウェアインターフェイス

- プログラム実行への影響の重大度によるエラー分類:

- 重大なエラー(マスク不可): OS の介入無しでの実行続行は不可能なエラー。例 外で報告される。

- 軽微なエラー(マスク可): エラーが例外で報告されるかどうかを OS が制御する。 エラーは、プログラム実行には直接作用しない。

- ソフトウェアへの影響を判断するための、識別したエラーの表示。

- 付加的なエラーに対する非同期データエラー (ADE) 例外

- 例外通知により命令実行が中断されるが、その状態は発見されたエラーによっ て異なるので、完了方法を表示する。

- 遅延報告 (deferred) だがリトライ可能な ADE 例外。

- エラー分離と命令再実行が正しく行えるよう、同時に起きた複数のエラーをす べて表示する。

#### コア内部のコンポーネント 3.1.1

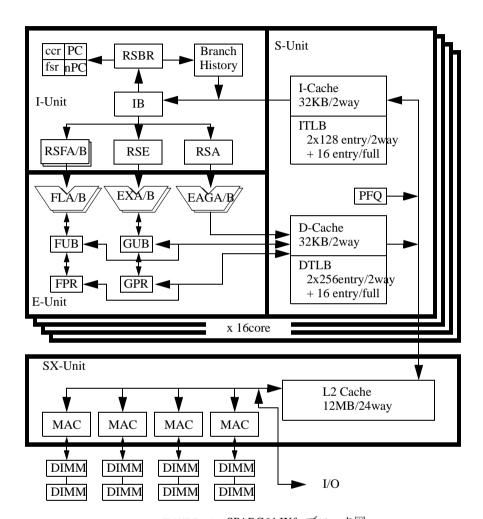

FIGURE 3-1 は SPARC64 IXfx のブロック図である。SPARC64 IXfx は 16 個のコアとメ モリコントローラ、バスインターフェースをチップ内に統合している。コア内には以 下のコンポーネントがある。

- 命令制御ユニット(IU)

- 実行ユニット (EU)

- 記憶ユニット (SU)

- L2 キャッシュと外部アクセスユニット (SXU)

FIGURE 3-1 SPARC64 IXfx ブロック図

# 3.1.2 命令制御ユニット (IU)

IU (Instruction control Unit) は、命令実行パスを予測し、予測したパスの命令をフェッチする、その後、フェッチした命令を適切なリザベーションステーションに配送し、そして、実行パイプラインに命令を発送する。発送された命令は、アウトオブオーダで実行され、インオーダで完了される。主要なブロックを TABLE 3-1 に示す。

TABLE 3-1 命令制御ユニットの主要ブロック

| ブロック                  | 説明                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------|

| 命令フェッチパイプライン          | 5 ステージ: フェッチアドレス生成、iTLB と LII キャッシュアクセス、iTLB と LII キャッシュのタグ比較、命令バッファへの書き込み、結果の格納。                           |

| ブランチヒストリ              | 分岐先と分岐方向を予測するためのテーブル。                                                                                       |

| 命令バッファ                | フェッチした命令を保持するためのバッファ。                                                                                       |

| リザベーションステーショ<br>ン     | 命令が実行可能になるまで保持するための5つのリザベーションステーション:分岐とその他の制御転送命令用のRSBR、load/store命令用のRSA、整数演算命令用のRSE、浮動小数点演算命令用のRSFAとRSFB。 |

| コミットスタックエントリ<br>(CSE) | 実行中の(発行されてまだ完了していない)命令の情報を保持するためのバッファ。                                                                      |

| PC, nPC, CCR, FSR     | 命令実行制御のためのプログラム可視レジスタ。                                                                                      |

# 3.1.3 命令実行ユニット (EU)

EU (Execution Unit) は全ての整数 (算術、論理、シフト)命令と全ての浮動小数点及び VIS 命令の実行を行う。TABLE 3-2 に EU の主要なブロックを記述する。

TABLE 3-2 EU の主要ブロック

| ブロック                         | 説明                                      |

|------------------------------|-----------------------------------------|

| GUB                          | 汎用整数レジスタ (gr) 用のリネーミングレジスタファイル。         |

| GPR                          | 汎用整数レジスタファイル。                           |

| FUB                          | 浮動小数点レジスタ (fr) 用のリネーミングレジスタファイル。        |

| FPR                          | 浮動小数点レジスタファイル。                          |

| EU 制御論理                      | 命令実行ステージを制御:実行する命令の選択、レジスタ<br>リード、命令実行。 |

| インターフェースレジスタ                 | 他ユニットへの入出力レジスタ。                         |

| 2 つの整数実行パイプライン<br>(EXA, EXB) | 64 ビット ALU とシフタ。                        |

**TABLE 3-2** EU の主要ブロック

| ブロック                                            | 説明                                                    |

|-------------------------------------------------|-------------------------------------------------------|

| 2 つの浮動小数点実行パイプライン (FLA, FLB)                    | 各浮動小数点実行パイプラインは、浮動小数点(乗算、加算/減算、乗加算、除算/平方根、グラフィックス)命令。 |

| メモリアクセスパイプラインのための 2 つの仮想アドレス加算器<br>(EAGA, EAGB) | ロード / ストアのための 2 つの 64 ビット仮想アドレス生成。                    |

# 3.1.4 ストレージ制御ユニット (SU)

SU (Storage Unit) は、ロード及びストア命令のために全てのデータの供給と受給を扱う。TABLE 3-3 に、SU の主要なブロックを記述する。

**TABLE 3-3** SU の主要ブロック

| プロック                | 説明                                                                                           |

|---------------------|----------------------------------------------------------------------------------------------|

| レベル1命令キャッシュ         | 32KB, 2 ウェイセットアソシアティブ、1 ラインは 128 バイト。低レイテンシ、命令供給用。                                           |

| レベル1データキャッシュ        | 32KB, 2 ウェイセットアソシアティブ、1 ラインは 128 バイト。低<br>レイテンシ、ロード・ストアデータ供給用。                               |

| 命令用 TLB             | 128 エントリ、2 ウェイセットアソシエイティブ TLB (sITLB) が 2 つ。                                                 |

|                     | 16 エントリ、フルアソシエイティブ TLB (fITLB)。                                                              |

| データ用 TLB            | 256 エントリ、2 ウェイセットアソシエイティブ TLB (sDTLB) が 2 つ。                                                 |

| -1-3 - 1-71         | 16 エントリ、フルアソシエイティブ TLB (fDTLB)。                                                              |

| ストアバッファとライト<br>バッファ | ストア操作のレイテンシからパイプラインを分離する。ストアが<br>データを待っている間、パイプラインが流れ続ける事を可能にす<br>る。最終的には、レベル1データキャッシュに書き込む。 |

# 3.1.5 二次キャッシュユニット(SXU)

SXU (Secondary Cache and External Access Unit) は、レベル 2 キャッシュの操作と外部 データクセスインタフェースを制御する。TABLE 3-4 に、SXU の主要なブロックを記述する。

**TABLE 3-4** SXU の主要ブロック

| ブロック        | 説明                                                                   |

|-------------|----------------------------------------------------------------------|

| レベル 2 キャッシュ | サイズは 12MB であり、24 ウェイセットアソシエイティブ構成、<br>1 ラインは 128 バイト。ライトバック方式のキャッシュ。 |

**TABLE 3-4 SXU** の主要ブロック

| ブロック       | 説明                                                  |

|------------|-----------------------------------------------------|

| ムーブインバッファ  | キャッシュライン読み出しリクエストに応じてメモリシステムか<br>ら返ってきたデータをキャッシュする。 |

| ムーブアウトバッファ | メモリへのライトバックデータを保持する。                                |

# 3.2 プロセッサパイプライン

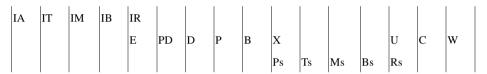

SPARC64 IXfx のパイプラインは 16 ステージからなる。FIGURE 3-2 にパイプラインの各ステージを、FIGURE 3-3 にパイプライン図を示す。

FIGURE 3-2 SPARC64 IXfx のパイプラインステージ

## 3.2.1 命令フェッチステージ

- IA: 命令フェッチアドレス生成

- IT: iTLB. 命令キャッシュタグアクセス

- IM: 命令キャッシュタグ比較

- IB: 命令キャッシュからバッファへ読み込み

- IR: 命令フェッチ最終ステージ

IAからIRまでのステージでは、キャッシュアクセスユニット(SU)と連携して命令を読み込み、パイプラインの後続ステージに供給する。メモリまたはキャッシュから読み出された命令は、命令バッファ(Instruction Buffer)に蓄えられる。

SPARC64 IXfx は分岐予測用の BRHIS (BRanch HIStory) と RAS (Return Address Stack) 資源を備えている。命令フェッチアドレスステージでは、分岐予測を行いフェッチアドレスを決定する。

SPARC64 IXfx の命令フェッチステージは、実行ステージがストールしていても命令フェッチができるよう、後続ステージとは可能な限り独立したデザインになっている。命令フェッチ部は、命令バッファがフルになるまでフェッチを続け、その後もプリフェッチを出して命令列を L1 キャッシュに持ってくることが可能である。

**FIGURE 3-3** SPARC64 IXfx のパイプライン図

## 3.2.2 命令発行ステージ

■ E: エントリ

■ PD: プリデコード

■ D: デコード

SPARC64 IXfx はアウトオブオーダ実行のプロセッサである。SPARC64 IXfx には 6 個の演算器があり (整数用 2 つ、浮動小数点用 2 つ、メモリアクセス用 2 つ)、整数演算器とメモリアクセス演算器には演算器 2 つに対して 1 個の、浮動小数点演算器には独立した 2 個のリザベーション・ステーションがある。E, PD, D ステージでは命令をデコード・発行し、リザベーション・ステーションに登録する。SPARC64 IXfx は 1 サイクルで最大 4 命令まで発行できる。

命令実行に必要な以下の資源は、このステージで割り当てられる。

- コミットスタックエントリ (CSE)

- 整数用と浮動小数点用のリネーミングレジスタ (GUB, FUB)

- リザベーション・ステーションのエントリ

- メモリアクセス用のポート

命令実行に必要な資源は命令ごとに異なるが、どの命令でも、実行に必要なすべての資源の割り当てはこのステージで行われる。通常の実行では、リザベーション・ステーションの解放はXステージで、その他の資源の解放はパイプラインの最後のWステージで行われる。EステージからWステージまでにある命令が実行中 (in-flight)の命令となる。例外が通知されると、実行中の命令は中止され、それらの命令が使用していた資源は直ちに解放される。これにより、デコーダは新しい命令の発行がすぐに行える。

# 3.2.3 実行ステージ

- P: プライオリティ

- B: バッファ読み出し

- X: 実行

- U: 更新

リザベーション・ステーションに格納された命令は、各々の実行条件が満たされると 演算器に送られる。実行条件とは、入力データが確定する、演算器が空く、などであ る。実行にかかるサイクル数は命令によって異なる。

#### キャッシュアクセスの実行ステージ

メモリアクセス要求は、アドレス計算が完了すると、キャッシュアクセスユニットに送られる。キャッシュアクセスのステージは、分岐予測を除けば命令フェッチの各ステージと同じである。詳細はSection 3.2.1 を参照。命令フェッチのステージ名とキャッシュアクセスのステージ名の対応を以下に示す。

| 命令フェッチ | データアクセス |

|--------|---------|

| IA     | Ps      |

| IT     | Ts      |

| IM     | Ms      |

| IB     | Bs      |

| IR     | Rs      |

例外が通知されると、パイプラインにデータを送るための資源は解放されるが、 キャッシュアクセスのパイプライン自体は、システムに要求したメモリアクセスを完 了させるまでは動き続ける。データが返ってくると、キャッシュにストアされる。

# 3.2.4 命令完了ステージ

- C: コミット

- W: 書き込み

アウトオブオーダで実行された命令は、最後に命令順序通りに完了処理が行われる。 例外の処理はこのステージで行われる。実行ステージで起きた例外は、すぐに処理されるのではなく、先行するすべての命令の完了処理が終わった後で通知される<sup>1</sup>。

<sup>1.</sup> RAS 関連の例外は完了を待たずに報告される。

# **Data Formats**

JPS1 Commonality の Chapter 4 を参照。

Ver 12, 2 Dec. 2013 F. Chapter 4 Data Formats 17

# Registers

JPS1 Commonality の Chapter 5 では、汎用レジスタ、ASR レジスタ、ASI レジスタの 3 種類を定義している。章立ては大きく、非特権レジスタ、特権レジスタの順番に なっており、ASR、ASI レジスタは特権レジスタとして扱われているが、実際は非特権アクセス可能なものも混ざっているので適切さを欠いている。さらに、ASI レジスタについては、Chapter 5 の他、用途に応じていくつかの Appendix でも定義されており、この点でもまとまりを欠いている。

SPARC64™ IXfx Extensions の章立てはできる限り JPS1 Commonality に合わせることにしているので、JPS1 Commonality の Chapter 5 で定義されているレジスタに関する実装依存仕様はこの章に記述することにする。ASI, ASR レジスタは特権・非特権が混ざるが、便宜上 Section 5.2, "Privileged Registers" に配置した。

ASI レジスタについては、以下のセクションも参照されたい。

- Appendix F.10, "Internal Registers and ASI Operations"

- Appendix L.3.2, "Special Memory Access ASIs"

- Appendix L.4, "ハードウェアバリア"

- Appendix M.3, "キャッシュ制御ASI"

- Appendix N.4, "Interrupt ASI Registers"

- Appendix P.2.5, "ASI\_EIDR"

- Appendix P.2.6, "エラー検出の制御 (ASI\_ERROR\_CONTROL)"

- Appendix P.3.1, "ASI\_STCHG\_ERROR\_INFO"

- Appendix P.4.1, "緊急エラーステータス (ASI\_UGESR)"

- Appendix P.7.1, "ASI\_ASYNC\_FAULT\_STATUS (ASI\_AFSR)"

- Appendix R.1, "System Config Register"

- Appendix R.2, "STICK Control Register"

また、電源オン時やリセット時のレジスタ値については Appendix O.3, "Uセット、 $RED\_state$  後のプロセッサ状態" (page 251) に、レジスタでエラーが発生した際の通知方法やエラー修復方法については Appendix P.8, "Uジスタで起きたエラーの処理方法" (page 288) にまとめられている。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 19

# 5.1 Nonprivileged Registers

# 5.1.1 General-Purpose r Registers

r[32] - r[63] (xq[0] - xq[31]) を追加する。

レジスタ番号は既存命令フィールドには入りきらないので、上位 1 ビットを XAR.urs1, XAR.urs2, XAR.urs3, XAR.urd で指示する。拡張されるレジスタ数は 32 本なので、各フィールドの bit<2:1> は 0 になっていなければならない。 bit<2:1> が 0 でないときは、*illegal\_action* 例外が通知される。

拡張整数レジスタは大部分の命令で使用可能。使用できない命令の実行時に XAR.v=1 になっていると、*illegal\_action* 例外が通知される。

xg[0] - xg[31] は PSTATE.AG, PSTATE.MG, PSTATE.IGの値によらず同じものが見える。

拡張レジスタに対する書込みを行うと、XASR.xqd=1になる。

**Programming Note –** Context switch 時に save する必要があるかどうかが判断できる。

# 5.1.4 Floating-Point Registers

レジスタを追加し、全部で 256 本の倍精度レジスタが使えるようにする。追加するのは倍精度レジスタで、f[64]-f[510] (偶数番号のみ) で指定する。レジスタの追加に伴い、レジスタの状態を表わす XASR も追加される。詳細は "Extended Arithmetic Register Status Register (XASR) (ASR 30)" (page 32) 参照。

f[0] -f[254] を Basic Floating-Point Registers、f[256] -f[510] を Extended Floating-Point Registers と呼ぶことにする。またf[0] -f[62] を V9 Floating-Point Registers とも呼ぶ。

## Floating-Point Register Number Encoding

JPS1 Commonality の同名の節で、命令で倍精度レジスタを指示する際のエンコーディングが定義されている。

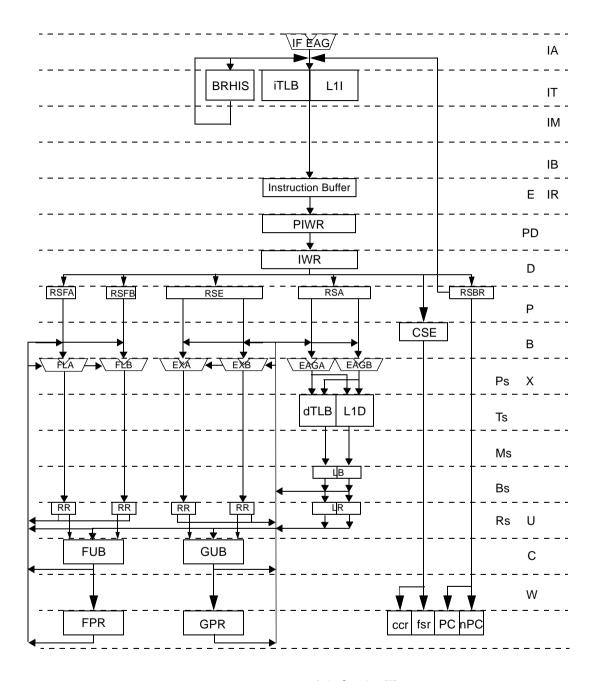

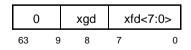

FIGURE 5-1 倍精度浮動小数点レジスタ番号のエンコーディング

拡張された 256 本の倍精度レジスタを指示するには、命令語のレジスタフィールド 5 ビットでは足りない。このため HPC-ACE では、レジスタフィールドの上位ビットを XAR レジスタに置き、命令実行時にそれらを結合してレジスタ番号を生成することに した。したがって、命令語だけではレジスタ番号は特定できない。

HPC-ACE 拡張レジスタ番号の生成は、XAR に置かれた上位 3 ビットと、FIGURE 5-1 に示したデコード後の 6 ビットを結合し 9 ビットの番号とする。最下位ビットは常に 0 になるので、f[0] - f[510] の偶数番号のみ、256 本のレジスタが指示できる。

## 倍精度レジスタの単精度利用

レジスタの追加に合わせて、倍精度レジスタを単精度浮動小数点演算でも使えるようにする。SPARC64 IXfx で追加されたレジスタだけでなく、SPARC V9 で定義された倍精度レジスタも単精度浮動小数点演算に使える。単精度浮動小数点演算命令で倍精度レジスタを指定するには、その命令の実行時点で XAR.v=1 であればよい。したがって、単精度で SIMD 演算を行うときは、倍精度レジスタを使うことになる。

倍精度レジスタを単精度浮動小数点演算に使用する際は、以下の点が SPARC V9 仕様と異なる。

- 命令のレジスタフィールドの解釈は、JPS1 Commonality の TABLE 5-5 の倍精度と同じになる。したがって偶数番号レジスタのみが使用できる。f[2n] (n = 0-255)

- レジスタの値は、bit<63:32> の上位 4 バイトを単精度値と解釈し、bit<31:0> の下位 4 バイトは無視される。

- 演算結果やロード結果はレジスタの上位4バイトに書き込まれ、下位4バイトには0 が書き込まれる。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 21

**Programming Note** – XAR.v=1かつ XAR.urs1=0の場合、rs1では SPARC V9の 倍精度レジスタを使って単精度演算を行う。rs2, rs3, rdも同様である。このとき bit<31:0> すなわち奇数番号レジスタの内容は破壊されることに注意すること。

エンディアン変換は単精度数、つまり4バイトを単位として行われる。

### SIMD 拡張命令のレジスタ指定方法

浮動小数点レジスタを使う命令の大部分は、XAR.V=1 かつ XAR.SIMD=1 のときに SIMD 拡張命令となり、1 命令で 2 演算を実行する。SIMD 演算で使われるレジスタの 組は、f[2n] に対して f[2n+256] (n=0-127) に固定されている。命令では f[2n] 側を指定する。使えないレジスタを指定した場合は *illegal\_action* が通知される。

SIMD FMADD 命令だけは例外で、rs1, rs2 に f[2n+256] を指定できる。詳細は Appendix A.24.1, "Floating-Point Multiply-Add/Subtract" (page 70) を参照。

**Programming Note** – 単精度浮動小数点命令も SIMD 拡張できるが、その際は、倍精度レジスタを単精度で使う。詳細は"*倍精度レジスタの単精度利用*"(page 21) を参照。

既存浮動小数点命令のうち SIMD 拡張されない命令には以下の命令が含まれる。 SIMD 拡張可能な命令の一覧は TABLE A-2 を参照。

- FDIV(S,D), FSQRT(S,D)

- VIS のうち論理演算 (FOR, FAND, etc.) でないもの

- FBfcc, FBPfcc, FCMP, FCMPE, FMOVcc など、fcc, icc, xcc を参照、更新する命令

- FMOVr

なお、SIMD の 2 演算を区別するときは、f[2n] に結果が格納される側の演算をbasic 側、f[2n+256] に結果が格納される側の演算を extended 側と呼ぶ。

エンディアン変換は basic, extended 毎に行われる。

## 5.1.7 Floating-Point State Register (FSR)

## FSR\_nonstandard\_fp (NS)

SPARC V9 仕様では FSR.NS ビットを定義している。このビットを 1 にセットすることで、浮動小数点演算器が IEEE Std 754-1985 に準拠しない演算処理を行っても良いことになっている。SPARC64 IXfx は FSR.NS ビットをサポートしている。

FSR.NSに1がセットされていると、演算の入力が非正規化数の場合や結果が非正規化数の場合に fp\_exception\_other が ftt = unfinished\_FPop 通知されるのではなく、同符号の0に置き換えられて、fp\_exception\_ieee\_754 が fsr.cexc.nxc=1 で通知される(この例外は FSR.TEM.NXM でマスクすることができる)。詳細は Appendix B.6, "Floating-Point Nonstandard Mode" (page 139) を参照。

FSR.NS に 0 がセットされていると、IEEE Std 754-1985 に準拠して動作する。

#### FSR\_version (ver)

個々の SPARC V9 IU 実装 (VER.impl で識別される)は、1 個以上の FPU を実装してもよいし実装しなくてもよい。このフィールドはこの CPU に実装されている FPU のバージョンを示す。SPARC64 IXfx の最初の版では FSR.ver = 0 である (impl.dep. #19)。しかし、将来の版では別の値になっているかもしれない。詳細はデータシートを参照。

## FSR\_floating-point\_trap\_type (ftt)

SPARC64 IXfx が fp\_exception\_other を ftt = unfinished\_FPop で通知する条件は Appendix B.6.1, "fp\_exception\_other Exception (ftt=unfinished\_FPop)" (page 140) を参照 (impl.dep. #248)。

#### FSR current exception (cexc)

ビット4から0は、IEEE 754で定義された例外のうちどれが発生したかを示す。例外が発生していなければ、対応するビットには0がセットされる。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 23

<sup>1.</sup> non-SIMD 時は 1 ビットだが、SIMD では複数ビットセットされることがある。

#### **FSR** Conformance

SPARC V9 では TEM, cexc, aexc のハードウェアでの実装方法を 2 種類許容している ( どちらも IEEE Std 754-1985 に準拠している )。SPARC64 IXfx は (1)、すなわちこれら 3 つを全部実装している。別の実装方法については JPS1 Commonality の Section 5.1.7 を参照。

## SIMD 演算における cexc, aexc 更新

SIMD 演算では basic, extended 両方の演算が同時に行われる。入力データは basic, extended で異なるので、両方で例外が起きることも、片方だけ起きることもある。

片方で例外が起きた場合の動作は、non-SIMD 演算と同じである。両方で例外が起きた場合、SPARC64 IXfx の SIMD 演算での例外通知と ftt の更新は以下のようになる。

1. basic, extended 両方で fp exception ieee 754 例外が検出された場合

説明のために、basic で起きた例外を保持する basic.cexc レジスタ、extended で起きた例外を保持する extend.cexc レジスタを仮定し、それぞれが、uf/of/dz/nx/nv のビットを持つものとする。

a. 両方とも例外通知がマスクされており、例外を通知しない場合

fsr.cexcにはbasic.cexcとextend.cexcの論理和が表示され、fsr.aexcにはbasic.cexcとextend.cexcの論理和が反映される。

```

\begin{array}{lll} \texttt{fsr.cexc} & \leftarrow \texttt{basic.cexc} \mid \texttt{extend.cexc} \\ \texttt{fsr.aexc} & \leftarrow \texttt{fsr.aexc} \mid \texttt{basic.cexc} \mid \texttt{extend.cexc} \end{array}

```

b. basic か extended のどちらかの例外が通知される場合

fsr.cexc には basic.cexc と extend.cexc の論理和が表示される。 fsr.aexc は更新されない。

```

fsr.cexc ← basic.cexc | extend.cexc

```

c. basic, extended 両方とも例外が通知される場合

fsr.cexc には basic.cexc と extend.cexc の論理和が表示される。 fsr.aexc は更新されない。

```

fsr.cexc ← basic.cexc | extend.cexc

```

2. 一方で fp exception ieee 754. 他方で fp exception other が検出された場合

例外の優先順位と異なり、fp\_exception\_other 例外が FSR.ftt = unfinished\_FPop で通知される。FSR.aexc, FSR.cexc は更新されない。

**Programming Note** – *fp\_exception\_other* が通知された場合、同時に *fp\_exception\_ieee\_754* 例外が起きたかどうかを判断する方法はないので、システムソフトウェアのエミュレーションルーチンは IEEE に準拠した例外の検出と、関連するレジスタの更新も行うこと。

3. basic, extended 両方で fp\_exception\_other が検出された場合

fp\_exception\_other 例外が FSR.ftt = unfinished\_FPop で通知される。FSR.aexc,FSR.cexc は更新されない。

**Note** - non-SIMD 演算の場合、*fp\_exception\_ieee\_754* が通知されるときは fsr.cexc には 1 要因のみが表示される。SIMD 演算の場合、basic と extended の要因の論理和 が表示されるので、複数要因が表示されることがある。

### 5.1.9 Tick (TICK) Register

SPARC64 IXfx は TICK.counter を 63 ビット幅で実装している (Impl. Dep. #105).

Implementation Note – SPARC64 IXfx では、TICK の読み出し時に counter に表示される値は、RDTICK 命令が実行されたときのものであり、完了したときのものではない (SPARC64 IXfx はアウトオブオーダ実行なので両者は明らかに異なる)。TICK の読み出しを2回行ったとき、counter の差分は、2回の RDTICK 命令の実行の間の CPU サイクル数である。間に挟まる命令列が十分長ければ、実行の間の CPU サイクル数と完了の間の CPU サイクル数の差は小さいだろう。

# 5.2 Privileged Registers

# 5.2.6 Trap State (TSTATE) Register

SPARC64 IXfx は TSTATE. CWP のビット <2:0> のみを実装している。ビット 3 とビット 4 の書き込みは無視され、読み出しには 0 が返る。

**Note** – ソフトウェアで PSTATE.RED に 1 を設定すべきではない。RED\_state に遷移する際に必要な、ハードウェア内部の処理をせずに、遷移する可能性があるためである。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 25

## 5.2.9 Version (VER) Register

TABLE 5-1 に SPARC64 IXfx の VER の各フィールドと値を示す。

TABLE 5-1 VER のエンコーディング

| ビット   | フィールド  | 説明                                   |

|-------|--------|--------------------------------------|

| 63:48 | manuf  | 0004 <sub>16</sub> (Impl. Dep. #104) |

| 47:32 | impl   | 9                                    |

| 31:24 | mask   | n (n の値はプロセッサチップの版数による)              |

| 15:8  | maxtl  | 5                                    |

| 4:0   | maxwin | 7                                    |

manuf フィールドには、JEDEC で定められた富士通を示す 8 ビットコードが表示され、上位 8 ビットは 0 となる。manuf, impl, mask フィールドの値はその性質上、将来のプロセッサでは変更されることがある。mask フィールドは論理回路が変更されるたびに大きい数字が入ることになるが、それが連続した数字である必要はない。

## 5.2.11 Ancillary State Registers (ASRs)

ASR の詳細については、JPS1 Commonality の Section 5.2.11 を参照。

#### Performance Control Register (PCR) (ASR 16)

SPARC64 IXfx の PCR 仕様は JPS1 Commonality 仕様と一部が異なる。FIGURE 5-2 と TABLE 5-2 で、JPS1 Commonality で定義された impl.dep. #207, #250 の SPARC64 IXfx での仕様と、PCR.SU, PCR.SL の JPS1 Commonality 仕様からの変更分を含む、PCR の仕様を説明する。PCR<2:1> は JPS1 Commonality に準拠している。

PA イベントカウンタの詳細は Appendix Q を参照。

| (  | )  | 0' | ۷F | (  | 0  | OVRO | 0  | N  | С  | 0  | S  | С  | S  | U  | S  | L | ULRO | UT | ST | PRIV |

|----|----|----|----|----|----|------|----|----|----|----|----|----|----|----|----|---|------|----|----|------|

| 63 | 48 | 47 | 32 | 31 | 27 | 26   | 25 | 24 | 22 | 21 | 20 | 18 | 17 | 11 | 10 | 4 | 3    | 2  | 1  | 0    |

FIGURE 5-2 PA 設定レジスタ (Performance Control Register, PCR) (ASR 16)

TABLE 5-2 PCR のフィールド

| ビット   | フィールド | 説明                                                                                                                                                                                                                                                                                                                   |    |     |     |     |     |     |                          |     |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|-----|-----|-----|--------------------------|-----|

| 47:32 | OVF   | オーバーフロー。RDPCR でカウンタのオーバーフローの情報が読み出せ、WRPCR でオーバーフロー情報をセット・クリアすることができる。PCR.OVF は SPARC64 IXfx 独自のフィールドである (impl. dep. #207)。OVF のビットとカウンタの対応は以下の通りである。OVF のビットに 0 を書き込むことで、対応するカウンタのオーバーフロー情報をクリアできる。                                                                                                                  |    |     |     |     |     |     |                          |     |

|       |       | 0 U3 L3 U2 L2 U1 L1 U0 L0                                                                                                                                                                                                                                                                                            |    |     |     |     |     |     | LO                       |     |

|       |       | 15                                                                                                                                                                                                                                                                                                                   | 7  | 6   | 5   | 4   | 3   | 2   | 1                        | 0   |

|       |       | ソフトウェアが 1 を書き込んでも、                                                                                                                                                                                                                                                                                                   | オー | バーフ | フロー | -のほ | 削外に | は通知 | 旧され                      | はい。 |

| 26    | OVRO  | オーバーフロー情報の変更禁止。書き込みの際、書き込もうとするデータの OVRO が 0 だと、データの OVF で PCR.OVF が 更新される。データの OVRO が 1 だと、データの OVF の値は無視され、PCR.OVF は書き込みによって更新されない。読み出しには 0 が返る。 OVRO はオーバーフロー情報を変更することなく PCR を更新するためのものである。 PCR.OVF はハードウェアが常に最新状態に保つので、次の PCR 読み出し時にはその時点でのオーバーフロー情報が返される。 PCR.OVRO は SPARC64 IXfx 独自のフィールドである (impl. dep. #207)。 |    |     |     |     |     |     | の<br>によっ<br>oのも<br>の PCR |     |

| 24:22 | NC    | カウンタペアの数。このフィールドはリードオンリーで、SPARC64 IXfx では3(カウンタペア4つ)である。                                                                                                                                                                                                                                                             |    |     |     |     |     |     |                          |     |

| 20:18 | SC    | PICにマッピングするカウンタペア<br>を更新し、読み出しでは現在のマッ                                                                                                                                                                                                                                                                                |    |     | _   |     |     | C O | マッ                       | ピング |

| ビット   | フィールド | 説明                                                                                                                                                              |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17:11 | SU    | PIC<63:32> で計測するイベントを指定する。書き込みで設定を更新し、読みだしでは現在の設定が返される。JPS1 Commonality の仕様を 1 ビット拡張し、7 ビットのフィールドとする。                                                           |

| 10:4  | SL    | PIC<31:0> で計測するイベントを指定する。書き込みで設定を更新し、読みだしでは現在の設定が返される。JPS1 Commonality の仕様を 1 ビット拡張し、7 ビットのフィールドとする。                                                            |

| 3     | ULRO  | SU, SL の変更禁止。書き込みの際、書き込もうとするデータの ULRO が $0$ だと、データの SU, SL で PCR.SU, PCR.SL が更新される。データの ULRO が $1$ だと、データの SU, SL は無視され、PCR.SU, PCR.SL は更新されない。 読み出しには $0$ が返る。 |

|       |       | ULRO は、SU, SL の設定を変更することなく PIC のマッピングを変更する<br>ためのものである。SPARC64 IXfx 独自のフィールドである (impl. dep.<br>#207)。                                                           |

| 2     | UT    | ユーザモード。PSTATE.PRIV=0で発生したイベントを計測する。                                                                                                                             |

| 1     | ST    | システムモード。PSTATE.PRIV=1で発生したイベントを計測する。                                                                                                                            |

|       |       | PCR.UT と PCR.ST がともに 1 の場合、すべての場合で発生したイベントが計測される。 PCR.UT と PCR.ST がともに 0 の場合、計測は行われない。 PCR.UT と PCR.ST はグローバルなフィールドで、すべての PIC に対して適用される。                        |

| 0     | PRIV  | 特権アクセス。PCR.PRIV=1のとき、非特権モード(PSTATE.PRIV=0)でRDPCR, WRPCR, RDPIC, WRPICを実行すると <i>privileged_action</i> 例外が通知される。                                                  |

|       |       | PCR.PRIV=0のときは、PSTATE.PRIV=0でRDPCRの実行は正常に完了し、WRPCRはPCR.PRIVを変更しようとすると(1を書き込もうとすると) privileged_action が通知される (impl. dep. #250)。                                  |

#### Performance Instrumentation Counter (PIC) Register (ASR 17)

PIC は JPS1 Commonality に準拠する。

SPARC64 IXfx では PIC は 4 組実装される。 PCR.SC で指定された PIC が ASR 17 で アクセスできる。 PIC のアクセスは PICU, PICL カウンタのペアにアクセスすること になる。 PICU, PICL のエンコーディングについては Appendix Q を参照。

オーバフロー発生時、カウンタは0にラップアラウンドし、SOFTINT レジスタのビット 15 に1 がセットされ、interrupt level-15 例外が通知される。カウンタオーバフローのトラップは、カウンタ値が FFFF FFFF $_{16}$  から0 に更新される際に通知される。同時に複数のオーバーラップが起きたときは、複数のオーバーラップビットが1にセットされる。すでに1 にセットされているオーバーフロービットは1 のまま変更されない。

オーバーフロービットは、ソフトウェアが対応する PCR.OVF に 0 を書き込むことでクリアされる。ソフトウェアは 1 を書き込むことができるが、この書き込みによるオーバーフロートラップは発生しない。

#### Dispatch Control Register (DCR) (ASR 18)

SPARC64 IXfx は DCR を実装しない。DCR の読み出しには 0 が返り、書き込みは無視される。DCR は特権レジスタである。非特権モードでのアクセスには privileged\_opcode 例外が通知される。

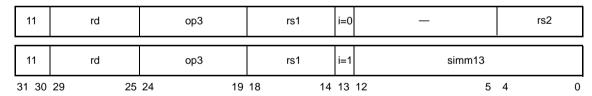

#### Extended Arithmetic Register (XAR) (ASR 29)

新規に追加された非特権レジスタである。命令フィールドを拡張するためのレジスタである。命令のレジスタ指定フィールド (rs1, rs2, rs3, rd) の上位 3 ビットと、SIMD 演算するかどうかを指定する。

XAR は 2 命令分のレジスタ指示フィールドを持つ。1 命令目、2 命令目用の各フィールドには V (valid) ビットがあり、その他のフィールドは v=1 のときに有効である。レジスタフィールドには整数 / 浮動小数点数の区別はなく、任意のレジスタと結合する。

トラップ時には、XAR の内容は TXAR [TL] にセーブされ、XAR は allo になる。セーブされるのは、実行中の命令の実行直前の XAR の値である。

**Note** - Tcc の条件が成立してトラップした時も、Tcc 実行直前の XAR の内容がセーブされる。

|   | 0     | f_v | 0     | f_simd | f_u | urd | f_ur | s1 | f_urs | 2 | f_urs3 |   | s_v | (  | )  | s_simd | s_urd | s_urs1 |   | s_urs | 2 | s_u | rs3 |

|---|-------|-----|-------|--------|-----|-----|------|----|-------|---|--------|---|-----|----|----|--------|-------|--------|---|-------|---|-----|-----|

| 6 | 63 32 | 31  | 30 29 | 28     | 27  | 25  | 24   | 22 | 21 19 | ) | 18 1   | 6 | 15  | 14 | 13 | 12     | 11 9  | 8 6    | ; | 5 3   |   | 2   | 0   |

TABLE 5-3 XAR のフィールド

| ビット   | フィールド  | 説明                                                                                                                            |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| 63:32 | _      | Reserved. このフィールドに 0 以外の値を書くと、illegal_instruction 例外が通知される。                                                                   |

| 31    | f_v    | $f_{-}$ で始まるフィールドの内容が有効かどうかを示す。 $f_{-}v=1$ なら、 $1$ 番目に実行される命令に $f_{-}$ が適用される。 $1$ 番目の命令が完了すると、 $f_{-}$ フィールドはすべて $0$ クリアされる。 |

| 30:29 | _      | Reserved. このフィールドに 0 以外の値を書くと、illegal_instruction 例外が通知される。                                                                   |

| 28    | f_simd | $f_simd=1$ なら、 $1$ 番目に実行される命令は SIMD 命令として実行される。 $f_simd=0$ なら non-SIMD で実行される。                                                |

| 27:25 | f_urd  | 1 番目の命令の rd の拡張フィールド。                                                                                                         |

| 24:22 | f_urs1 | 1番目の命令の rs1 の拡張フィールド。                                                                                                         |

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 29

TABLE 5-3 XAR のフィールド

| ビット   | フィールド  | 説明                                                                                                                    |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------|

| 21:19 | f_urs2 | 1番目の命令の rs2 の拡張フィールド。                                                                                                 |

| 18:16 | f_urs3 | 1番目の命令の rs3 の拡張フィールド。                                                                                                 |

| 15    | s_v    | $s_{-}$ で始まるフィールドの内容が有効かどうかを示す。 $s_{-}v=1$ なら、2番目に実行される命令に $s_{-}$ が適用される。2番目の命令が完了すると、 $s_{-}$ フィールドはすべて $0$ クリアされる。 |

| 14:13 | _      | Reserved. このフィールドに 0 以外の値を書くと、illegal_instruction 例外が通知される。                                                           |

| 12    | s_simd | $s\_simd=1$ なら、 $2$ 番目に実行される命令は SIMD 命令として実行される。 $s\_simd=0$ なら non-SIMD で実行される。                                      |

| 11:9  | s_urd  | 2番目の命令の rd の拡張フィールド。                                                                                                  |

| 8:6   | s_urs1 | 2番目の命令の rs1 の拡張フィールド。                                                                                                 |

| 5:3   | s_urs2 | 2番目の命令の rs2 の拡張フィールド。                                                                                                 |

| 2:0   | s_urs3 | 2番目の命令の rs3 の拡張フィールド。                                                                                                 |

#### 本仕様書における XAR の記述について

Table 5-3 のフィールド名以外に以下の別名表記も用いる。

#### ■ メモリアクセス用

| 別名              | 実際のフィールド                       |

|-----------------|--------------------------------|

| XAR.f_dis_hw_pf | XAR.f_urs3<1>                  |

| XAR.s_dis_hw_pf | XAR.s_urs3<1>                  |

| XAR.f_sector    | <pre>XAR.f_urs3&lt;0&gt;</pre> |

| XAR.s_sector    | XAR.s_urs3<0>                  |

#### ■ SIMD FMA 用

| 別名               | 実際のフィールド                      |

|------------------|-------------------------------|

| XAR.f_negate_mul | <pre>XAR.f_urd&lt;2&gt;</pre> |

| XAR.s_negate_mul | XAR.s_urd<2>                  |

| XAR.f_rs1_copy   | XAR.f_urs3<2>                 |

| XAR.s_rs1_copy   | XAR.s_urs3<2>                 |

#### 総称

1命令目、2命令目の区別なしに記述する場合は XAR.f\_v, XAR.s\_v の値により 1命令目、2命令目のどちらかを選択したものとする。

| 記述法            | XAR.f_v = 1 のとき  | XAR.f_v = 0 かつ XAR.s_v = 1 のとき |

|----------------|------------------|--------------------------------|

| XAR.v          | XAR.f_v          | XAR.s_v                        |

| XAR.urd        | XAR.f_urd        | XAR.s_urd                      |

| XAR.urs1       | XAR.f_urs1       | XAR.s_urs1                     |

| XAR.urs2       | XAR.f_urs2       | XAR.s_urs2                     |

| XAR.urs3       | XAR.f_urs3       | XAR.s_urs3                     |

| XAR.dis_hw_pf  | XAR.f_dis_hw_pf  | XAR.s_dis_hw_pf                |

| XAR.sector     | XAR.f_sector     | XAR.s_sector                   |

| XAR.negate_mul | XAR.f_negate_mul | XAR.s_negate_mul               |

| XAR.rs1_copy   | XAR.f_rs1_copy   | XAR.s_rs1_copy                 |

#### XAR 動作

XAR を参照する命令と参照しない命令がある。

ここでは XAR を参照する命令のことを、"XAR 対象命令" と呼ぶ。どの命令が XAR 対象命令かは、TABLE A-2 (page 59) を参照。

- XAR 対象でない命令は、その命令の実行時に XAR.v=1 だと *illegal\_action* 例外が通知される。

- XAR 対象命令の動作は、

- XAR.v=1 のとき、XAR.urs1, XAR.urs2, XAR.urs3, XAR.urd がそれぞれ命令フィールドの rs1.rs2.rs3.rd と結合する。

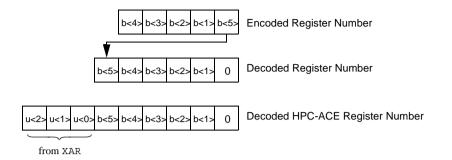

整数レジスタでは、XARのフィールドを上位3ビット、命令フィールドを下位5ビットとする計8ビットで指定されるレジスタを使用する。

浮動小数点レジスタでは、XAR のフィールドを上位 3 ビットとし、命令フィールドの 5 ビットを倍精度レジスタのエンコーディング方式にしたがってデコードした 6 ビットを下位とする計 9 ビットで指定されるレジスタを使用する。浮動小数点レジスタのエンコーディングの詳細は "Floating-Point Register Number Encoding" (page 20) を参照。

- XAR.f\_v=1 なら XAR.f\_urs1, XAR.f\_urs2, XAR.f\_urs3, XAR.f\_urd が使われる。

- XAR.f\_v=0かつXAR.s\_v=1ならXAR.s\_urs1, XAR.s\_urs2, XAR.s\_urs3, XAR.s\_urdが使われる。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 31

- XAR の値は1回のみ有効。XAR を参照した命令が完了すると、XAR の関連フィール ドは all0 になる。

- XAR 対象命令であっても、以下のどれかにあたる場合 illegal action が通知される。

- xq[32] 以上の整数レジスタを指定した場合。

- rs1 を使わない命令に対して、urs1≠0 を指定した場合。 rs2. rs3. rd についても同様である。 rs2フィールドをsimm13やfcn などの即値として使う命令で、urs2≠0の場合

- も illegal action が通知される。

- FDIV(S,D), FSQRT(S,D) で rd に f [256] 以上を指定した場合。

- SIMD拡張されない命令(整数演算も含む)に対してXAR.simd=1を指示した場

- XAR.simd = 1 で f [256] 以上を指定した場合。 ただし FMADD は、rs1, rs2 に f [256] 以上を指定可能。 XAR.urs3<2>, XAR.urd<2> も1になってもよいが、これはf[256]以上の指定 ではなく、別の意味に解釈される。詳細は "FMADD の SIMD 拡張" (page 73) を

- ld/st/atomic 命令で XAR.urs3<2>≠0 のとき。

後続1命令のレジスタ番号を指示する場合、1st を使っても 2nd を使ってもよい。

Programming Note - WRXAR 命令を使えばXAR.f v, XAR.s vどちらでも任意に 1 を設定できる。sxar1命令ではXAR.f v=1になる。

XAR.f v=0のときは、f simd, f urs1, f urs2, f urs3, f urdの各フィールド に0でない値があっても無視される。命令実行後、各フィールドの値がどうなるかは 未定義である。XAR.s v = 0 のときは、s simd, s urs1, s urs2, s urs3, s urdの各フィールドに0でない値があっても無視される。命令実行後各フィールドの値が どうなるかは未定義である。

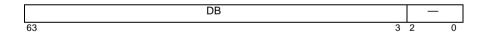

#### Extended Arithmetic Register Status Register (XASR) (ASR 30)

新規追加非特権レジスタ。

| ビット  | フィールド    | 属性 | 説明                                     |

|------|----------|----|----------------------------------------|

| 63:9 | _        | R  | Reserved.                              |

| 8    | xgd      | RW | xg[0]-xg[31] が更新されると、xgd=1になる。         |

| 7:0  | xfd<7:0> | RW | 浮動小数点レジスタが更新されると、対応するビットに1が<br>セットされる。 |

コンテキストスイッチ時に、レジスタを保存する必要があるかどうかを判断するために使用する。拡張レジスタを更新すると、対応するビットが1になる。

- V9 定義の整数レジスタの更新を示すフラグはない。

- xg[0] xg[31] を更新すると XASR.xgd = 1 がセットされる。

- 浮動小数点レジスタを更新すると、対応する xfd<i>=1がセットされる。レジスタと xfd のビット対応は以下の通り。

| 浮動小数点レジスタ       | 対応する XASR のビット |

|-----------------|----------------|

| f[0] - f[62]    | xfd<0>         |

| f[64] - f[126]  | xfd <l></l>    |

| f[128] - f[190] | xfd<2>         |

| f[192] - f[254] | xfd<3>         |

| f[256] -f[318]  | xfd<4>         |

| f[320] - f[382] | xfd<5>         |

| f[384] - f[446] | xfd<6>         |

| f[448] - f[510] | xfd<7>         |

**Programming Note** - xfd[0] は V9 FPR を更新したときにセットされる。このとき、V9 の FPRS も同時に更新される。例えば f[15] を更新した場合は、FPRS.dl = 1 と XASR.xfd<0>=1 がセットされる。

**Implementation Note** - MOVr, MOVcc, FMOVr, FMOVcc 命令で条件が不成立のとき、対応する XASR のビットが 1 になるかどうかは実装に依存する。

#### Trap XAR Registers (TXAR) (ASR 31)

新規追加特権レジスタ。フィールドは XAR と同じである。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 3:

TXAR はトラップ時に XAR が保存されるレジスタである。レジスタフィールドの定義は XAR と同じである。TXAR[1] – TXAR [MAXTL] までのレジスタが定義されている。TL > 0 のときは、TXAR [TL] が見える。TL を変更すると、変更直後の命令から新しいTL に対応する TXAR [TL] が read/write できる。

TL = 0で read/write すると *illegal\_instruction* が通知される。 *Reserved* フィールドに 0 でない値を書くと *illegal\_instruction* が通知される。

## 5.2.12 Registers Referenced Through ASIs

本節では JPS1 Commonality の 5.2.12 で定義されている ASI レジスタについてのみ記述する。その他の ASI レジスタについては Appendix L を参照。

#### Data Cache Unit Control Register (DCUCR)

ASI  $45_{16}$  (ASI\_DCU\_CONTROL\_REGISTER), VA =  $00_{16}$ .

DCUCR は、命令、プリフェッチ、書き込みとデータキャッシュ、MMU、ウォッチポイントなど、メモリアクセスに関連するハードウェアの機能を制御するためのレジスタである。SPARC64 IXfx の DCUCR は JPS1 Commonality で定義された仕様をほぼ実装している。

DCUCR のビット配置を FIGURE 5-3 に、ビットの説明を TABLE 5-4 に示す。

| -  | _  | 0  | 0  | (  | )  | WEAK_SPCA | _  | -  | VI | M  | PR | PW | VR | VW | _  | _ | DM | IM | 0 | 0 |

|----|----|----|----|----|----|-----------|----|----|----|----|----|----|----|----|----|---|----|----|---|---|

| 63 | 50 | 49 | 48 | 47 | 42 | 41        | 40 | 33 | 32 | 25 | 24 | 23 | 22 | 21 | 20 | 4 | 3  | 2  | 1 | 0 |

FIGURE 5-3 DCUCR (ASI 45<sub>16</sub>)

TABLE 5-4 DCUCR のフィールド

| ビット    | フィールド      | 属性 | 説明                                                                                                                                                                                   |

|--------|------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:50  | _          |    | Reserved                                                                                                                                                                             |

| 49:48  | CP, CV     | R  | SPARC64 IXfx では実装されない。読み出しには 0 が返り、書き込みは無視される。                                                                                                                                       |

| 47:42  | impl. dep. | R  | 読み出しには0が返り、書き込みは無視される。                                                                                                                                                               |

| 41     | WEAK_SPCA  | RW | 投機的なメモリアクセスの抑止 (impl. dep. #240)。 WEAK_SPCA に 1 がセットされると、分岐予測が行われなくなる。命令のプリフェッチは常に分岐しない方向に行われる。分岐命令以降のロード、ストアは、分岐方向が確定するまで行われない。ハードウェアプリフェッチ機構は停止され、プリフェッチ命令はストロングプリフェッチも含めすべて無効となる。 |

|        |            |    | 命令プリフェッチのアクセス範囲は CPU 内部リソース<br>によって決まる一定範囲内に留まるので、<br>weak_spca=1 ではメモリアクセスの範囲は推定可能で<br>ある。                                                                                          |

| 40:33  | PM<7:0>    |    | Reserved.                                                                                                                                                                            |

| 32:25  | VM<7:0>    | RW | Data Watchpoint Register のマスクを指定する。<br>SPARC64 IXfx では Data Watchpoint Register は物理アドレス、論理アドレス共用。                                                                                    |

| 24, 23 | PR, PW     | RW | Data Watchpoint Register の値を物理アドレスと解釈して<br>VMで指定されたアドレスにread またはwriteアクセスする<br>と <i>PA_watchpoint</i> 例外が通知される。                                                                      |

| 22, 21 | VR, VW     | RW | Data Watchpoint Register の値を論理アドレスと解釈して<br>VMで指定されたアドレスに read または write アクセスする<br>と VA_watchpoint 例外が通知される。                                                                          |

| 20:4   | _          |    | Reserved.                                                                                                                                                                            |

| 3      | DM         | RW | Data MMU 有効化。DM を 0 にセットすると、データアクセス時にアドレス変換が行われない。このとき、論理アドレスはそのまま物理アドレスとして使われる。                                                                                                     |

| 2      | IM         | RW | 命令 MMU 有効化。IM を 0 にセットすると、データアクセス時にアドレス変換が行われない。このとき、論理アドレスはそのまま物理アドレスとして使われる。                                                                                                       |

| 1      | DC         | R  | SPARC64 IXfx では実装されない。読み出しには 0 が返り、書き込みは無視される。                                                                                                                                       |

| 0      | IC         | R  | SPARC64 IXfx では実装されない。読み出しには 0 が返り、書き込みは無視される。                                                                                                                                       |

**Implementation Note** - DCUCR.WEAK\_SPCA = 1 のとき、CTI 以降の命令プリフェッチは、最大でもその CTI から 1KB を越えることはない。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 35

**Programming Note** - 投機メモリアクセス抑止を確実に行うために、システムソフトウェアは DCUCR. WEAK SPCA = 1 に設定後直ちに membar #Sync を発行すること。

**Programming Note -** SPARC64 IXfx では DCUCR の IM (IMMU enable), DM (DMMU Enable) 変更は以下の命令列で行う必要がある。

# DCUCR.IM update

stxa DCUCR

flush

# DCUDR.DM update

stxa DCUCR

membar #sync

#### **Data Watchpoint Registers**

レジスタ名 ASI WATCHPOINT

ASI 58<sub>16</sub> VA 38<sub>16</sub>

アクセス種別 Supervisor Read/Write

| ビット  | フィールド | 属性 | 説明                       |

|------|-------|----|--------------------------|

| 63:3 | DB    | RW | ウォッチポイントアドレス (VA, PA 共用) |

JPS1 Commonality の TABLE 5-18 で、ウォッチポイントの対象は translating ASI, bypass ASI、であると定義している。しかしこの表の定義に従うと、実装依存 ASI や未定義 ASI もウォッチポイントの対象となってしまうので、SPARC64 IXfx では translating, bypass, nontranslating を定義し直した (TABLE L-1 (page 214) を参照)。この表で translating, bypass と定義された ASI がウォッチポイントの対象となる。

JPS1 Commonality ではウォッチポイントを、論理アドレス・物理アドレス独立に設定できるが、SPARC64 IXfx では、アドレスの指定は一つだけで、そのアドレスを論理アドレス・物理アドレスと解釈した場合にマッチするかどうかを監視するよう、仕

様を変更する。JPS1 Commonality の ASI\_VA\_WATCHPOINT (ASI =  $58_{16}$ , VA =  $38_{16}$ ) を ASI\_WATCHPOINT という名前にし、ASI\_PA\_WATCHPOINT (ASI =  $58_{16}$ , VA =  $40_{16}$ ) は 削除する。

#### **Compatibility Note** – この変更は SPARC JPS1 非互換である。

ウォッチポイントの有効・無効の指定方法は、SPARC JPS1 仕様に準拠し、DCUCR.VR, DCUCR.VW, DCUCR.PR, DCUCR.PW で指定する。DCUCR.VR またはDCUCR.VW に 1 がセットされていると、DB を論理アドレスと解釈してマッチした場合に VA\_watchpoint が通知され、DCUCR.PR または DCUCR.PW に 1 がセットされていると、DB を物理アドレスと解釈してマッチした場合に PA\_watchpoint が通知される。論理アドレス・物理アドレスどちらでもマッチした場合は、VA\_watchpoint が通知される。

ウォッチポイントが有効である ASI 空間の一覧が JPS1 Commonality の TABLE 5-18 で 定義されているが、この表は SPARC64 IXfx で未実装である ASI も含まれている。 SPARC64 IXfx は、未実装である translating ASI ではウォッチポイントの検出は行わず、アクセスすると data\_access\_exception が通知される。

物理アドレスとしてマッチしているかどうかを判定する際、DB<63:41> は無視される。

SIMD ロード、SIMD ストア命令では、basic 側、extended 側のどちらでもウォッチポイントを検出する。アドレスとマスクが basic 側のアドレスとアクセス長にマッチすれば、basic 側の  $VA\_$  watchpoint,  $PA\_$  watchpoint が通知され、アドレスとマスクが extended 側のアドレスとアクセス長にマッチすれば、extended 側の  $VA\_$  watchpoint,  $PA\_$  watchpoint が通知される。

ウォッチポイントの信頼性を下げる機能は SPARC64 IXfx には実装されていない (impl. dep. #244)。

以下の命令については、ウォッチポイントの設定と検出に関する特例がある。詳細は それぞれの命令を参照。

- Appendix A.4, "Block Load and Store Instructions (VIS I)"

- Appendix A.30, "Load Quadword, Atomic [Physical]"

- Appendix A.42, "Partial Store (VIS I)"

- Appendix A.77, "Store Floating-Point Register on Register Condition"

- Appendix A.79, "Cache Line Fill with Undetermined Values"

- Appendix F.5.1, "Trap Conditions for SIMD Load/Store"

#### Instruction Trap Register

SPARC64 IXfx は命令トラップレジスタを実装する (impl. dep. #205)。

Ver 12, 2 Dec. 2013 F. Chapter 5 Registers 37

SPARC64 IXfx では、命令キャッシュに CALL, 条件分岐命令 (BPCC, FBPfcc, Bicc, BPr) が保持される際、下位 11 ビットは命令定義通りメモリ上と同じデータが保存される (impl. dep. #245)。

## 5.2.13 Floating-Point Deferred-Trap Queue (FQ)

SPARC64 IXfx は浮動小数点演算の遅延トラップキューを実装しない (impl. dep. #24). RDPR 命令で FQ を読み出そうとすると、*illegal\_instruction* 例外を通知する (impl. dep. #25)。

# 5.2.14 IU Deferred-Trap Queue

SPARC64 IXfx は整数ユニットの遅延トラップキューを実装しない (impl. dep. #16)。

# Instructions

### 6.1 Instruction Execution

SPARC64 IXfx は先進のスーパスケーラ機構を実装した SPARC V9 プロセッサである。1 サイクルで複数の命令を発行・実行することができる。SPARC64 IXfx のプログラムセマンティクスは逐次命令実行モデルなので、この節の事項はソフトウェアには見えないが、効率と正確性を知る上で重要なのでここで説明する。

#### 6.1.1 Data Prefetch

SPARC64 IXfx はプログラムの命令順序通りではなく、投機的に命令実行を行う(アウトオブオーダ)。投機実行された命令列が実行されるべき命令でないことがわかると、命令実行は取り消されるが、投機実行した命令列のメモリアクセスは取り消すことができない。SPARC64 IXfx の投機メモリアクセスの方針は以下の通りである。

- 1. あるメモリ操作 x のメモリアドレスが揮発性 (volatile) のとき (location[x]), SPARC64 IXfx は location[x] に対するプリフェッチを行わない。location[x] のフェッチは、x が確実に実行される (committable) と判明した後で行われる。

- 2. あるメモリ操作 x のメモリアドレスが不揮発性 (nonvolatile) のとき (location[x]), SPARC64 IXfx は location[x] に対するプリフェッチを行うかもしれない。その際は以下の方針に従う。

- a. メモリ操作 x がストアセマンティクスの操作で、キャッシャブル領域のアクセスの場合、データを排他的使用権を獲得するところまで行う。ストアセマンティクス以外の操作では、ノンキャッシャブルであってもプリフェッチを行う。

- b. アトミック操作(CAS(X)A, LDSTUB, SWAP)のプリフェッチは行われない。

SPARC64 IXfx は投機的なロード命令の実行を防ぐための機構を2つ実装している。

Ver 12, 2 Dec. 2013 F. Chapter 6 Instructions 39

- 1. ある種のページや I/O 空間に対しては投機アクセスを行わない。投機的なアクセスを禁止する場合は、PTE の E (side-effect) ビットに 1 をセットする。E ビットがセットされているページへのアクセスは、そのアクセスが投機的でなくなるまで 待機させられる。詳細は Appendix F を参照。

- 2. ロードを強制的にプログラム順に行わせる ASI\_PHYS\_BYPASS\_WITH\_EBIT [\_L] (ASI =  $15_{16}$ ,  $1D_{16}$ ) は投機的には実行されない。

#### 6.1.2 Instruction Prefetch

SPARC64 IXfx は、命令の供給が間に合わず実行が止まるということが極力起こらないよう、命令プリフェッチを行う。分岐予測の結果によっては、実際には実行しない命令列をプリフェッチすることがある。さらに、投機実行した命令がメモリアクセスをすることもある。命令プリフェッチや投機メモリアクセスによる例外を検出してもすぐには通知せず、その命令の直前の命令が完了してから通知される。1

## 6.1.3 Syncing Instructions

SPARC64 IXfx はある種の命令を sync 命令として扱う。sync 命令は実行するとパイプラインを数サイクルの間停止させるような命令である。sync 命令には pre sync と post sync の 2 種類がある。pre sync 命令は、プログラム順でその命令より前にある命令の実行が完了してから、その命令だけを実行完了し、その後で、後続命令を実行するような副次的効果を持つ命令である。post sync 命令は、プログラム順でその命令より後にある命令の発行を、その命令が実行完了するまで停止する副次的効果を持つ命令である。pre sync かつ post sync 属性を持つ命令も存在する。

SPARC64 IXfx では、ストアを除くすべての命令がプログラム順に完了する。ストアはその結果が global visible になる前に完了する (ストアの突き放し完了)。

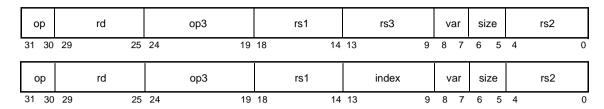

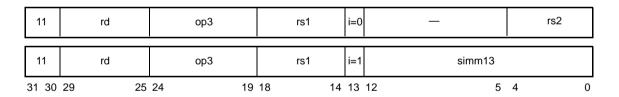

# 6.2 Instruction Formats and Fields

SPARC64 IXfx の命令フォーマットは 5 種類に大別される。そのうち 4 種類の命令フォーマットは JPS1 Commonality の Section 6.2 を参照。5 番目の命令フォーマットは SPARC64 IXfx 独自のフォーマットである。

<sup>1.</sup> ハードウェアのエラーやその他命令実行とは非同期に起きるエラーは、そのエラーを起こした命令がの完了を待たずに通知される。

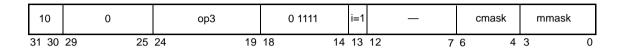

Format 5 (op = 2,  $op3 = 37_{16}$ ): FMADD, FPMADDX, FSELMOV, and FTRIMADD (in place of IMPDEP2A and IMPDEP2B)

FIGURE 6-1 Summary of Instruction Formats: Format 5

命令フィールドの説明は JPS1 Commonality の TABLE 6-1 を参照。Format 5 で追加された 4 つのフィールドの説明を下表に示す。

**TABLE 6-1** Format 5 の命令フィールドの解釈

| フィールド | 説明                                                                    |

|-------|-----------------------------------------------------------------------|

| rs3   | この5ビットフィールドは、浮動小数点演算の3番目の入力浮動小数点<br>レジスタを示す。                          |

| var   | この2ビットフィールドは、浮動小数点積和演算の種類を指示するために使われるほか、Impdep2に定義された命令を選択するために使われる。  |

| size  | この2ビットフィールドは、浮動小数点積和演算のサイズを指示するために使われるほか、Impdep2に定義された命令を選択するために使われる。 |

| index | FTRIMADDd で係数テーブルを指示するために使われる。                                        |

# 6.3 Instruction Categories

## 6.3.3 Control-Transfer Instructions (CTIs)

実行制御命令には以下の種類がある。

- 条件分岐 (Bicc, BPcc, BPr, FBfcc, FBPfcc)

- 無条件分岐

- Call and link (CALL)

- Jump and link (JMPL, RETURN)

- Return from trap (DONE, RETRY)

- Trap (Tcc)

この仕様書では SPARC64 IXfx の CALL と JMPL 命令について説明する。それ以外の実行制御命令は JPS1 Commonality を参照。

#### CALL and JMPL Instructions

SPARC64 IXfx は PSTATE. AM = 0 のとき、PC の 64 ビットすべてをデスティネーションレジスタに書き込む。PSTATE. AM = 1 のときは上位 32 ビットをゼロにした値をデスティネーションレジスタに書き込む。

# 6.3.7 Floating-Point Operate (FPop) Instructions

FPop が fp\_exception\_other 例外を FSR.ftt = unfinished\_FPop で通知する正確な条件 は、Appendix B.6, "Floating-Point Nonstandard Mode" (page 139) で定義する。

### 6.3.8 Implementation-Dependent Instructions

SPARC64 IXfx は IMPDEP1, IMPDEP2 に、浮動小数点演算命令を定義している。JPS1 Commonality では FPop を "オペコードが FPop1 または FPop2 である命令"と定義しているので、IMPDEP の命令は FPop ではないことになる。

IMPDEP2 で定義された浮動小数点積和演算命令のうち FMADD, FMSUB, FNMSUB には 4 倍精度演算が定義されているが、SPARC64 IXfx では 4 倍精度演算は実装されないので、これらの命令を実行すると *illegal\_instruction* 例外が通知される。FNMADD だけは 4 倍精度演算が定義されていない。4 倍精度浮動小数点積和演算は SPARC V9 で必須の命令ではないので、システムソフトウェアはエミュレーションしなくてもよい。

SPARC64 IXfx で IMPDEP1, IMPDEP2 に追加された命令のうち、浮動小数点レジスタを使う以下の命令は、PSTATE.PEF = 0 または FPRS.FEF = 0 のときに実行すると、 fp disabled 例外が通知される。

$$\begin{split} & FCMP(GT,LE,EQ,NE,GE,LE)E(s,d), \ FCMP(EQ,NE)(s,d), \ FMAX(s,d), \ FMIN(s,d), \\ & FRCPA(s,d), \ FRSQRTA(s,d), \ FTRISSELd, \ FTRISMULd, \ FTRIMADDd, \\ & FSELMOV(s,d), \ F\{N\}M(ADD,SUB)(s,d), \ FPMADDX\{HI\}, \ ST\{D\}FR \end{split}$$

これらは FPop ではないので、*Reserved* であるオペコードを実行しようとすると、JPS1 Commonality 6.3.9 で定義されている通り、*illegal\_instruction* 例外が通知される。また、これらの命令のうち FPMADDX{HI}, ST{D}FR 以外は、JPS1 Commonality 6.3.7 の FPop と同様に FSR を更新する。FTRISSELd, FSELMOV(s,d) は fp\_exception\_ieee\_754 例外を通知しない命令だが、実行が完了すると FSR.cexc の全フィールドに 0 をセットし、FSR.aexc は変更しない。

# Traps

# 7.1 Processor States, Normal and Special Traps

JPS1 **Commonality** ではこの節で CPU のステートと遷移を定義しているが、 SPARC64™ IXfx Extensions では Appendix O.1, "*リセット種類*" (page 247) で定義しているので、そちらを参照されたい。

## 7.1.1 RED state

Appendix O.2.1, "RED\_state" (page 250) も参照。

#### RED\_state Trap Table

RED\_state 用のトラップテーブルは実装依存のアドレス RSTVaddr に配置される。RSTVaddr の値はある実装に対しては固定となっており、SPARC64 IXfx では論理アドレス FFFF FFFF F000 0000 $_{16}$ 、物理アドレス 0000 01FF F000 0000 $_{16}$  である (impl. dep. #114)。

#### RED\_state Execution Environment

RED\_state では CPU はある制約下で動作するが、このためにいくつかの CPU 制御用レジスタの値は固定値で上書きされる。

Note - 遷移をアトミックに行うため、値は上書きであって代入ではない。

RED state での SPARC64 IXfx の動作は以下の通りである (impl.dep. #115)

Ver 12, 2 Dec. 2013 F. Chapter 7 Traps 43

- RED\_state である間は、ITLB によるアドレス変換機能は無効となる。DTLB によるアドレス変換は RED\_state 遷移直後は無効だが、RED\_state 中にソフトウェアによって有効にすることができる。RED\_state 中でも、ASI レジスタ経由でTLB を参照・変更する機能は有効である。

- TLB によるアドレス変換が無効である間、すべてのメモリアクセスはノンキャッシャブル、ストロングオーダとして扱われる。

- XIR はマスクされないので、XIR を受けると例外を通知する。

**Note** – CPU 内のエラーにより RED\_state に入った場合、ソフトウェアは致命的なエラーからの復旧やエラーを起こしたコンポーネントを無効にするなどの処理を行うべきである。リセット後に RED\_state に入った場合、ソフトウェアはシステムを実行状態にするためのセットアップを行うこと。

#### 7.1.2 error\_state

プロセッサは、トラップレベルが最大 (TL = MAXTL) のときにトラップが起きると error\_state に遷移する (impl. dep. #39)。

CPU は、CPU 内部で生成される *watchdog\_reset* (WDR) によって error\_state に遷移するが、WDR を抑止し、error\_state で留まるように設定することもできる (impl. dep #40, #254)。

# 7.2 Trap Categories

### 7.2.2 Deferred Traps

SPARC64 IXfx ではエラー処理の例外が deferred で通知されることがある。詳細は Appendix P.2.2, "*エラー検出時の動作*" (page 263) または Appendix P.4.3, "*ADE* トラップ発生した時の命令の実行状況" (page 283) を参照。

### 7.2.4 Reset Traps

SPARC64 IXfx は命令完了が約 6.7 秒の間行われない場合、watchdog reset (WDR) 例外を通知する。

### 7.2.5 Uses of the Trap Categories

SPARC64 IXfx では、命令実行に同期して起きる例外はすべて precise である (impl. dep. #33)。

複数のメモリアクセスとして実行される命令(LDD(A), STD(A), LDSTUB, CASA, CASXA, SWAP など)が、最初のアクセスの後で致命的なエラーを起こした場合、precise で通知される。

# 7.3 Trap Control

#### 7.3.1 PIL Control

SPARC64 IXfx はシステムからのインタラプト要求を受信すると、 *interrupt\_vector\_trap* ( $TT = 60_{16}$ ) を通知する。トラップハンドラはインタラプト情報を読んだ後、SPARC V9 準拠のインタラプトで通知しなおす。この通知はソフトウェアが SOFTINT を書き込むことで行われる。詳細は JPS1 Commonality の Section 5.2.11 を参照。

SPARC64 IXfx は SPARC V9 準拠のインタラプトを受けると、PIL レジスタの値を チェックする。優先順位の条件を満たすインタラプトがある場合、SPARC64 IXfx は 新しい命令の発行をやめ、未完了の命令をすべてキャンセルし、トラップハンドラに 処理を移す。ただし、実行中の命令列が、より優先順位が高いトラップハンドラのも のである場合はこの限りではない。

SPARC64 IXfx はインタラプト要求を disrupting トラップとして処理する。

# 7.4 Trap-Table Entry Addresses

# 7.4.2 Trap Type (TT)

SPARC64 IXfx では以下のトラップを定義している (impl. dep. #35; impl. dep. #36)。

- async\_data\_error

- illegal\_action

- SIMD\_load\_across\_pages

Ver 12, 2 Dec. 2013 F. Chapter 7 Traps 45

JPS1 Commonality のトラップ一覧にこれらを含めたものを TABLE 7-1, TABLE 7-2 に示す。TABLE 7-1 の網掛け部分は、SPARC64 IXfx では起こらないトラップである。

TABLE 7-1 SPARC64 IXfx のトラップ一覧 (TT 番号順) (1 of 2)

| SPARC V9<br>M/O | JPS1<br>M/O | トラップ名                         | тт                                   | % g 種類          | 優先順位      |

|-----------------|-------------|-------------------------------|--------------------------------------|-----------------|-----------|

| •               | •           | Reserved                      | 000 <sub>16</sub>                    | -NA-            | -NA-      |

| •               | •           | power_on_reset                | 001 <sub>16</sub>                    | AG              | 0         |

| 0               | •           | watchdog_reset                | 002 <sub>16</sub>                    | AG              | 1         |

| 0               | •           | externally_initiated_reset    | 003 <sub>16</sub>                    | AG              | 1         |

| •               | •           | software_initiated_reset      | 004 <sub>16</sub>                    | AG              | 1         |

| •               | •           | RED_state_exception           | 005 <sub>16</sub>                    | AG              | 1         |

| •               | •           | Reserved                      | $006_{16} - 007_{16}$                | -NA-            | -NA-      |

| •               | •           | instruction_access_exception  | 008 <sub>16</sub>                    | MG              | 5         |

| 0               | О           | instruction_access_MMU_miss   | 009 <sub>16</sub>                    | MG (impl. dep.) | 2         |

| 0               | •           | instruction_access_error      | $00A_{16}$                           | AG              | 3         |

| •               | •           | Reserved                      | $00B_{16}$ - $00F_{16}$              | -NA-            | -NA-      |

| •               | •           | illegal_instruction           | 010 <sub>16</sub>                    | AG              | 7         |

| •               | •           | privileged_opcode             | 011 <sub>16</sub>                    | AG              | 6         |

| O               | O           | unimplemented_LDD             | 012 <sub>16</sub>                    | AG              | 6         |

| 0               | O           | unimplemented_STD             | 013 <sub>16</sub>                    | AG              | 6         |

| •               | •           | Reserved                      | 014 <sub>16</sub> -01F <sub>16</sub> | -NA-            | -NA-      |

| •               | •           | fp_disabled                   | 020 <sub>16</sub>                    | AG              | 8         |

| O               | •           | fp_exception_ieee_754         | 021 <sub>16</sub>                    | AG              | 11        |

| O               | •           | fp_exception_other            | 022 <sub>16</sub>                    | AG              | 11        |

|                 |             | (ftt = unimplemented_FPop のみ) | 022 <sub>16</sub>                    | AG              | 8.2       |

| •               | •           | tag_overflow                  | 023 <sub>16</sub>                    | AG              | 14        |

| O               | •           | clean_window                  | $024_{16} - 027_{16}$                | AG              | 10        |

| •               | •           | division_by_zero              | 028 <sub>16</sub>                    | AG              | 15        |

| O               | O           | internal_processor_error      | 029 <sub>16</sub>                    | impl. dep.      | impl. dep |

| •               | •           | Reserved                      | $02A_{16}$ – $02F_{16}$              | -NA-            | -NA-      |

| •               | •           | data_access_exception         | 030 <sub>16</sub>                    | MG              | 12        |

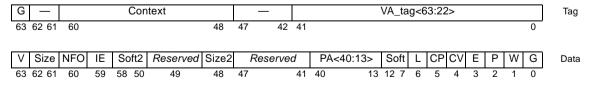

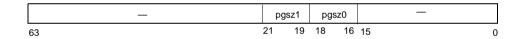

| O               | O           | data_access_MMU_miss          | 031 <sub>16</sub>                    | MG (impl. dep.) | 12        |