## **ASSP**

# **High Power Factor LED Driver IC for LED lighting**

## MB39C602

#### DESCRIPTION

MB39C602 is a flyback type switching regulator contorller IC. The LED current is regulated by controlling the switching on-time depending on the LED load.

It is most suitable for the general lighting applications, for example stocks of commercial and residential light bulbs and so on.

### **■ FEATURES**

- High power factor in Single Conversion

- · Helps to achieve high efficiency and low EMI by detecting auxiliary transformer zero current

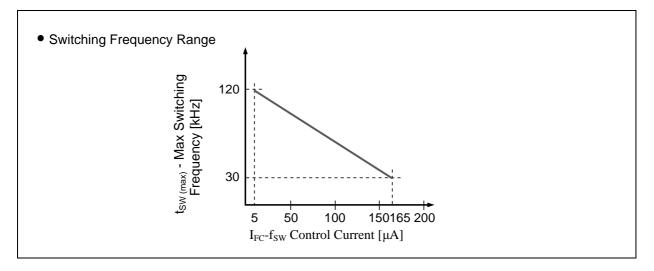

- Switching frequency setting depend on the FC pin current: 30 kHz to 120 kHz

- Control of the current of Primary Winding without the external sense resistor

- Built-in under voltage lock out function

- Built-in output over voltage protection function

- Built-in over temperature protection function

- Input voltage range VDD : 9V to 20V

- Input voltage range for LED lighting applications : AC110V<sub>RMS</sub>, AC230V<sub>RMS</sub>

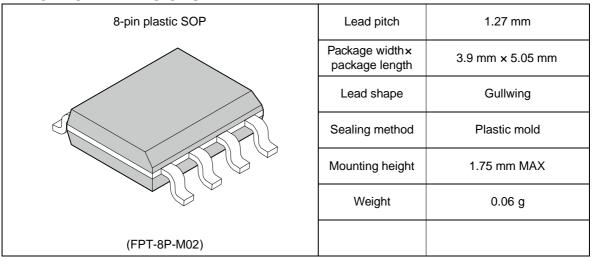

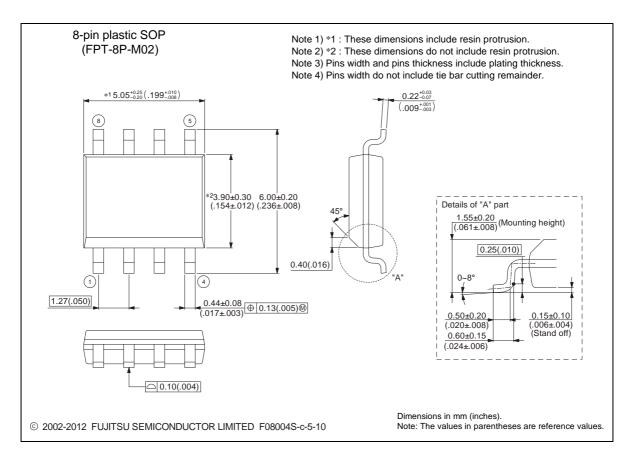

- Package : SOP-8 (3.9mm  $\times$  5.05mm  $\times$  1.75mm [Max])

### **■ APPLICATIONS**

- LED lighting

- PWM dimmable LED lighting

## Power Supply online Design Simulation Easy DesignSim

This product supports the web-based design simulation tool.

It can easily select external components and can display useful information.

Please access from the following URL.

http://edevice.fujitsu.com/pmic/en-easy/?m=ds

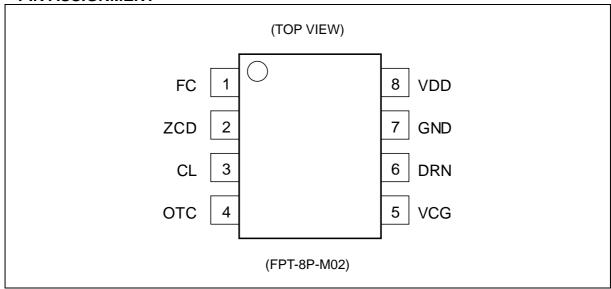

## **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTIONS**

| Pin No. | Pin Name | I/O | Description                                                      |

|---------|----------|-----|------------------------------------------------------------------|

| 1       | FC       | I   | Switching frequency setting pin.                                 |

| 2       | ZCD      | I   | Transformer auxiliary winding zero current detecting pin.        |

| 3       | CL       | I   | Pin for controlling peak current of transformer primary winding. |

| 4       | OTC      | I   | On-time control pin.                                             |

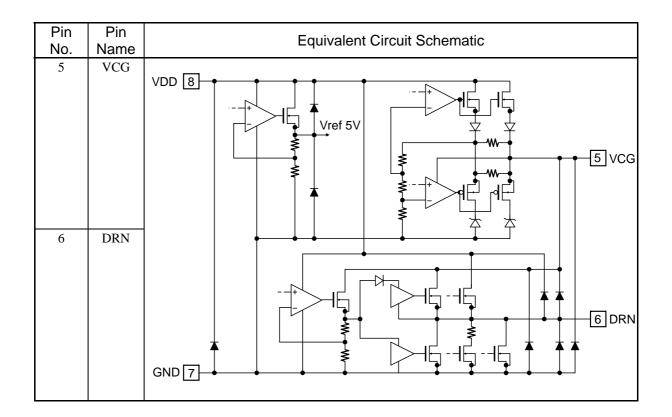

| 5       | VCG      | -   | External MOSFET gate bias pin.                                   |

| 6       | DRN      | О   | External MOSFET source connection pin.                           |

| 7       | GND      | -   | Ground pin.                                                      |

| 8       | VDD      | -   | Power supply pin.                                                |

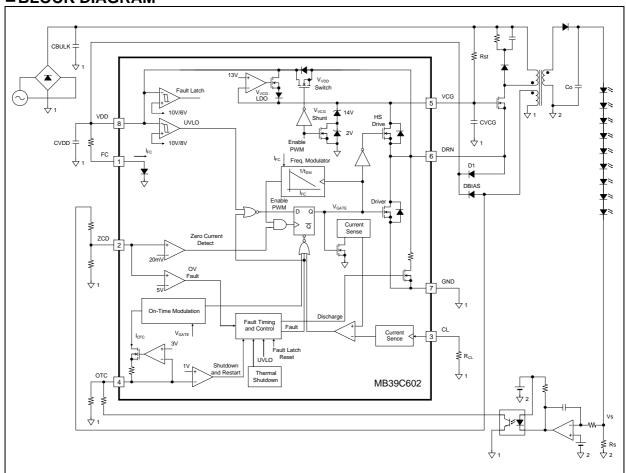

## **■BLOCK DIAGRAM**

### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol             | Condition                               | Ra      | ting  | Unit    |  |

|----------------------|--------------------|-----------------------------------------|---------|-------|---------|--|

| Farameter            | Symbol             | Condition                               | Min Max |       | J Silic |  |

| Power supply voltage | $V_{VDD}$          | VDD pin                                 | -0.3    | +25.0 | V       |  |

|                      | $V_{DRN}$          | DRN pin                                 | -       | 20    | V       |  |

|                      | $V_{VCG}$          | VCG pin                                 | -0.3    | +16.0 | V       |  |

| Input voltage        | $V_{ZCD}$          | ZCD pin                                 | -0.3    | +6.0  | V       |  |

| input voltage        | $V_{OTC}$          | OTC pin                                 | -0.3    | +6.0  | V       |  |

|                      | $V_{CL}$           | CL pin                                  | -0.3    | +6.0  | V       |  |

|                      | $V_{FC}$           | FC pin                                  | -0.3    | +2.0  | V       |  |

|                      | I <sub>VCG</sub>   | VCG pin                                 | -       | 10    | mA      |  |

| Input current        | $I_{OTC}$          | OTC pin                                 | -1      | 0     | mA      |  |

| input current        | $I_{CL}$           | CL pin                                  | -1      | 0     | mA      |  |

|                      | $I_{FC}$           | FC pin                                  | 0       | 1     | mA      |  |

|                      | $I_{DRN}$          | DRN pin                                 | -       | 800   | mA      |  |

| Output current       | $I_{\mathrm{DRN}}$ | DRN pin,<br>Pulsed 400ns, 2% duty cycle | -1.5    | +6.0  | A       |  |

| Power dissipation    | $P_{D}$            | Ta ≤ +25°C                              | -       | 800*  | mW      |  |

| Storage temperature  | $T_{STG}$          |                                         | -55     | +125  | °C      |  |

<sup>\*:</sup> The value when using two layers PCB.

4

Reference: θja (wind speed 0m/s): +125°C/W

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                               | Symbol           | Condition                                                 |      | Value |       | Unit  |

|-----------------------------------------|------------------|-----------------------------------------------------------|------|-------|-------|-------|

| r arameter                              | Symbol           | Condition                                                 | Min  | Тур   | Max   | Offic |

| VDD pin input voltage                   | VDD              | VDD pin                                                   | 9    | -     | 20    | V     |

| VCG pin input voltage                   | VCG              | VCG pin (from low-impedance source)                       | 9    | -     | 13    | V     |

| VCG pin input current                   | $I_{VCG}$        | VCG pin (from high-impedance source)                      | 10   | -     | 2000  | μΑ    |

| OTC pin resistance to GND               | R <sub>OTC</sub> | OTC pin                                                   | 25   | -     | 100   | kΩ    |

| CL pin resistance to GND                | $R_{CL}$         | CL pin                                                    | 24.3 | -     | 200.0 | kΩ    |

| ZCD pin resistance to auxiliary winding | $R_{ZCD}$        | ZCD pin Transformer auxiliary winding connection resistor | 50   | -     | 200   | kΩ    |

| VCG pin capacitance to GND              | $C_{VCG}$        | VCG pin                                                   | 33   | ı     | 200   | nF    |

| VDD pin bypass capacitance              | $C_{BP}$         | Ceramic capacitance to set between VDD and GND pin        | 0.1  | -     | 1.0   | μF    |

| Operating ambient temperature           | Та               | -                                                         | -40  | +25   | +85   | °C    |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

## **■ELECTRICAL CHARACTERISTICS**

$(Ta = +25^{\circ}C, V_{VDD} = 12V)$

|                         |                                               |                                 | Din |                                                                           | $1a = +25$ °C, $V_{VDD} =$ Value |       |       |      |

|-------------------------|-----------------------------------------------|---------------------------------|-----|---------------------------------------------------------------------------|----------------------------------|-------|-------|------|

| Parameter               |                                               | Symbol                          | No. | Condition                                                                 | Min Typ Max                      |       |       | Unit |

| VCG voltage (Operating) |                                               | VCG (OPERATING)                 | 5   | V <sub>VDD</sub> =14V,<br>I <sub>VCG</sub> =2.0mA                         | 13                               | 14    | 15    | V    |

|                         | VCG voltage (Disable)                         | VCG <sub>(DISABLED)</sub>       | 5   | $V_{OTC}=0V, I_{VCG}=26\mu A$                                             | 15                               | 16    | 17    | V    |

|                         | VCG voltage difference                        | ΔVCG                            | 5   | VCG (DISABLED) - VCG (OPERATING)                                          | 1.75                             | 2.00  | 2.15  | V    |

|                         | VCG Shunt input current                       | I <sub>VCG (SREG)</sub>         | 5   | V <sub>VCG</sub> =VCG <sub>(DISABLED)</sub> - 100mV, V <sub>OTC</sub> =0V | -                                | 12    | 26    | μА   |

|                         | VCG Shunt Load<br>Regulation                  | $\Delta VCG_{(SREG)}$           | 5   | V <sub>OTC</sub> =0V,<br>26μA <i<sub>VCG≤5mA</i<sub>                      | -                                | 125   | 200   | mV   |

| VDD and VCG<br>SUPPLY   | VCG LDO regulation voltage                    | VCG <sub>(LREG)</sub>           | 5   | V <sub>VDD</sub> =20V, I <sub>VCG</sub> =-2mA                             | -                                | 13    | -     | V    |

| SUFFLI                  | VCG LDO Dropout voltage                       | VCG (LREG, DO)                  | -   | VDD-VCG, V <sub>VDD</sub> =11V,<br>I <sub>VCG</sub> =-2mA                 | -                                | 2.0   | 2.8   | V    |

|                         | UVLO Turn-on threshold voltage                | VDD (ON)                        | 8   | -                                                                         | 9.7                              | 10.2  | 10.7  | V    |

|                         | UVLO Turn-off<br>threshold voltage            | VDD (OFF)                       | 8   | -                                                                         | 7.55                             | 8.00  | 8.50  | V    |

|                         | UVLO hysteresis                               | $\Delta VDD_{(UVLO)}$           | 8   | VDD (ON) - VDD (OFF)                                                      | 1.9                              | 2.2   | 2.5   | V    |

|                         | VDD switch on-resistance                      | R <sub>DS, ON (VDD)</sub>       | 6,8 | $V_{VCG}$ =12V, $V_{VDD}$ =7V, $I_{DRN}$ =50mA                            | -                                | 4*    | 10*   | Ω    |

|                         | Fault Latch Reset<br>VDD voltage              | VDD (FAULT RESET)               | 8   | -                                                                         | 5.6                              | 6.0   | 6.4   | V    |

|                         | Minimum switching period                      | t <sub>SW (HF)</sub>            | 6   | I <sub>FC</sub> =5μA                                                      | 7.215                            | 7.760 | 8.305 | μs   |

|                         | Maximum switching period                      | t <sub>SW (LF)</sub>            | 6   | I <sub>FC</sub> = 165μA                                                   | 31.5*                            | 35.0* | 38.5* | μs   |

|                         | DRN peak current                              | I                               | 6   | $I_{FC}=5\mu A, I_{CL}=100\mu A$                                          | -                                | 3*    | -     | A    |

| MODULATION              | Did v peak current                            | I <sub>DRN (peak)</sub>         | 6   | $I_{FC} = 5\mu A, I_{CL} = 30\mu A$                                       | -                                | 1*    | -     | A    |

| WODELMION               | Minimum peak current for R <sub>CL</sub> open | I <sub>DRN (peak, absmin)</sub> | 6   | R <sub>CL</sub> =OPEN                                                     | -                                | 0.45* | -     | A    |

|                         | ILIM blanking time                            | t <sub>BLANK (ILIM)</sub>       | 6   | $I_{FC}$ =5 $\mu$ A, $R_{CL}$ =100 $k\Omega$ , 1.2A pull-up on DRN        | -                                | 400*  | -     | ns   |

|                         | CL voltage                                    | $V_{CL}$                        | 3   | I <sub>FC</sub> =5μA                                                      | 2.94                             | 3.00  | 3.06  | V    |

|                         | FC voltage                                    | $V_{FC}$                        | 1   | $I_{FC}=10\mu A$                                                          | 0.34                             | 0.70  | 0.84  | V    |

|                         | Driver on-resistance                          | R <sub>DS (on) (DRN)</sub>      | 6,7 | I <sub>DRN</sub> =4.0A                                                    | -                                | 200*  | 400*  | mΩ   |

|                         | Driver off leakage current                    | I <sub>DRN (OFF)</sub>          | 6,7 | V <sub>DRN</sub> =12V                                                     | -                                | 1.5   | 20.0  | μΑ   |

| DRIVER                  | High-side driver on-resistance                | R <sub>DS (on) (HSDRV)</sub>    | 5,6 | High-side driver current = 50mA                                           | -                                | 6*    | 11*   | Ω    |

|                         | DRN discharge current                         | $I_{\mathrm{DIS}}$              | 6,7 | VDD=OPEN,<br>DRN=12V,<br>Fault latch set                                  | 2.38                             | 3.40  | 4.42  | mA   |

| Parameter                   |                                         | Symbol                       | Pin | Condition                                                   | Value |       | Unit |       |

|-----------------------------|-----------------------------------------|------------------------------|-----|-------------------------------------------------------------|-------|-------|------|-------|

| - arameter                  |                                         | Syllibol                     | No. | Condition                                                   | Min   | Тур   | Max  | Offic |

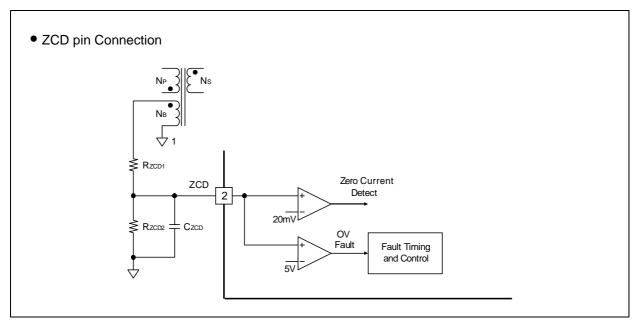

|                             | Zero current threshold voltage          | V <sub>ZCD (TH)</sub>        | 2   | -                                                           | 5*    | 20*   | 50*  | mV    |

|                             | Clamp voltage                           | V <sub>ZCD (CLAMP)</sub>     | 2   | I <sub>ZCD</sub> =-10μA                                     | -200  | -160  | -100 | mV    |

| TRANSFORMER<br>ZERO CURRENT | Start timer operation threshold voltage | V <sub>ZCD (START)</sub>     | 2   | -                                                           | 0.10  | 0.15  | 0.20 | V     |

| DETECTION                   | Driver turn-on Delay time               | t <sub>DLY (ZCD)</sub>       | 6   | 150Ω pull-up 12V on DRN                                     | 1     | 150   | -    | ns    |

|                             | Wait time for zero current detection    | t <sub>WAIT (ZCD)</sub>      | 6   | -                                                           | 2.0   | 2.4   | 2.8  | μs    |

|                             | Start timer period                      | t <sub>ST</sub>              | 6   | V <sub>ZCD</sub> =0V                                        | 150   | 240   | 300  | μs    |

| OVERVOLTAGE                 | OVP threshold voltage                   | V <sub>ZCD (OVP)</sub>       | 2   | -                                                           | 4.85  | 5.00  | 5.15 | V     |

| FAULT                       | OVP blanking time                       | t <sub>BLANK, OVP</sub>      | 6   | -                                                           | 0.6   | 1.0   | 1.7  | μs    |

| TAULI                       | Input bias current                      | I <sub>ZCD (bias)</sub>      | 2   | V <sub>ZCD</sub> =5V                                        | -0.1  | 0     | +0.1 | μΑ    |

| SHUTDOWN                    | Shutdown Threshold voltage              | V <sub>OTC (Vth)</sub>       | 4   | OTC=                                                        | 0.7   | 1.0   | 1.3  | V     |

| THRESHOLD                   | Shutdown OTC current                    | I <sub>OTC, PU</sub>         | 4   | V <sub>OTC</sub> = V <sub>OTC (vth)</sub>                   | -600  | -450  | -300 | μΑ    |

| MAXIMUM ON                  | ON-Time                                 | t <sub>OTC</sub>             | 6   | R <sub>OTC</sub> =76kΩ                                      | 3.4   | 3.8   | 4.2  | μs    |

| TIME                        | OTC voltage                             | V <sub>OTC</sub>             | 4   | -                                                           | 2.7   | 3.0   | 3.3  | V     |

|                             | Shutdown temperature                    | $T_{SD}$                     | -   | Tj, temperature rising                                      | -     | +150* | -    | °C    |

| ОТР                         | Hysteresis                              | $T_{\mathrm{SD\_HYS}}$       | -   | Tj, temperature<br>falling,degrees below<br>T <sub>SD</sub> | -     | +25*  | 1    | °C    |

|                             | Dorron aumaly aum                       | I <sub>VDD (STATIC)</sub>    | 8   | $V_{VDD}$ =20V, $V_{ZCD}$ =1V                               | 1.36  | 1.80  | 2.34 | mA    |

| POWER SUPPLY                | Power supply current                    | I <sub>VDD (OPERATING)</sub> | 8   | V <sub>VDD</sub> =20V                                       | -     | 3.0*  | 3.7* | mA    |

| CURRENT                     | Power supply current for UVLO           | I <sub>VDD (UVLO)</sub>      | 8   | $V_{VDD} = VDD_{(ON)} - 100 \text{mV}$                      | 1     | 285   | 500  | uA    |

<sup>\*:</sup> Standard design value

#### **■FUNCTION EXPLANATION**

### (1) LED Current Control Function

MB39C602 is a flyback type switching regulator controller. The LED current is regulated by controlling the switching on-time depending on the LED load. The LED current is converted into detecting voltage (Vs) by sense resistor (Rs) connected in series with LED. Vs is compared by an external error amplifier (Err AMP). When Vs falls below a reference voltage, Err AMP output rises and the current that flows into the Opto-Coupler is decreased.

The OTC pin current is controlled via the Opto-Coupler in the on-time control block. In on-time control, it controls on-time at OTC pin current. So, on-time increases when the current of the OTC pin decreases. And the average current supplied to LED is regulated, because on-time is regulated at the constant switching frequency.

### (2) Cascode Switching

The switch in Primary Winding is a cascode connection. The gate of external MOSFET is connected with the VCG pin, and the source is connected with the drain of internal Driver MOSFET. When the swich is on-state, internal Driver MOSFET is turned on, HS Driver MOSFET is turned off, and the source voltage of external MOSFET goes down to GND. For this period the DC bias is supplied to the gate of external MOSFET from the VCG pin. Therefore external MOSFET is turned on.

When the switch is off-state, internal Driver MOSFET is turned off, HS Driver MOSFET is turned on, and the source voltage of external MOSFET goes up to VCG voltage. For this period the DC bias is supplied to the gate of external MOSFET from the VCG pin. Therefore external MOSFET is turned off. Moreover, the current flowing into internal Driver MOSFET is equal to the current of Primary Winding. Therefore, the peak current into Primary Winding can be detected without the sense resistor.

### (3) Natural PFC (Power Factor Correction) Function

In the AC voltage input, when the input current waveform is brought close to the sine-wave, and the phase difference is brought close to Zero, Power Factor is improved. In the flyback method operating in discontinuous conduction mode, when the input capacitance is set small, the input current almost becomes equal with peak current ( $I_{PEAK}$ ) of Primary Winding.

$$I_{PEAK} = \left(\frac{V_{BULK} \times t_{ON}}{L_{MP}}\right) = \left(\frac{V_{BULK}}{\left(\frac{L_{MP}}{t_{ON}}\right)}\right) \\ \quad V_{BULK} : Supply \ voltage \ of \ Primary \ Winding \\ L_{MP} : Inductance \ of \ Primary \ Winding \\ t_{ON} : On-time$$

In on-time control, if loop response of Error Amp. is set to lower than the AC frequency (below 1/10 of the AC frequency), on-time can be constant. Therefore, input current is proportional to input voltage, so Power Factor is regulated.

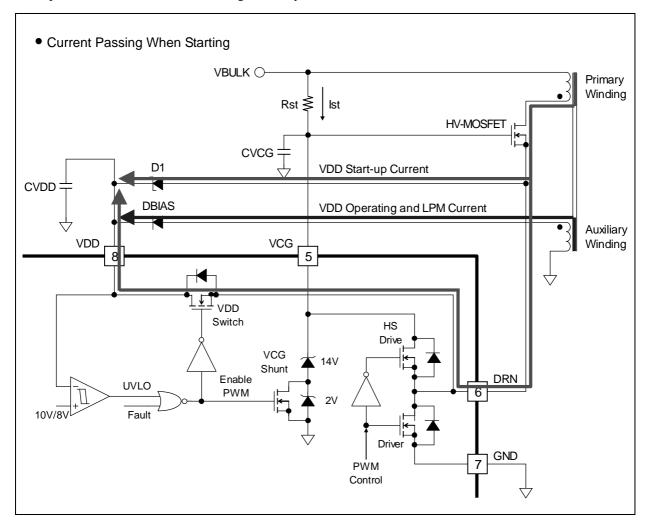

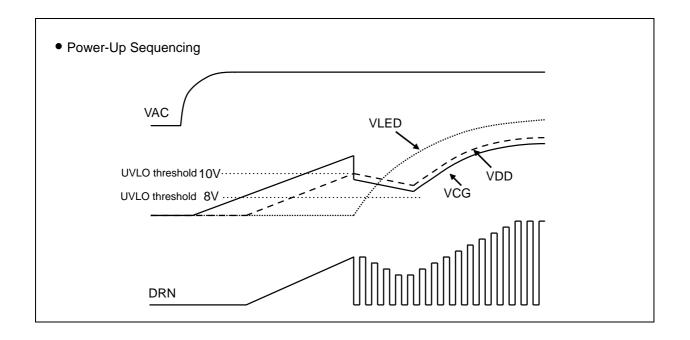

### (4) Power-Up Sequencing

When the voltage is input to VBULK, the electric charge is charged to capacitance of the VCG pin (CVCG) through starting resistor (Rst). So, the voltage of the VCG pin rises. The voltage of the DRN pin rises by source follower when the voltage of the VCG pin reaches the threshold voltage of the external HVMOSFET.

The DRN pin is connected with the VDD pin through the internal VDD Switch, and VDD capacitor (CVDD) is charged from the DRN pin. When the voltage at the VDD pin reaches the threshold voltage of UVLO, the VDD Switch is turned off, and the internal Bias circuit operates, and the switching is started.

After the switching begins, the voltage at the VDD pin is supplied from Auxiliary Winding through the external diode (DBIAS). The voltage of an Auxiliary Winding is decided by rolling number ratio of Auxiliary Winding and Secondary Winding, and the voltage of Secondary Winding. Therefore, the voltage at the VDD pin is not supplied, until the voltage of Auxiliary Winding rises more than the voltage at the VDD pin. In this period, it is necessary to set the capacitor of the VDD pin to prevent the voltage of the VDD pin from falling below the threshold voltage of UVLO.

The external Schottky diode (D1) is required between the DRN pin and VDD pin. This diode is used to prevent the current that flows through the body diode of the VDD Switch.

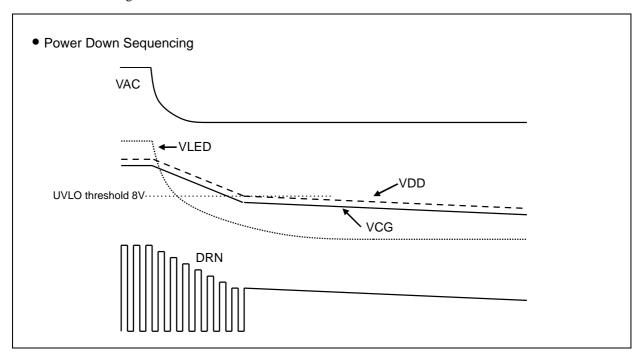

### (5) Power Down Sequencing

When AC power is removed from the AC line, the current does not flow to Secondary Winding even if HV MOSFET is switching. The LED current is supplied from the output capacitance and decreases gradually. Similarly, the voltage at the VDD pin decreases because the current does not flow into Auxiliary Winding. The switching stops and MB39C602 becomes shutdown when the voltage at the VDD pin falls below the threshold voltage of UVLO.

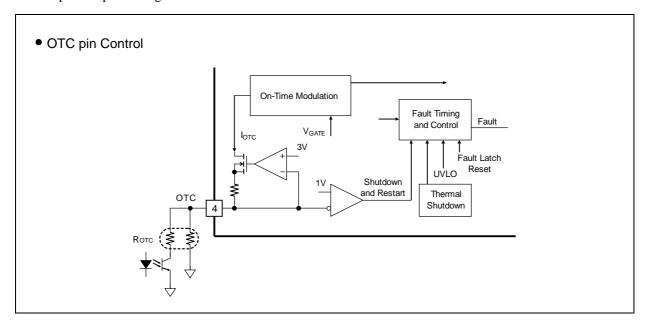

### (6) OTC Part

It is set on-time by connecting resistance (R<sub>OTC</sub>) with OTC pin.

As shown in following figure, the on-time can be controlled by connecting the collector of the Opto-Coupler through resistor from OTC.

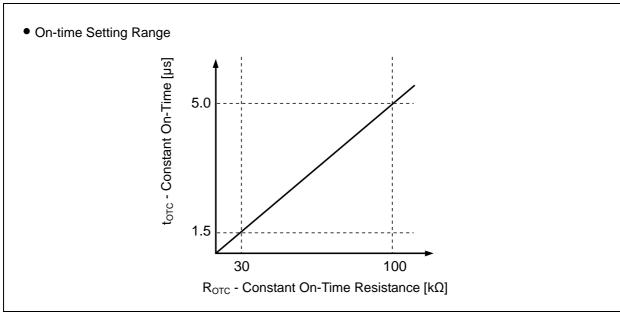

The following figure shows how the on-time is programmed over the range of between  $1.5\mu s$  and  $5.0\mu s$  for either range of programming resistors. On-time is related to the programmed resistor based on the following equations.

$$R_{OTC} = t_{OTC} \times (2 \times 10^{10} \left[ -\frac{\Omega}{S} \right])$$

Moreover, it can be shutted down by making the voltage of the OTC pin below "V<sub>OTC (Vth)</sub> (typ 1V)".

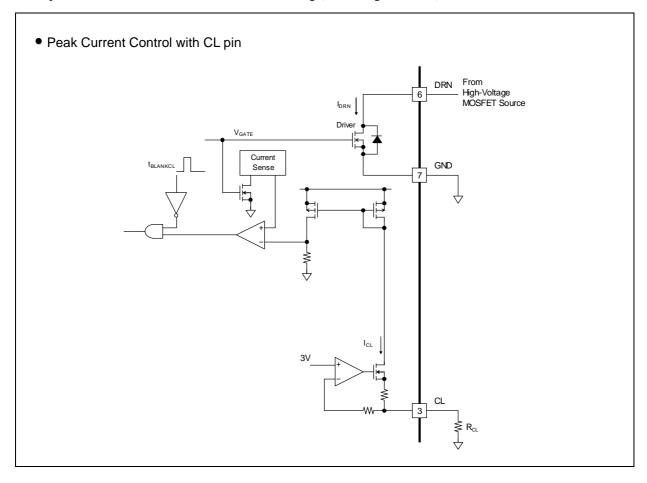

### (7) CL Part

It is set the peak current of Primary Winding by connecting resistance with CL pin.

The maximum peak current of Primary Side is set by connecting resistance ( $R_{\text{CL}}$ ) between the CL pin and GND.

$$I_{DRN(pk)} = (\frac{100kV}{R_{CL}})$$

An about 400ns blanking time of the beginning of switching cycle is masking the spike noise. As a result, it prevents the sense of current from malfunctioning (See the figure below.).

### (8) FC Part

The switching frequency is controlled by setting the current of the FC pin. In on-time control, the switching frequency is set by pulling up the FC pin to VDD.

Switching frequency range is from 30kHz to 120kHz.

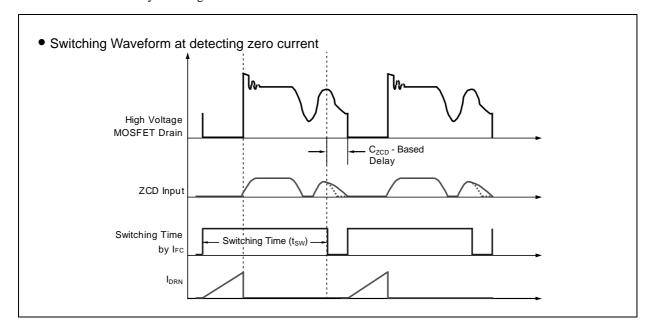

### (9) ZCD Part

MB39C602 requires the following two conditions in order to start the next switching cycle.

- 1. The time since the last turn-on edge must be equal to or longer than the switching time set by I<sub>FC</sub>.

- 2. Immediately after zero current detection at ZCD pin. Or, the time since the last zero current detection must be longer than  $t_{WAIT\,(ZCD)}$  (2.4 $\mu$ s or less).

The ZCD pin is connected with Auxiliary Winding of the transformer through the resistance division, and detects zero current as shown below.

A delay, 50ns to 200ns, can be added with  $C_{ZCD}$  to adjust the turn-on of the primary switch with the resonant bottom of Primarty Winding waveform.

#### ■ VARIOUS PROTECTION CIRCUITS

Under voltage lockout protection (UVLO)

The under voltage lockout protection (UVLO) protects IC from malfunction and protects the system from destruction/deterioration during the transient state and momentary drop due to start up for the power supply pin voltage (VDD). The voltage decrease of the VDD pin is detected with comparator, and output HS DRIVER is turned off and output DRIVER is turned off, and the switching is stopped. The system returns if the VDD pin becomes more than the threshold voltage of the UVLO circuit.

### Output over voltage Proteciton (OVP)

When LED is in the state of open and the output voltage rises too much, the voltage of Auxiliary Winding and the voltage of the ZCD pin rise. The over voltage is detected by sampling this voltage of the ZCD pin. When ZCD pin voltage rises more than the threshold voltage of OVP, the over voltage is detected. Output HS DRIVER is turned off, and output DRIVER is turned off, and the switching is stopped. (latch-off)

If the VDD pin becomes below the voltage of Fault Latch Reset, OVP is released.

#### Over temperature protection (OTP)

The over temperature protection (OTP) is a function to protect IC from the thermal destruction. When the junction temperature reaches  $+150^{\circ}$ C, output HS DRIVER is turn off, and output DRIVER is turned off, and the switching is stopped. It returns again when the junction temperature falls to  $+125^{\circ}$ C (automatic recovery).

### ■ VARIOUS FUNCTION TABLES

|                                            |        | DF     | RN     |                 | Detection                        |                                        |           |

|--------------------------------------------|--------|--------|--------|-----------------|----------------------------------|----------------------------------------|-----------|

| Function                                   | LS_DRV | HS_DRV | VDD SW | Discharge<br>SW | Condition at Protected Operation | Return<br>Condition                    | Remarks   |

| Normal Operation                           |        |        | OFF    | OFF             | -                                | -                                      | -         |

| Under Voltage Lockout<br>Protection (UVLO) | OFF    | OFF    | ON     | OFF             | VDD < 8.0V                       | VDD > 10.2V                            | Standby   |

| OTC<br>Shutdown                            | OFF    | OFF    | ON     | OFF             | OTC = GND                        | OTC > 1V                               | Standby   |

| Output Over Voltage<br>Protection (OVP)    | OFF    | OFF    | ON     | ON              | ZCD > 5V                         | $VDD < 6V$ $\rightarrow$ $VDD > 10.2V$ | Latch-off |

| Over Temperature<br>Protection (OTP)       | OFF    | OFF    | ON     | OFF             | Tj > +150°C                      | Tj < +125°C                            | -         |

### ■I/O PIN EQUIVALENT CIRCUIT SCHEMATIC

|            |             | VALENT CIRCUIT SCHEMATIC     |  |  |  |

|------------|-------------|------------------------------|--|--|--|

| Pin<br>No. | Pin<br>Name | Equivalent Circuit Schematic |  |  |  |

| 1          | FC          | FC 1 GND 7                   |  |  |  |

| 2          | ZCD         | ZCD 2 W+ GND 7               |  |  |  |

| 3          | CL          | CL 3 CL 3 GND 7              |  |  |  |

| 4          | OTC         | OTC 4  GND 7                 |  |  |  |

#### **■USAGE PRECAUTION**

### 1. Do not configure the IC over the maximum ratings.

If the IC is used over the maximum ratings, the LSI may be permanently damaged. It is preferable for the device to normally operate within the recommended usage conditions. Usage outside of these conditions can have an adverse effect on the reliability of the LSI.

### 2. Use the device within the recommended operating conditions.

The recommended values guarantee the normal LSI operation under the recommended operating conditions. The electrical ratings are guaranteed when the device is used within the recommended operating conditions and under the conditions stated for each item.

## 3. Printed circuit board ground lines should be set up with consideration for common impedance.

### 4. Take appropriate measures against static electricity.

- Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- Work platforms, tools, and instruments should be properly grounded.

- Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial between body and ground.

### 5. Do not apply negative voltages.

The use of negative voltages below - 0.3 V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

## ■ ORDERING INFORMATION

| Part number | Package                           | Remarks |

|-------------|-----------------------------------|---------|

| MB39C602PNF | 8-pin plastic SOP<br>(FPT-8P-M02) |         |

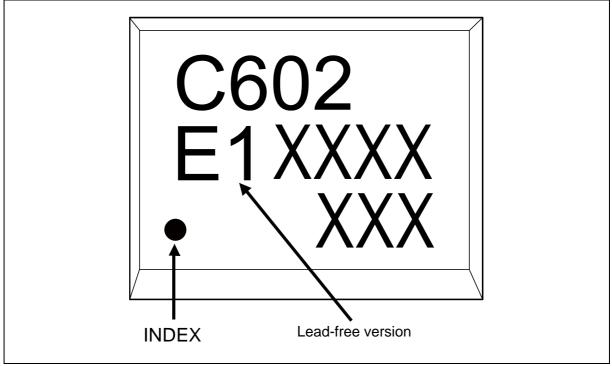

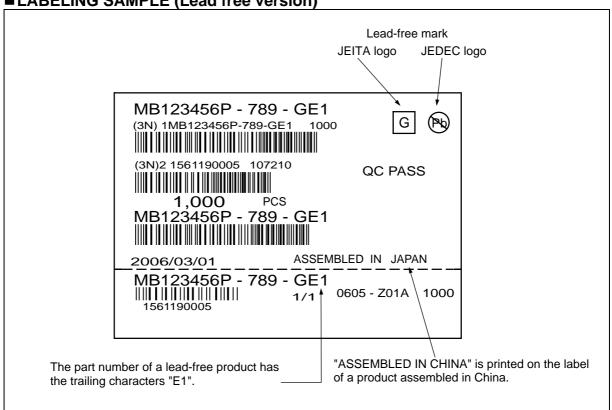

### ■ Rohs Compliance Information of Lead (Pb) Free Version

The LSI products of FUJITSU SEMICONDUCTOR with "E1" are compliant with RoHS Directive, and has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE). A product whose part number has trailing characters "E1" is RoHS compliant.

### ■MB39C602PNF RECOMMENDED CONDITIONS OF MOISTURE SENSITIVITY **LEVEL**

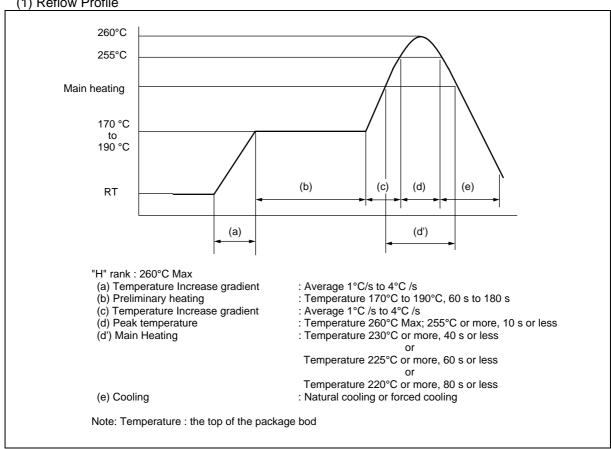

### [FUJITSU SEMICONDUCTOR Recommended Mounting Conditions] Recommended Reflow Condition

| Recommended Renow O | econinenced Kenow Condition                                |                                                                                                               |  |  |  |

|---------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Item                | Condition                                                  |                                                                                                               |  |  |  |

| Mounting Method     | IR (infrared reflow), warm air reflow                      |                                                                                                               |  |  |  |

| Mounting times      | 2 times                                                    |                                                                                                               |  |  |  |

|                     | Before opening                                             | Please use it within two years after manufacture.                                                             |  |  |  |

| Storage period      | From opening to the 2nd reflow                             | Less than 8 days                                                                                              |  |  |  |

| <b>.</b>            | When the storage period after opening was exceeded         | Please process within 8 days after baking (125°C ±3°C, 24H+ 2H/–0H). Baking can be performed up to two times. |  |  |  |

| Storage conditions  | 5°C to 30°C, 70% RH or less (the lowest possible humidity) |                                                                                                               |  |  |  |

### [Mounting Conditions]

### (1) Reflow Profile

(2) JEDEC Condition: Moisture Sensitivity Level 3 (IPC/JEDEC J-STD-020D)

(3) Recommended manual soldering (partial heating method)

| Item                | Condition                                                                                     |                                                                                                                                   |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                     | Before opening                                                                                | Within two years after manufacture                                                                                                |  |  |  |

| Storage period      | Between opening and mounting                                                                  | Within two years after manufacture (No need to control moisture during the storage period because of the partial heating method.) |  |  |  |

| Storage conditions  | 5°C to 30°C, 70% RH or less (the lowest possible humidity)                                    |                                                                                                                                   |  |  |  |

| Mounting conditions | Temperature at the tip of a soldering iron: 400°C Max<br>Time: Five seconds or below per pin* |                                                                                                                                   |  |  |  |

<sup>\*:</sup> Make sure that the tip of a soldering iron does not come in contact with the package body.

(4) Recommended dip soldering

| Item               | Condition                                                           |                                                                                                                 |  |  |  |

|--------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Mounting times     | 1 time                                                              |                                                                                                                 |  |  |  |

|                    | Before opening                                                      | Please use it within two years after manufacture.                                                               |  |  |  |

| Storage period     | From opening and mounting                                           | Less than 14 days                                                                                               |  |  |  |

|                    | When the storage period after opening was exceeded                  | Please process within 14 days after baking (125°C ±3°C, 24H+ 2H/—0H).  Baking can be performed up to two times. |  |  |  |

| Storage conditions | 5°C to 30°C, 70% RH or less (the lowest possible humidity)          |                                                                                                                 |  |  |  |

| Mounting condition | Temperature at soldering tub: 260°C Max Time: Five seconds or below |                                                                                                                 |  |  |  |

### ■ PACKAGE DIMENSIONS

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

## **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan Tel: +81-45-415-5858

http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://us.fujitsu.com/micro/

#### **Europe**

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 902 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fsk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://sg.fujitsu.com/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. 30F, Kerry Parkside, 1155 Fang Dian Road, Pudong District, Shanghai 201204, China Tel: +86-21-6146-3688 Fax: +86-21-6146-3660 http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 2/F, Green 18 Building, Hong Kong Science Park, Shatin, N.T., Hong Kong

Tel: +852-2736-3232 Fax: +852-2314-4207

http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information. Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws. The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department