基于FPGA加速器的WAN加速技术

本技术介绍参考了以下链接

English

2018年11月22日

基于FPGA加速器的WAN加速技术

在10 Gbps线路上实现了业界最快的有效数据传输速度,高达40 Gbps

株式会社富士通研究所(注1)(以下简称:富士通研究所)开发出了一种WAN加速技术,基于FPGA(注2)服务器,实现了云间海量数据的高速传输,传输速度高达每秒40千兆位(以下简称:Gbps)。

开发背景

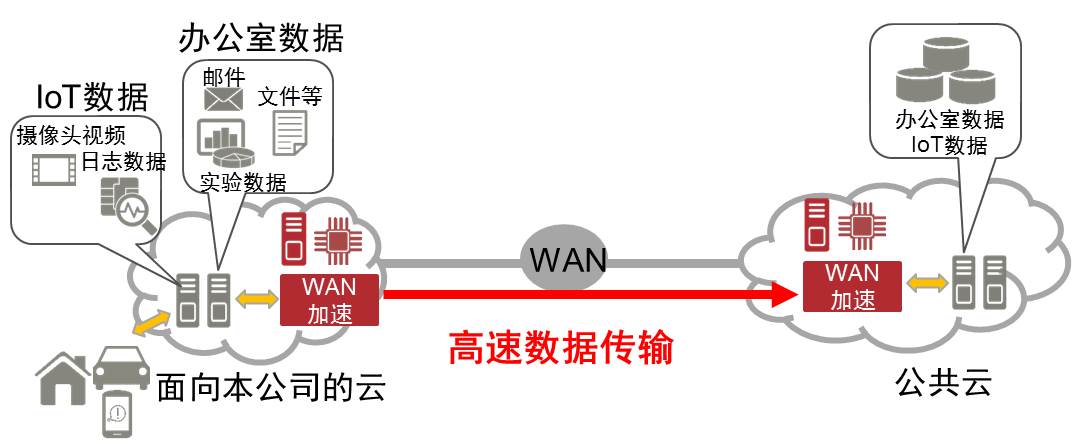

近年来,随着云的发展,出现了通过将企业内部服务器管理的数据(内部文件、设计数据、电子邮件等)迁移到云上,来提高数据和服务器管理维护效率的行为。另外,IoT、AI等数字技术也得到广泛应用,人们期望通过对工厂或现场摄像头拍摄的视频、设备日志数据等大量数据进行分析利用,实现业务或商业创新。随之而来的是,流经云间WAN线路的数据量呈爆炸式增长,它激发了对下一代WAN加速技术的需求,该技术能够在云间高速传输大量数据。

图1 WAN加速技术在云环境中的应用

课题

在WAN加速技术中,为了提高实际传输速度,需要通过压缩传输数据或去除重复数据来减少数据量。在10Gbps网络线路上进行更快速的数据传输时,需要处理的数据量增大,会导致服务器中压缩或去除重复数据的处理速度变慢。因此,需要能够更加高速运行的CPU或具有更高处理速度的WAN加速技术来实现实时操作。

开发的技术

此次,富士通研究所开发了一种WAN加速技术,它将安装在服务器上的FPGA作为加速器,可应用在云上且实现超过10 Gbps的实时操作。在本技术的WAN加速处理过程中,对于压缩或去除重复数据时,负载过重、且难以提高CPU处理速度的部分,通过使用FPGA执行处理,以及CPU和FPGA加速器的高效连接,实现了WAN加速技术的高效运行。

开发的技术特征如下:

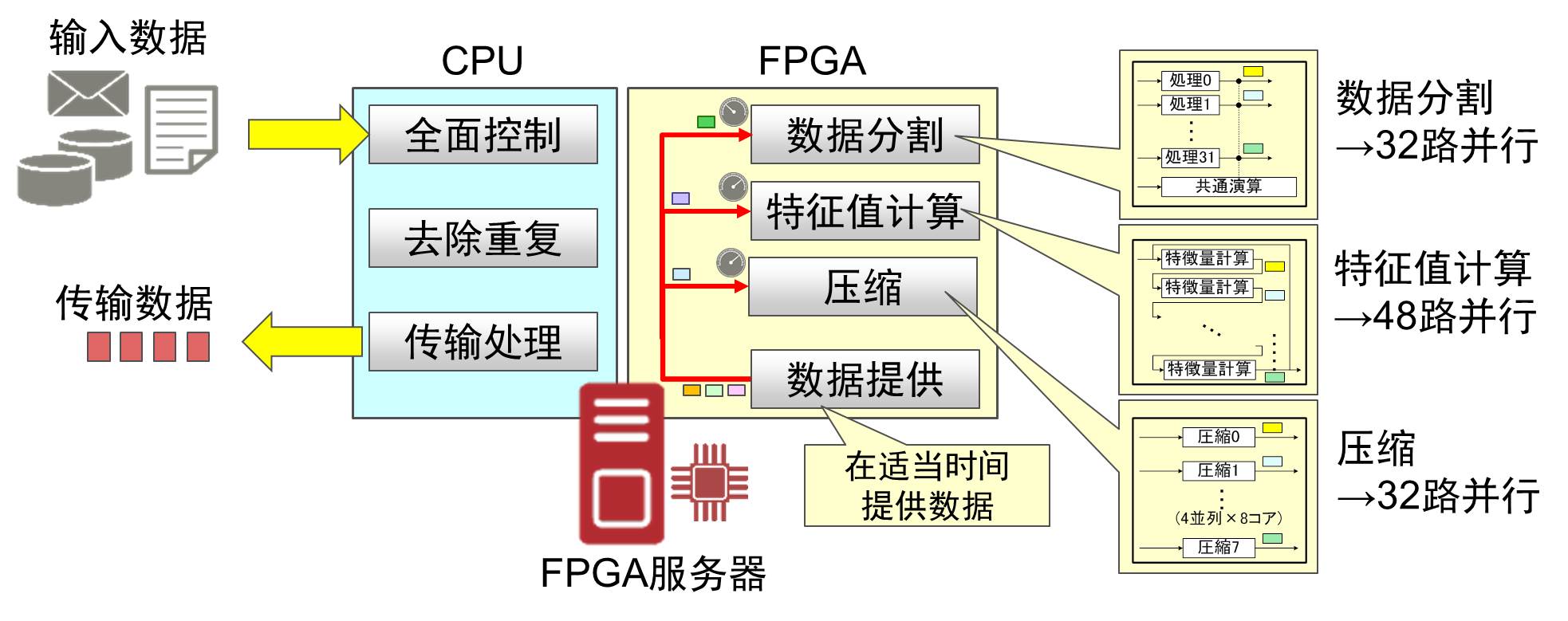

- 基于高并行专用运算器的FPGA并行化技术

此次富士通研究所开发了一种FPGA并行化技术,在FPGA中高并行安装专门用于数据分割、特征值计算、无损压缩处理的运算器,同时基于每个运算的完成预测,在适当时间提供数据,实现了运算器的高并行操作,从而大幅度削减了数据压缩/去除重复所需的处理时间。

图2 基于FPGA服务器实施WAN加速处理

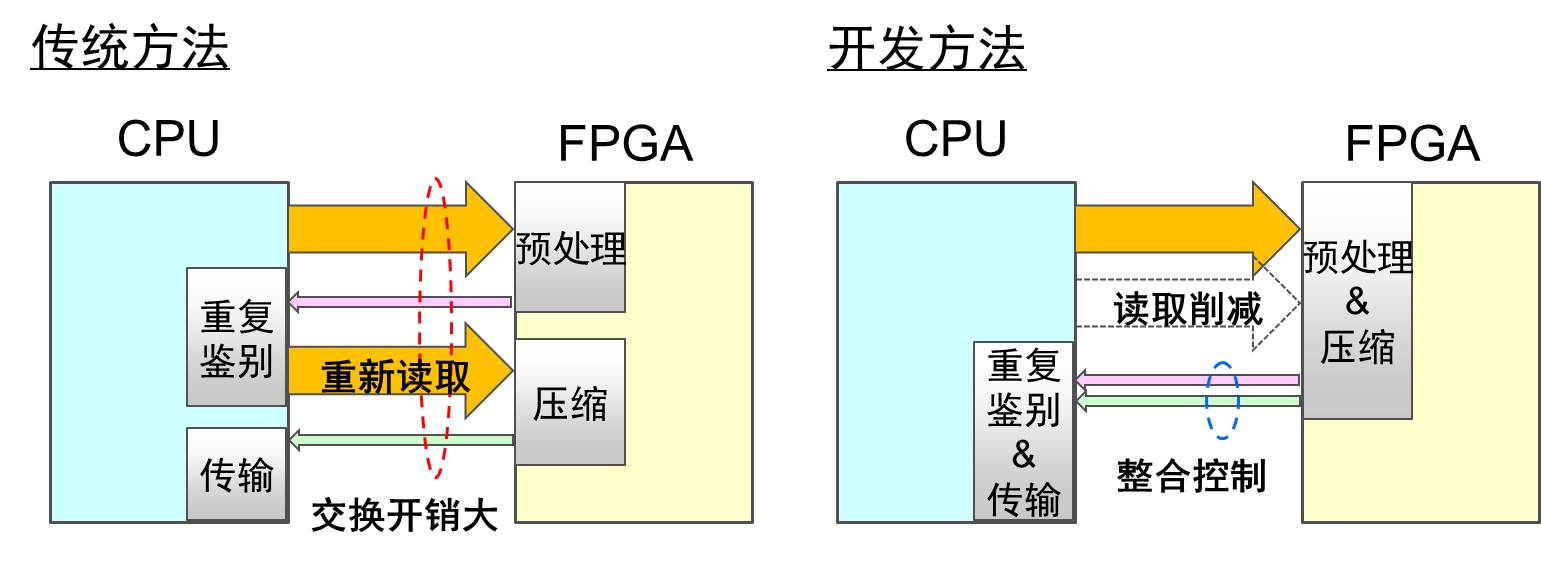

- CPU和FPGA间的处理流程优化技术

以往,基于重复数据的鉴别结果确定是否进行无损压缩处理时,需要在FPGA端执行重复鉴别处理的前后读取两次数据,导致开销变大,系统性能降低。此次,富士通研究所通过将处理切换固定到FPGA上,在FPGA端进行重复数据鉴别的预处理及压缩处理,并在CPU端根据重复数据的鉴别结果,控制压缩处理结果在CPU中的反映方式,减少了CPU和FPGA间重新加载输入数据和控制交换所产生的开销。该技术减少了CPU和FPGA间基于数据传输和控制交换等产生的等待时间,实现了CPU和FPGA加速器间的高效连接。

图3 降低CPU和FPGA间开销的技术概要

效果

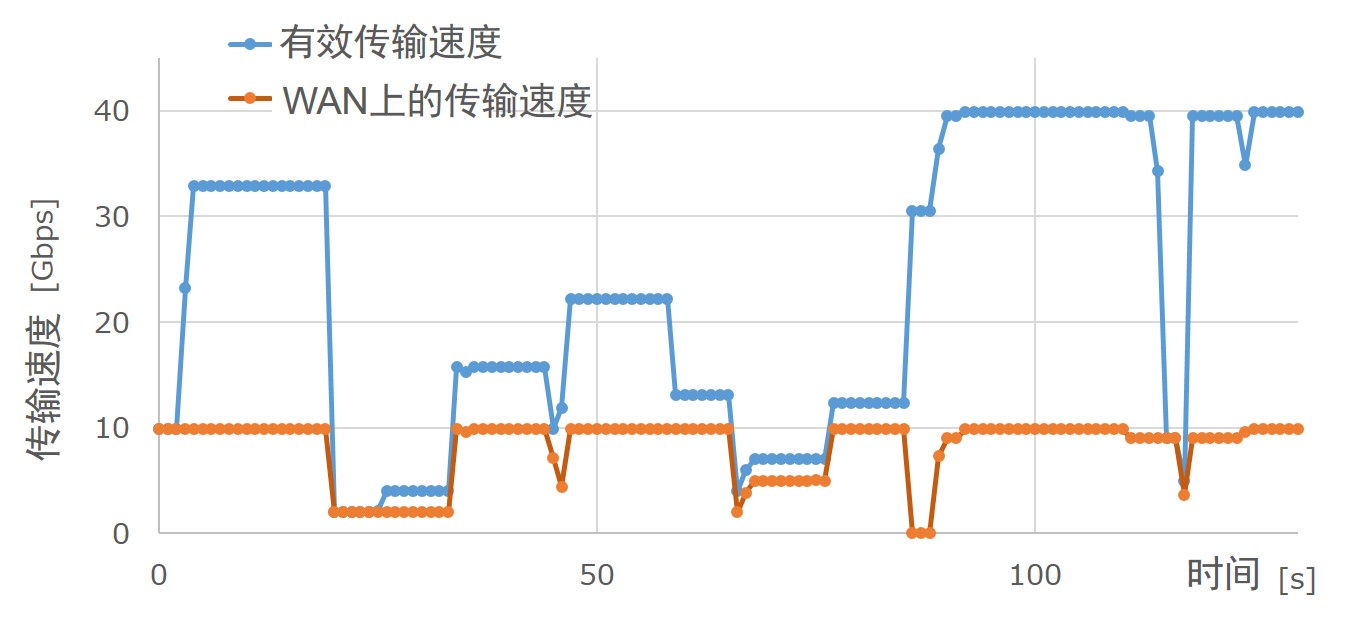

富士通研究所将此次开发的技术应用于FPGA服务器,结果显示处理速度是仅使用CPU的30倍。我们用10 Gbps线路将各服务器连接,在该实验环境中对海量数据的传输速度进行了评估。在模拟数据定期备份(文档或图像数据等)的实验中,我们确认实现了高达40 Gbps的传输速度,为业界最高。该技术将会大幅提高WAN线路上数据的传输效率,加快云中数据共享和备份等数据传输的速度,同时可实现各公司/办事处间海量数据共享与活用的下一代云服务。

图4 基于实验数据的评估结果样本

今后

富士通研究所将在可用于云环境的虚拟设备上安装该技术,并在真实环境中进行评估,目标实现其产品化。