本技术介绍参考了以下链接

English

2017年12月16日

可提高深度学习(Deep Learning)中硬件能效的电路技术

株式会社富士通研究所(注1)(以下简称,富士通研究所)开发了一种电路技术,通过减少深度学习中用于学习处理的数据位宽,可以在不改变神经网络架构和学习方法的情况下提高深度学习中硬件的能效。

开发背景

近年来,随着IoT的普及,连接到网络的设备数量迅速增加。预测到2020年,将会有数百亿台设备连接至网络,届时将会产生庞大的数据量。通常情况下,这些数据本身并没有意义,但我们可以通过深度学习等机器学习从中提取价值,创造出新的知识见解。

由于IoT学习数据的增加以及深度学习神经网络规模的扩大,对服务器(用于深度学习)的性能要求也越来越高。另外,为了减少传输数据的通信量和记录数据的存储量,不仅需要在云端,还需要在靠近数据源的边缘侧进行学习。

由于用于深度学习的服务器,无论在边缘还是云端,都有功率的限制,因此预计未来要想提高性能,很难通过单纯扩大规模来实现,这就需要一种技术来提高能效。

课题

通常,用于深度学习的硬件以32位浮点的数据格式执行运算处理。通过将运算中使用数据的位宽减少到16位或更少,或使用基于整数执行运算的硬件,可减少运算量,提高能效。但与此同时,这可能导致运算缺乏所需精度,无法进行深度学习,削弱神经网络的识别能力等。

开发的技术

此次,富士通研究所开发了一种基于整数运算的电路技术,通过减少深度学习过程中运算单元的位宽和用于记录学习结果内存的位宽,提高能效。在深度学习过程中,利用独特的数值表示来减少位宽,分析多层神经网络各层数据分布情况的同时,通过运算算法自动控制小数点的位置以保持运算精度。

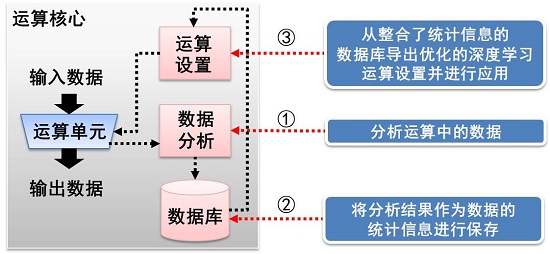

基于本技术的深度学习硬件的运算核心包括: (1)用于分析运算中数据的单元块(block) (2)存储经过分析的数据分布的数据库 (3)保持运算设置的单元块(图1)。在数据分析单元块中,对深度学习过程中运算单元的输出数据进行实时分析,将分析结果作为表示数据分布的统计信息保存在数据库中。该分布用于优化运算单元的设置,以保持足够的运算精度,提高深度学习的训练精度(图2)。

图1 通过运算核心提高运算精度

图2 利用统计信息优化运算设置

效果

新开发的电路技术可以从两个方面提高能效。第一,针对用浮点进行的运算,通过用整数运算代替,可降低功耗(注2)。第二,通过将数据位宽从32位减少到8位,运算单元和内存的功耗降低了约75%。设想在深度学习硬件中安装该技术并进行模拟实验,使用LeNet(注3)和MNIST(注4)数据集进行学习,结果证明,与32位浮点运算的学习结果(识别率为98.90%)相比,16位的识别率为98.89%,8位的为98.31%。这样,深度学习处理虽需要大量学习数据,但通过提高深度学习中硬件的能效,无论在云服务器还是靠近数据源的边缘服务器,都可实现深度学习处理。

今后

富士通研究所计划将开发的新技术作为富士通株式会社AI技术“Human Centric AI Zinrai”之一,目标于2018年度实现其商业化。同时,我们还将与客户共同为促进AI技术的应用而努力。此外,为了进一步减少用于深度学习的数据量,我们还将继续开发新的电路技术。

注释

- 注1 株式会社富士通研究所:

- 社长 佐佐木 繁

总公司所在地 日本神奈川县川崎市 - 注2针对用浮点进行的运算,通过用整数运算代替,可降低功耗:

- 例如:32位整数数据的乘法器和加法器的总功率约为3.2微微焦耳(pJ),而32位浮点数据约为4.6 pJ,这种情况下,运算单元的功率可降低约30%。 出处:M. Horowitz, "1.1 Computing's energy problem(and what we can do about it)," 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers(ISSCC), San Francisco, CA, 2014, pp. 10-14.

- 注3 LeNet:

- 手写数字识别中经常使用的卷积神经网络。

- 注4 MNIST:

- 用于手写数字识别的28×28像素学习数据集。