# 3.125Gbps x4 Parallel Transceiver

Macro for XAUI (0.11µm)

### Features

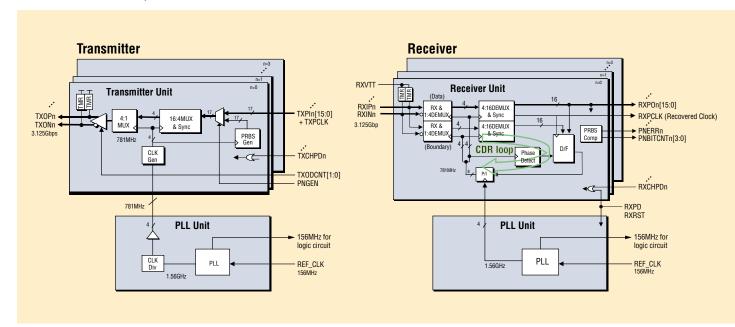

- 3.125Gbps x 4 channel unidirectional data transfer rate for 10G Ethernet physical layer

- IEE802.3ae physical layer compliant

- 156MHz input reference clock and parallel interface

- 4-channel CDR Rx and 4-channel Tx arrays

- Differential PCML (Vterm=1.2V and 1.8V)

- AC coupled differential interface

- 1:16 SERDES with 16:20 gearbox, 8B/10B coding and lane lane alignment provided as RTL/netlist

- On chip integrated 50-ohm termination resistors

- Independent dual loop PLL based CDR on each Rx channel

- Built-in PRBS (2^23-1) generators and comparators for loopback testing

- 1.2V and 2.5V power supply, 0.11µm standard CMOS process

#### Benefits

- Available as library cell for ASIC designs

- Programmable Tx voltage swing and amount of pre-emphasis

- Pre-emphasis based Tx equalization allows up to 12dB high frequency loss

- Meet XAUI jitter specifications (IEEE 802.3)

## 3.125Gbps x4 Parallel Transceiver

### Description

The Fujitsu's XAUI macro is for ASICs that perform at high bandwidth data communication.

The macro meets XAUI jitter specifications as follows:

- jitter generation < 0.35UI (without pre-emphasis)

- jitter tolerance > 0.60UI (peak to peak total jitter)

- meets sinusoidal jitter tolerance mask requirement

The macro has 100mW/ch power dissipation(including Rx, Tx, CDR, bias circuit and PLL, maximum preemphasis) and runs under power supply of  $1.2V\pm0.10V$ ,  $2.5V\pm0.20V$  and junction temperature of  $0^{\circ}C\sim125^{\circ}C$ .

The macro is fabricated in Fujitsu's standard 0.11µm CMOS technology.

The macro can be used in a variety of applications:

- 10G Ethernet

- WAN router or switch backplanes and line card to switch fabric interface

- Any backplane line for 3.125Gbps x4 data rate

## Deliverables

The Fujitsu value-added XAUI Transceiver Macro enables customers to design a variety of complex ASIC designs for high-end networking applications.

A Fujitsu application engineer works with the customer to identify the customer's specific IP requirements. Fujitsu will provide the customer with the following information to support the 3.125Gbps x4 XAUI Transceiver macro:

- Verilog Model

- Front-end simulation

- C model with Verilog wrapper

- Design Compiler Model

- Timing analysis

- Library Exchange Format (LEF)

- Floorplanning

- Place and Route