# Semicustom

**CMOS**

# Standard cell

# **CS81 Series**

#### ■ DESCRIPTION

The CS81 series 0.18  $\mu m$  CMOS standard cell is a line of highly integrated CMOS ASICs featuring high speed and low power consumption.

This series incorporates up to 40 million gates which have a gate delay time of 11 ps, resulting in both integration and speed about three times higher than conventional products.

In addition, CS81 can operate at a power-supply voltage of down to 1.1 V, substantially reducing power consumption.

#### **■ FEATURES**

- Technology : 0.18 μm silicon-gate CMOS, 4 to 6 layer wiring capable of integrating a mixture of highspeed processes and cells on a single chip (under development)

- Supply voltage :  $\pm 1.8 \text{ V} \pm 0.15 \text{ V}$  (normal) to  $\pm 1.1 \text{ V} \pm 0.1 \text{ V}$

- Junction temperature range : -40 to +125 °C

- Gate delay time :  $t_{pd} = 11 ps (1.8 V, inverter, F/O = 1)$

- Gate power consumption : Pd = 5 nW/MHz/BC (1.1 V, 2-NAND, F/O = 1)

- Support for high speed (62.2 Mbps to 780 Mbps, 2.5 Gbps to 3.125 Gbps) interface macros for transmission

- · Output buffer cells with noise reduction circuits

- Inputs with on-chip input pull-up/pull-down resistors (33 kΩ typical) and bidirectional buffer cells

- Buffer cells dedicated to crystal oscillators

- Special interfaces (P-CML, LVDS, PCI, AGP, USB, SDRAM-I/F, SSTL, and others. including those under development)

- IP macros (CPU (FR, ARM7, ARM9), DSP, PCI, IEEE1394, USB, IrDA, PLL, ADC, DAC, and others. including those under development)

- Capable of incorporating compiled cells (RAM/ROM/multiplier, and others.)

- · Configurable internal bus circuits

- · Advanced hardware/software co-design environment

- Short-term development using a timing driven layout tool

- · Support for static timing sign-off

Dramatically reducing the time for generating test vectors for timing verification and the simulation time

(Continued)

#### (Continued)

- Hierarchical design environment for supporting large-scale circuits

- Simulation (before layout) considering the input slew rate and detailed RC delay calculation (after layout), supporting development with minimized timing trouble after trial manufacture

- Support for memory (RAM/ROM) SCAN

- Support for memory (RAM) BIST

- Support for boundary SCAN

- Support for path delay test

- Package lineup: HQFP, FBGA, FCBGA, LQFP

#### **■ MACRO LIBRARY**

## 1. Logic cells (about 400 types)

Adder

Decoder

AND-OR Inverter

• Non-SCAN Flip Flop

Clock BufferLatch

InverterBuffer

• NAND

OR-AND

• AND

OR-AND Inverter

• NOR

• OR

• SCAN Flip Flop

Selector

• ENOR

• BUS Driver

• AND-OR

• EOR

Others

## 2. IP macros

| CPU/DSP                      | FR, SPARClite, ARM7, ARM9, Communications DSP, DSP for AV and others |

|------------------------------|----------------------------------------------------------------------|

| High speed interface macros  | 622 Mbps to 780 Mbps, 2.5 Gbps to 3.125 Gbps                         |

| Interface macro              | PCI, IEEE1394, USB, IrDA, and others                                 |

| Multimedia processing macros | JPEG, MPEG, and others                                               |

| Mixed signal macros          | ADC, DAC, OPAMP, and others                                          |

| Compiled macros              | RAM, ROM, multiplier, adder, multiplier-accumulator, and others      |

| PLL                          | Analog PLL, digital PLL                                              |

#### 3. Special I/O interface macros

• T-LVTTL • LVDS • SSTL • PCI HSTLAGP

• P-CML

• IEEE1394

• SDRAM-I/F

• USB

#### **■ COMPILED CELLS**

Compiled cells are macro cells which are automatically generated with the bit/word configuration specified. The CS81 series has the following types of compiled cells. (Note that each macro is different in word/bit range depending on the column type.)

## 1. Clock synchronous single-port RAM (1 address : 1 RW)

• High density type/Partial write type

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 4           | 16 to 72 K      | 16 to 1 K  | 1 to 72   | bit  |

| 16          | 64 to 72 K      | 64 to 4 K  | 1 to 18   | bit  |

· High speed type

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 8           | 256 to 144 K    | 64 to 2 K  | 4 to 72   | bit  |

· Large scale partial write type

| Column type | Memory capacity  | Word range  | Bit range | Unit |

|-------------|------------------|-------------|-----------|------|

| 16          | 24.5 K to 1179 K | 4 K to 16 K | 6 to 72   | bit  |

### 2. Clock synchronous dual-port RAM (2 addresses : 1 RW, 1 R)

• High density type/Partial write type

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 4           | 16 to 72 K      | 16 to 1 K  | 1 to 72   | bit  |

| 16          | 64 to 72 K      | 64 to 4 K  | 1 to 18   | bit  |

## 3. Clock synchronous register file (3 addresses : 1 W, 2 R)

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 1           | 4608            | 4 to 64    | 1 to 72   | bit  |

4. Clock synchronous register file (4 addresses : 2 W, 2 R)

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 1           | 4608            | 4 to 64    | 1 to 72   | bit  |

#### 5. Clock synchronous ROM (1 addresses, 1 R)

| Column type | Memory capacity | Word range | Bit range | Unit |

|-------------|-----------------|------------|-----------|------|

| 16          | 256 to 512 K    | 128 to 4 K | 2 to 128  | bit  |

#### 6. Clock synchronous delay line memory (2 addresses : 1 W, 1 R)

|             |                 |            | · · · · · · · · · · · · · · · · · · · |      |

|-------------|-----------------|------------|---------------------------------------|------|

| Column type | Memory capacity | Word range | Bit range                             | Unit |

| 8           | 256 to 32 K     | 32 to 1 K  | 8 to 32                               | bit  |

| 16          | 384 to 32 K     | 64 to 2 K  | 6 to 16                               | bit  |

| 32          | 512 to 32 K     | 128 to 4 K | 4 to 8                                | bit  |

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                       | Cumbal          | R           | ating                                     | Unit   |  |

|---------------------------------|-----------------|-------------|-------------------------------------------|--------|--|

| Parameter                       | Symbol          | Min         | Max                                       | Unit   |  |

| Supply voltage*1                | V <sub>DD</sub> | -0.5        | +2.5*2                                    | V      |  |

| Supply voltage*1                | <b>V</b> DD     | -0.5        | +4.0*3                                    | V      |  |

| Input voltogo*1                 | M               | 0.5         | V <sub>DD</sub> +0.5 ( ≤ 2.5 V) *2        | V      |  |

| Input voltage*1                 | VI –0.5         |             | $V_{DD}+0.5 ( \le 4.0 \text{ V}) *3$      | V      |  |

| Output voltogo*1                | VO              | -0.5        | $V_{DD}+0.5 (\le 2.5 \text{ V})^{*2}$     | V      |  |

| Output voltage*1                | VO              | -0.5        | $V_{DD}+0.5 ( \le 4.0 \text{ V})^{*3}$    | \ \ \  |  |

| Storage temperature             | Tst             | <b>–55</b>  | +125                                      | °C     |  |

| Junction temperature            | Tj              | -40         | +125                                      | °C     |  |

| Output current*4                | Ю               | _           | ±4                                        | mA     |  |

| Input signal transmitting rate  | RI              | _           | Clock input*5 : 200<br>Normal input : 100 | Mbps*6 |  |

| Output signal transmitting rate | RO              | <del></del> | 100                                       | Mbps*6 |  |

| Output load capacitance         | CO              |             | 3000/RO                                   | pF     |  |

| Supply pin current              | ID              | _           | *7                                        | mA     |  |

<sup>\*1 :</sup> Vss = 0 V

\*7 : Supply pin current for one VDD/GND pin

| Frame  | Source type                                          | Maximum o       | Number of         |       |

|--------|------------------------------------------------------|-----------------|-------------------|-------|

|        | Source type                                          | Standard source | Additional source | layer |

|        | VDDE, VDDI, VDD, VSS                                 | 68              | 68                | 4, 5  |

| YS, YI | VDDE                                                 | 39              | 39                | 3     |

|        | V <sub>DDI</sub> , V <sub>DD</sub> , V <sub>SS</sub> | 68              | 68                | 3     |

| В      | VDDE, VDDI, VDD, VSS                                 | 43              | 30                | _     |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>\*2 :</sup> Internal gate part in case of single power supply or dual power supply

<sup>\*3:</sup> I/O part in case 3.3 V I/F or 2.5 V I/F is used by dual power supply.

<sup>\*4 :</sup> DC current which continues more than 10 ms, or average DC current

<sup>\*5:</sup> in case of I/O cell for clock input

<sup>\*6 :</sup> bps = bit per second

## **■ RECOMMENDED OPERATING CONDITIONS**

• Single power supply ( $V_{DD} = +1.8 \text{ V} \pm 0.15 \text{ V}$ )

(Vss = 0 V)

| Parameter                             | Symbol          | Value                       |     |                             | Unit |

|---------------------------------------|-----------------|-----------------------------|-----|-----------------------------|------|

| Farameter                             | Symbol          | Min                         | Тур | Max                         | Oill |

| Supply voltage (1.8 V supply voltage) | V <sub>DD</sub> | 1.65                        | 1.8 | 1.95                        | V    |

| "H" level input voltage (1.8 V CMOS)  | ViH             | $V_{\text{DD}} \times 0.65$ | _   | V <sub>DD</sub> + 0.3       | V    |

| "L" level input voltage (1.8 V CMOS)  | VıL             | -0.3                        | _   | $V_{\text{DD}} \times 0.35$ | V    |

| Junction temperature                  | Tj              | -40                         | _   | +125                        | °C   |

• Dual power supply (VdDE = +3.3 V  $\pm$  0.3 V, VdDI = +1.8 V  $\pm$  0.15 V)

(Vss = 0 V)

| Parameter               |                      | Symbol           |                              | Unit |                              |            |

|-------------------------|----------------------|------------------|------------------------------|------|------------------------------|------------|

|                         |                      | Syllibol         | Min                          | Тур  | Max                          | Offic      |

| Supply voltage          | 1.8 V supply voltage | V <sub>DDI</sub> | 1.65                         | 1.8  | 1.95                         | V          |

| Supply voltage          | 3.3 V supply voltage | V <sub>DDE</sub> | 3.0                          | 3.3  | 3.6                          | V          |

| "L" lovel input veltage | 1.8 V CMOS           |                  | $V_{\text{DDI}} \times 0.65$ | _    | V <sub>DDI</sub> + 0.3       | V          |

| "H" level input voltage | 3.3 V CMOS           | Vıн              | 2.0                          | _    | V <sub>DDE</sub> + 0.3       | ]          |

| "L" level input voltage | 1.8 V CMOS           | VIL              | -0.3                         | _    | $V_{\text{DDI}} \times 0.35$ | V          |

| L level input voltage   | 3.3 V CMOS           | VIL              | -0.3                         | _    | +0.8                         | ] <b>'</b> |

| Junction temperature    | ·                    | Tj               | -40                          | _    | +125                         | °C         |

• Dual power supply (VDDE = +3.3 V  $\pm$  0.3 V, VDDI = +1.5 V  $\pm$  0.1 V / +1.1 V  $\pm$  0.1 V)

(Vss = 0 V)

| Parameter               |            | Symbol           |      | Unit |                        |      |

|-------------------------|------------|------------------|------|------|------------------------|------|

|                         |            | Symbol           | Min  | Тур  | Max                    | Unit |

|                         |            | V <sub>DDE</sub> | 3.0  | 3.3  | 3.6                    | V    |

| Supply voltage          |            | V <sub>DDI</sub> | 1.0  | 1.1  | 1.2                    | V    |

|                         |            |                  | 1.4  | 1.5  | 1.6                    | V    |

| "H" level input voltage | 3.3 V CMOS | VIH              | 2.0  | _    | V <sub>DDE</sub> + 0.3 | V    |

| "L" level input voltage | 3.3 V CMOS | VIL              | -0.3 | _    | +0.8                   | V    |

| Junction temperature    |            | Tj               | -40  | _    | +125                   | °C   |

#### • Dual power supply (VDDE = +2.5 V $\pm$ 0.2 V, VDDI = +1.8 V $\pm$ 0.15 V)

(Vss = 0 V)

| Parameter               |               | Symbol           |                              | Unit |                              |       |

|-------------------------|---------------|------------------|------------------------------|------|------------------------------|-------|

|                         |               | Syllibol         | Min                          | Тур  | Max                          | Oilit |

| Supply voltage          |               | V <sub>DDE</sub> | 2.3                          | 2.5  | 2.7                          | V     |

| Supply voltage          | upply voltage |                  | 1.65                         | 1.8  | 1.95                         | V     |

| ((1))                   | 1.8 V CMOS    | Vıн              | $V_{\text{DDI}} \times 0.65$ | _    | V <sub>DDI</sub> + 0.3       | V     |

| "H" level input voltage | 2.5 V CMOS    |                  | 1.7                          | _    | V <sub>DDE</sub> + 0.3       | V     |

| "L" level input voltage | 1.8 V CMOS    | VIL              | -0.3                         | _    | $V_{\text{DDI}} \times 0.35$ | V     |

| L level input voltage   | 2.5 V CMOS    | VIL              | -0.3                         | _    | +0.7                         | V     |

| Junction temperature    |               | Tj               | -40                          | _    | +125                         | °C    |

## • Dual power supply (VDDE = +2.5 V $\pm$ 0.2 V, VDDI = +1.5 V $\pm$ 0.1 V / +1.1 V $\pm$ 0.1 V)

(Vss = 0 V)

| Parameter               |            | Symbol           |      | Unit |                        |       |

|-------------------------|------------|------------------|------|------|------------------------|-------|

|                         |            | Syllibol         | Min  | Тур  | Max                    | Offic |

|                         |            | V <sub>DDE</sub> | 2.3  | 2.5  | 2.7                    | V     |

| Supply voltage          |            | V <sub>DDI</sub> | 1.0  | 1.1  | 1.2                    | V     |

|                         |            |                  | 1.4  | 1.5  | 1.6                    | V     |

| "H" level input voltage | 2.5 V CMOS | VIH              | 1.7  | _    | V <sub>DDE</sub> + 0.3 | V     |

| "L" level input voltage | 2.5 V CMOS | VIL              | -0.3 | _    | +0.7                   | V     |

| Junction temperature    |            | Tj               | -40  | _    | +125                   | °C    |

# WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC characteristics

• Signal power supply : VDD = 1.8 V

(V<sub>DD</sub> = 1.8 V  $\pm$  0.15 V, V<sub>SS</sub> = 0 V, Tj = -40 °C to +125 °C)

| Parameter                    | Symbol   | Conditions                                          | itions                |     | Value    |      |  |

|------------------------------|----------|-----------------------------------------------------|-----------------------|-----|----------|------|--|

| Parameter                    | Syllibol | Conditions                                          | Min                   | Тур | Max      | Unit |  |

| Supply Current               | IDDS     | _                                                   | _                     | _   | *        | mA   |  |

| "H" level output voltage     | Vон      | $I$ он = $-100 \mu A$                               | V <sub>DD</sub> - 0.2 | _   | $V_{DD}$ | V    |  |

| "L" level output voltage     | Vol      | $I_{OL} = +100 \mu A$                               | 0                     | _   | 0.2      | V    |  |

| Input leakage current        | IL       | _                                                   | _                     | _   | ±5       | μΑ   |  |

| Pull up/Pull down resistance | Rp       | Pull up $V_{IL} = 0$<br>Pull down $V_{IH} = V_{DD}$ | _                     | 18  | _        | kΩ   |  |

<sup>\*:</sup> For details of YS, YI, B frame of CS81 series, contact the sales representative.

• Dual power supply :  $V_{DDE} = 3.3 \text{ V}$ ,  $V_{DDI} = 1.8 \text{ V}$  ( $V_{DDE} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $V_{DDI} = 1.8 \text{ V} \pm 0.15 \text{ V} / 1.5 \text{ V} \pm 0.1 \text{ V} / 1.1 \text{ V} \pm 0.1 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_j = -40 \, ^{\circ}\text{C}$  to  $+125 \, ^{\circ}\text{C}$ )

| Parameter                       | Cymbol                      | Conditions                                                                         | Value                  |     |                  | Unit  |

|---------------------------------|-----------------------------|------------------------------------------------------------------------------------|------------------------|-----|------------------|-------|

| Parameter                       | Symbol                      | Conditions                                                                         | Min                    | Тур | Max              | Unit  |

| Supply Current                  | IDDS                        | _                                                                                  | _                      | _   | *1               | mA    |

| "Ll" lovel output voltoge       | <b>V</b> OH4                | 3.3 V Output Ioн = -100 μA                                                         | V <sub>DDE</sub> - 0.2 | _   | V <sub>DDE</sub> | V     |

| "H" level output voltage        | V <sub>OH2</sub>            | 1.8 V Output Ioн = -100 μA                                                         | V <sub>DDI</sub> - 0.2 | _   | V <sub>DDI</sub> | V     |

| "I " lovel output voltoge       | V <sub>OL4</sub>            | 3.3 V Output IoL = 100 μA                                                          | 0                      | _   | 0.2              | V     |

| "L" level output voltage        | V <sub>OL2</sub>            | 1.8 V Output IoL = 100 μA                                                          | 0                      | _   | 0.2              | V     |

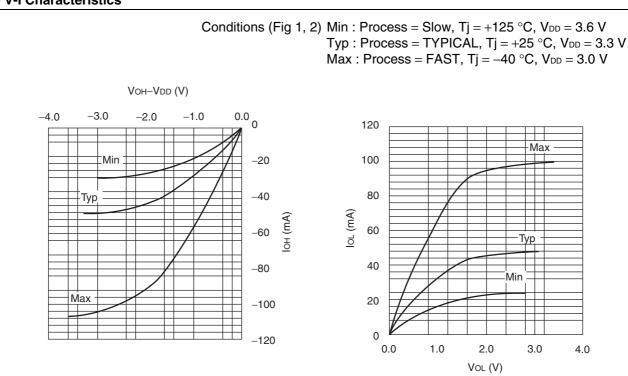

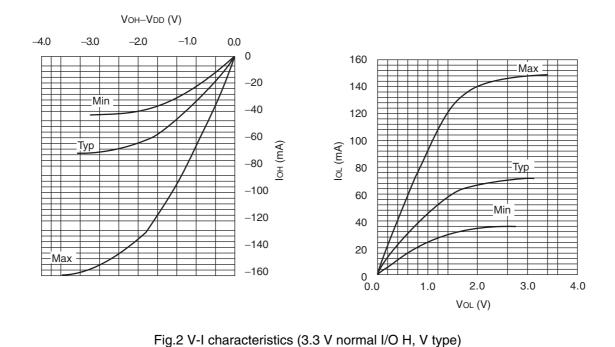

| "H" level output V-I            |                             | 3.3 V<br>VDDE = 3.3 V±0.3 V                                                        |                        | *2  |                  | _     |

| characteristics                 | _                           | 1.8 V<br>V <sub>DDI</sub> = 1.8 V±0.15 V                                           |                        | _   |                  | _     |

| "L" level output V-l            |                             | 3.3 V<br>VDDE = 3.3 V±0.3 V                                                        |                        | *2  |                  | _     |

| characteristics                 |                             | 1.8 V<br>V <sub>DDI</sub> = 1.8 V±0.15 V                                           |                        |     |                  | _     |

| Input leakage current           | IL                          | _                                                                                  | _                      | _   | ±5               | μΑ    |

| Pull up/Pull down<br>resistance | Rp Pul<br>Pul<br>3.3<br>Pul | 1.8 V<br>Pull up V <sub>IL</sub> =0<br>Pull down V <sub>IH</sub> =V <sub>DDI</sub> | _                      | 18  | _                | kΩ    |

|                                 |                             | 3.3 V<br>Pull up V <sub>IL</sub> =0<br>Pull down V <sub>IH</sub> =V <sub>DDE</sub> | 10                     | 33  | 80               | 1 K22 |

<sup>\*1 :</sup> For details of YS, YI, B frame of CS81 series, contact the sales representative.

<sup>\*2 :</sup> Refer to the Fig.1 to 2.

• Dual power supply :  $V_{DDE} = 2.5 \text{ V}$ ,  $V_{DDI} = 1.8 \text{ V} / 1.5 \text{ V} / 1.1 \text{ V}$  ( $V_{DDE} = 2.5 \text{ V} \pm 0.2 \text{ V}$ ,  $V_{DDI} = 1.8 \text{ V} \pm 0.15 \text{ V} / 1.5 \text{ V} \pm 0.1 \text{ V} / 1.1 \text{ V} \pm 0.1 \text{ V}$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_j = -40 \text{ °C to } +125 \text{ °C}$ )

| Doromotor                 | Symbol Conditions |                                                                                    |                        |     | Unit             |       |

|---------------------------|-------------------|------------------------------------------------------------------------------------|------------------------|-----|------------------|-------|

| Parameter                 |                   |                                                                                    | Min                    | Тур | Max              | Onit  |

| Supply Current            | IDDS              | _                                                                                  | _                      |     | *                | mA    |

| "L" lovel output voltage  | Vонз              | 2.5 V Output Io <sub>H</sub> = -100 μA                                             | V <sub>DDE</sub> - 0.2 | _   | V <sub>DDE</sub> | V     |

| "H" level output voltage  | V <sub>OH2</sub>  | 1.8 V Output Ioн = -100 μA                                                         | V <sub>DDI</sub> - 0.2 | _   | V <sub>DDI</sub> | V     |

| "I " lovel output voltage | Vol3              | 2.5 V Output IoL = 100 μA                                                          | 0                      |     | 0.2              | V     |

| "L" level output voltage  | V <sub>OL2</sub>  | 1.8 V Output IoL = 100 μA                                                          | 0                      | _   | 0.2              | V     |

| Input leakage current     | IL                | _                                                                                  | _                      |     | ±5               | μΑ    |

| Pull up/Pull down         | Po                | 2.5 V<br>Pull up V <sub>IL</sub> =0<br>Pull down V <sub>IH</sub> =V <sub>DDE</sub> | _                      | 25  | _                | - kΩ  |

| resistance                | Rp                | 1.8 V<br>Pull up V <sub>IL</sub> =0<br>Pull down V <sub>IH</sub> =V <sub>DDI</sub> | _                      | 18  | _                | - K22 |

<sup>\*:</sup> For details of YS, YI, B frame of CS81 series, contact the sales representative.

#### • V-I Characteristics

Fig.1 V-I characteristics (3.3 V normal I/O L, M type)

#### 2. AC characteristics

$(V_{DD} = 1.8 \text{ V} \pm 0.15 \text{ V}, \text{ Vss} = 0 \text{ V}, \text{ Tj} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C})$

| Parameter  | Symbol             | Rating         |                             |                | Unit  |

|------------|--------------------|----------------|-----------------------------|----------------|-------|

| raiametei  | Symbol             | Min            | Тур                         | Max*           | Offic |

| Delay time | t <sub>pd</sub> *1 | typ*2 × tmin*3 | $typ^{*2} \times ttyp^{*3}$ | typ*2 × tmax*3 | ns    |

<sup>\*1 :</sup> Delay time = propagation delay time, enable time, disable time

<sup>\*3 :</sup> Measurement conditions.

| Measurement condition                                                                                                                       | tmin | ttyp | tmax |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| $V_{DD} = 1.8 \text{ V} \pm 0.15 \text{ V}, \text{ Vss} = 0 \text{ V}, \text{ Tj} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$ | 0.64 | 1.00 | 1.58 |

| $V_{DD} = 1.5 \text{ V} \pm 0.10 \text{ V}, \text{ Vss} = 0 \text{ V}, \text{ Tj} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$ | 0.83 | 1.31 | 2.05 |

| $V_{DD} = 1.1 \text{ V} \pm 0.10 \text{ V}, \text{ Vss} = 0 \text{ V}, \text{ Tj} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$ | 1.37 | 2.45 | 4.88 |

Note: tpd max is calculated according to the maximum junction temperature (Tj).

#### ■ INPUT/OUTPUT PIN CAPACITANCE

$(T_i = +25 \, {}^{\circ}C, \, V_{DD} = V_i = 0 \, V, \, f = 1 \, MHz)$

| Parameter  | Symbol | Requirements | Unit |

|------------|--------|--------------|------|

| Input pin  | Cin    | Max 16       | pF   |

| Output pin | Соит   | Max 16       | pF   |

| I/O pin    | Cı/o   | Max 16       | pF   |

Note: Capacitance varies according to the package and the location of the pin.

## **■ DESIGN METHOD**

SCCAD2 is the standard cell integrated design environment providing three major functions, enabling high-quality, large-scale system LSIs to be developed in a shorter period of time. They include: the timing driven layout function for automatic placement/routing based on timing constraints to prevent timing problems after layout, the function for shortening the development cycle time by dividing a large-scale circuit and performing simultaneous logical/physical design of multiple circuits, and the function for automatically generating power/ signal wiring patterns while evaluating the supply voltage drop, signal noise, delay penalty, and crosstalk (Contact your nearest Fujitsu Semiconductor office for more information and availability).

<sup>\*2 : &</sup>quot;typ" is calculated based on the cell specifications.

## **■ PACKAGES**

The table below lists the package types available.

Consult Fujitsu Semiconductor for the combination of each package and the time of availability.

| Package | Pin count                                                          | Material |

|---------|--------------------------------------------------------------------|----------|

| HQFP    | 208<br>240<br>256<br>304                                           | Plastic  |

| LQFP    | 144<br>176<br>208                                                  | Plastic  |

| FBGA    | 112<br>133<br>176<br>192<br>224<br>240<br>272<br>288<br>304<br>368 | Plastic  |

| FCBGA   | 1089<br>1225<br>1369<br>1681<br>1849<br>2116                       | Plastic  |

# **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### **Europe**

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 902 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fsk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD.

151 Lorong Chuan,

#05-08 New Tech Park 556741 Singapore

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China

Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: +852-2377-0226 Fax: +852-2376-3269 http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department