### **ASSP**

# ISO/IEC 18000-6 Type-C Compliant FRAM Embedded UHF Band RFID LSI *FerVID family*™

### MB97R803A/B, MB97R804A/B

#### **■ OVERVIEW**

This specification defines the LSI specification for the passive RFID Tag LSI "MB97R803A/B, MB97R804A/B" based on international standard "EPCglobal Class 1 Generation 2 (Ver.1.2.0).

In this document, the term "interrogator" used in the EPCglobal standard is changed to R/W (reader/writer) in accordance with customary practice. The term "Tag" is used as it is.

#### **■ FEATURE**

- Compliant with EPCglobal Class 1 Generation 2 (C1G2) Ver.1.2.0

- Compliant with all UHF bands all over the world (carrier frequency: 860 MHz to 960 MHz)

- High-speed data transmission (compliant with EPCglobal C1G2)

$\mbox{R/W} \rightarrow \mbox{Tag:} 26.7 \mbox{ kbps}$  to 128 kbps (when the counts of data 0 and 1are equal)

Tag  $\rightarrow$  R/W: 40 kbps to 640 kbps

- DSB-ASK, SSB-ASK, PR-ASK modulation (compliant with EPCglobal C1G2)

- Anti-collision function

- Frequency Hopping

- BlockPermalock: User memory area can be locked from writing in unit of 1 block (16 bits).

- ReadLock (custom command): User memory area can be locked from reading in unit of 1 Area (256 bits)

- Serial Interface (SPI)

- Accessible area: User memory area can be read/written through SPI.

- Access control with RF interface is prioritized

- Power supply: 2.3 V to 3.6 V (power is required for the memory access via SPI.)

- Low power consumption : Operating current=70μA(Typ@2MHz),

Standby current=10µA(Typ)

- Power down mode : Power down current =10nA(Typ)

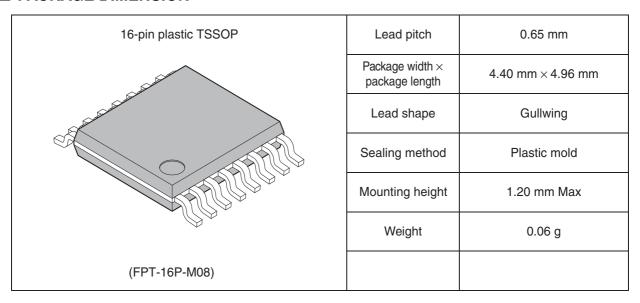

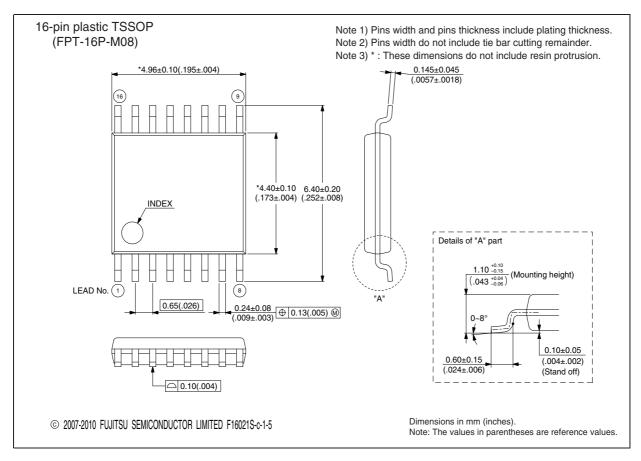

- Package: 16-pin TSSOP (FPT-16P-M08)

- FRAM 4 Kbytes (4,096 bytes): High speed read/write Non-volatile memory

- User Memory Area: 3,424 bytes

- System Memory Area (including Reserved, EPC, and TID): 672 bytes

- Read/Write Endurance: 10<sup>10</sup> times

- Memory Data Retention: 10years ( + 55 °C)

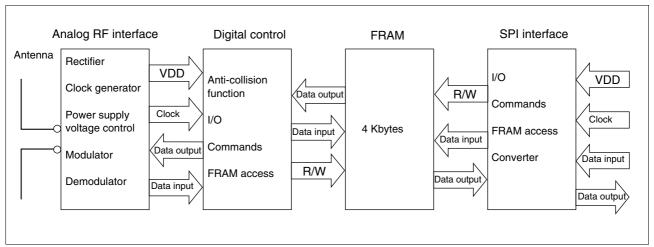

#### **■ BLOCK DIAGRAM**

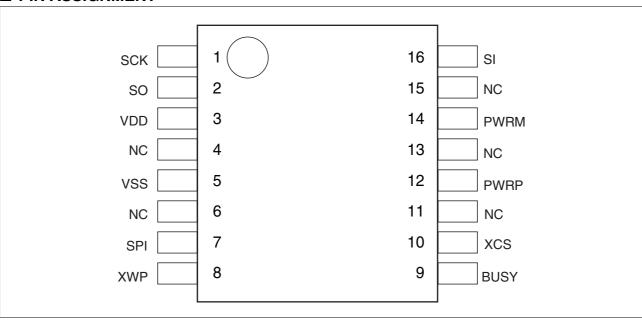

#### **■ PIN ASSIGNMENT**

| Pin Number   | Pin Name | Interface         | Function Description                                 |  |

|--------------|----------|-------------------|------------------------------------------------------|--|

| 12           | PWRP     | RF                | Antenna pin                                          |  |

| 14           | PWRM     | RF                | Antenna pin                                          |  |

| 9            | BUSY     | Serial            | RF Interface Status pin                              |  |

| 7            | SPI      | Serial            | SPI Mode Switch pin                                  |  |

| 10           | XCS      | Serial            | Chip Select pin                                      |  |

| 8            | XWP      | Serial            | Write Protect pin                                    |  |

| 1            | SCK      | Serial            | Serial Clock pin                                     |  |

| 16           | SI       | Serial            | Serial Data Input pin                                |  |

| 2            | SO       | Serial            | Serial Data Output pin                               |  |

| 3            | VDD      | Serial            | Supply Voltage pin                                   |  |

| 5            | VSS      | Serial Ground pin |                                                      |  |

| 4,6,11,13,15 | NC       | -                 | No Connection pin (There is no internal connection.) |  |

#### **■ RF INTERFACE**

RF signal interface is compliant with EPCglobal C1G2 Ver.1.2.0 (as described in 6.3.1).

#### **■ SERIAL INTERFACE**

This LSI has SPI (Serial Peripheral Interface) interface. It is able to access FRAM User memory through the SPI interface. In this case, the external power supply is required.

#### 1. Pin Function Description

The Serial Pin and its function descriptions are shown in the table below.

• Pin function

| Pin Number | Pin Name | Function Description                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9          | BUSY     | RF interface status pin When the VDD pin is set to ON during RF communication, BUSY will output "H". In this status, Serial communication will be ignored even if RF and Serial communications are both being performed at the same time, because the chip can only perform RF communication when BUSY outputs "H". Switching to the serial communication can be performed only when BUSY is "L". |

| 7          | SPI      | SPI Mode Switch pin This is an input pin to control to switch to Serial communication mode. When SPI is "H", the LSI can be transfer to Serial communication mode.                                                                                                                                                                                                                                |

| 10         | XCS      | Chip Select pin This is an input pin to select chip. When XCS is "H", device is deselect (standby status) as long as the LSI is not write status internally. And SO becomes High-Z. In this case, inputs from all pins other than the antenna pin are ignored. When XCS is "L", the chip will be in selected state (active). XCS must fall before inputting opcode.                               |

| 8          | XWP      | Write Protect pin This is an input pin to protect FRAM from writing. When WXP is "L", FRAM memory is protected.                                                                                                                                                                                                                                                                                   |

| 1          | SCK      | Serial Clock pin This is a clock input pin to input/output serial data. SI is loaded synchronously to a rising edge. SO is output synchronously to a falling edge.                                                                                                                                                                                                                                |

| 16         | SI       | Serial Data Input pin This is an input pin of serial data. It inputs op-code, address, and writing data.                                                                                                                                                                                                                                                                                          |

| 2          | SO       | Serial Data Output pin This is an output pin of serial data. Reading data of FRAM memory are output. Its High-Z during standby.                                                                                                                                                                                                                                                                   |

| 3          | VDD      | Supply Voltage pin: 2.3 V to 3.6 V                                                                                                                                                                                                                                                                                                                                                                |

| 5          | VSS      | Ground pin                                                                                                                                                                                                                                                                                                                                                                                        |

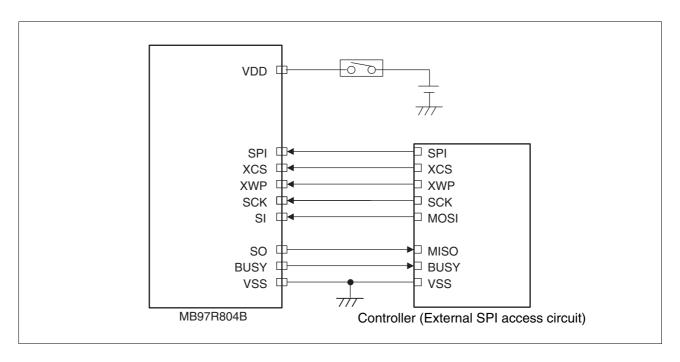

#### 2. Connection to SPI Interface

This LSI works as a slave of SPI. It can be connected to the microcontroller equipped with SPI port as shown in the figure below.

The external SPI controller shall monitor the BUSY signal. When BUSY signal is "H", the external power must be disconnected and the other signal must be "L".

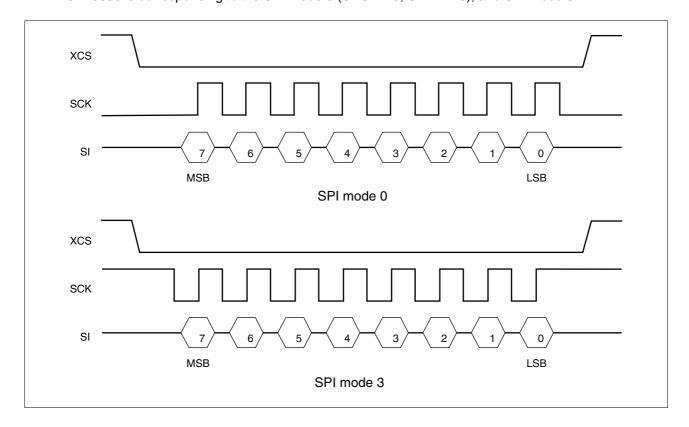

#### 3. SPI Mode

MB97R8030 is corresponding to the SPI mode 0 (CPOL = 0, CPHA = 0), and SPI mode 3.

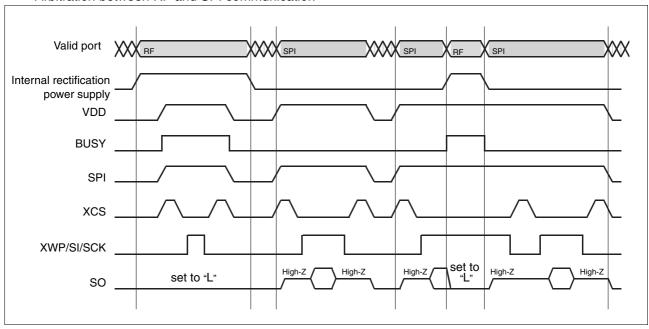

#### 4. Arbitration between RF and SPI communication

This LSI has access arbitration feature when there is access from both RF I/F and SPI I/F simultaneously. In this case, RF communication has priority.

BUSY signal indicates that there is access from RF I/F, and it is validated when VDD is connected.

The controller needs to confirm the BUSY signal before changing to the SPI communication mode. When the BUSY signal is in "H", the SPI communication is ignored if the SPI communication is performed at the same time because the LSI is executing RF communication.

The BUSY pin outputs "H" if the VDD pin is turned on during RF communication as the figure shown below.

#### • Arbitration between RF and SPI communication

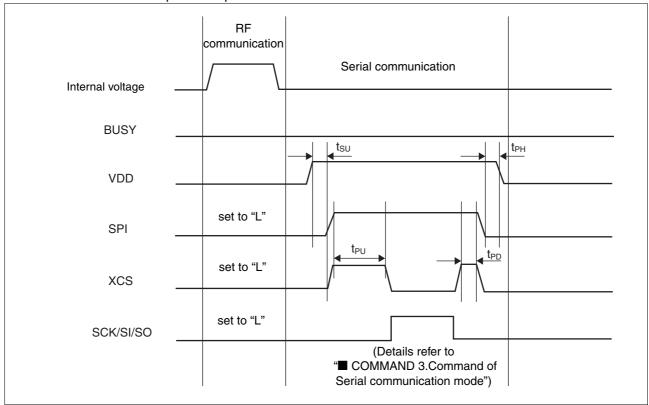

#### 5. Power Sequence in Serial Communication Mode

The power sequence in Serial communication mode is shown in the figure below.

After asserting VDD, check that BUSY is "L" and then assert SPI and XCS at the same time. Wait for 1 ms or more after asserting XCS and then release XCS and begin Serial communication. The timing specifications for the power sequence are shown in the following table. Refer to " COMMAND 3. Command of Serial communication mode" for details on the Serial communication timing specifications.

#### • Serial communication power sequence

#### • Timing specifications during Serial communication

| Parameter                        | Symbol      | Value (Min) | Unit |

|----------------------------------|-------------|-------------|------|

| SPI rising start time            | tsu         | 0           | μs   |

| Power supply hold time           | tрн         | 0           | μs   |

| XCS level hold time at power ON  | <b>t</b> PU | 1000        | μs   |

| XCS level hold time at power OFF | <b>t</b> PD | 0.06        | μs   |

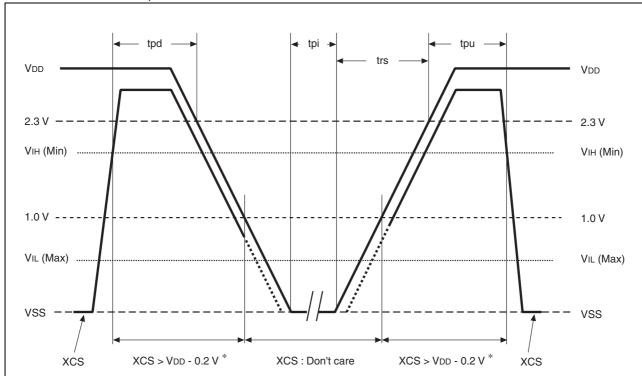

#### 6. XCS Level Hold Time at Power ON/OFF

Power ON/OFF sequence while switching to the serial communication is shown in the figure below and XCS level hold time at power ON/OFF is shown in the table below.

• Power ON/OFF sequence in serial communication

\*: XCS (Max)< V<sub>DD</sub> + 0.5 V

Note • Since power ON from middle-level may cause malfunction, VDD should rise from 0 V at power ON.

• If any operation other than the specified read cycle, write cycle or power ON/OFF sequence is performed, the stored data cannot be guaranteed.

| Parameter                        | Symbol | Va   | Unit |       |

|----------------------------------|--------|------|------|-------|

| Farameter                        | Symbol | Min  | Max  | Oille |

| XCS level hold time at power OFF | tpd    | 0.06 | _    | us    |

| XCS level hold time at power ON  | tpu    | 1000 | _    | us    |

| Power supply falling time        | tpi    | 10   |      | ms    |

| Power supply rising time         | trs    | 0.05 | 200  | ms    |

#### ■ MEMORY

#### 1. Memory addressing

#### (1) Memory addressing in RF communication mode

Memory addressing in RF communication mode use Extensible bit vectors (EBV) format, which is compliant with EPCglobal C1G2 Ver1.2.0 (Annex A).

#### (2) Memory addressing in Serial communication mode

The logical address is used for memory addressing in Serial communication mode.

#### 2. Memory Map

#### (1) Memory area

The memory is divided into the following five areas.

· Five memory areas

|          |                 |   |      |               |                  | Access command    |               |               |     |

|----------|-----------------|---|------|---------------|------------------|-------------------|---------------|---------------|-----|

| Name     | ame Memory size |   | BANK | Address range | RF communication | SPI communication |               |               |     |

| User     | 1712w           | × | 16b  | =             | 27,392bit        | 11                | 000н to 06AFн | R/W/S/BLW/BLE | R/W |

| TID      | 16w             | × | 16b  | =             | 256bit           | 10                | 000н to 00Fн  | R/S           | R   |

| EPC      | 35w             | × | 16b  | =             | 560bit           | 01                | 000н to 022н  | R/W/S/BLW/BLE | R   |

| Reserved | 4w              | × | 16b  | =             | 64bit            | 00                | 000н to 003н  | R/W           | _   |

| System   | 14w             | × | 16b  | =             | 224bit           | _                 |               | L/BPL         | *   |

<sup>\* :</sup> Only lock and SPI error information can be read

Note: Command abbreviation:

R:READ, W: WRITE, S: SELECT, L: Lock, BPL: BlockPermalock, BLW: BlockWrite, BLE: BlockErase

The User, TID, EPC, and Reserved memory areas contain the data that is defined by the EPCglobal C1G2 specification (Chapter 6.3.2.1). The memory areas are also called as "Memory bank or "Bank" in EPC standard (In this specification, the User memory area is also called as "User memory").

In each memory bank, the logical address starts from zero (00H).

Logical addressing in EBV-8 format is used.

The system area stores user memory lock information and AreaGroup passwords.

The memory map is shown in shown in the table on next page. (The system area is not disclosed). The User memory consists of 7 Area Group and 107 Areas. The Area is defined as " $16 \times 16$  bits word" (256 bits)" of data and each AreaGroup contains several areas. The first 6 AreaGroup contain 16 areas, the last AreaGroup contains 11 areas.

In addition, the idea of "Bank" "Area" and "AreaGroup" shall be ignored when using the Serial communication mode.

#### Memory map

| Bank         | emory | Logical Addr<br>(RF communic | ess<br>ation) | Logical<br>Address | Data Des                 | cription      | Size   | Total  | Total      |

|--------------|-------|------------------------------|---------------|--------------------|--------------------------|---------------|--------|--------|------------|

|              | bank  | (bit)                        | (word)        | (SPI)              |                          | •             | (word) | (word) | (bit)      |

|              |       | 00000н - 000FFн              | 0000н - 000Fн | 0000н - 000Fн      |                          | Area00        | 16     |        |            |

|              |       | 00100н - 001FFн              | 0010н - 001Fн | 0010н - 001Fн      | A O                      | Area01        | 16     |        |            |

|              |       | 00200н - 00ЕFFн              | 0020н - 00ЕГн | 0020н - 00ЕГн      | AreaGroup00              | Area02 - 14   | 208    |        |            |

|              |       | 00F00н - 00FFFн              | 00F0н - 00FFн | 00F0н - 00FFн      |                          | Area15        | 16     |        |            |

| USER         | 11    | 01000н - 01FFFн              | 0100н - 01FFн | 0100н - 01FFн      | AreaGroup01              | Area00 - 15   | 256    | 1 710  | 07.000     |

| USER         | 11    | 02000н - 02FFFн              | 0200н - 02FFн | 0200н - 02FFн      | AreaGroup02              | Area00 - 15   | 256    | 1,712  | 27,392     |

|              |       | 03000н - 03FFFн              | 0300н - 03FFн | 0300н - 03FFн      | AreaGroup03              | Area00 - 15   | 256    |        |            |

|              |       | 04000н - 04FFFн              | 0400н - 04FFн | 0400н - 04FFн      | AreaGroup04              | Area00 - 15   | 256    |        |            |

|              |       | 05000н - 05FFFн              | 0500н - 05FFн | 0500н - 05FFн      | AreaGroup05              | Area00 - 15   | 256    |        |            |

|              |       | 06000н - 06АFFн              | 0600н - 06АГн | 0600н - 06АГн      | AreaGroup06              | Area00 - 10   | 176    |        |            |

|              |       | 00000н - 0000Fн              | 0000н - 0000н | 06С0н - 06С0н      | StoredCRC16 (            | PC, EPC)      | 1      |        |            |

|              |       | 00010н - 0001Fн              | 0001н - 0001н | 06С1н - 06С1н      | StoredPC (Prot           | ocol Control) | 1      |        |            |

| EPC          | 1     | 00020н - 0020Fн              | 0002н - 0020н | 06С2н - 06ЕОн      | EPC                      |               | 31     | 35     | 560        |

|              |       | 00210н - 0021Fн              | 0021н - 0021н | 06Е1н - 06Е1н      | XPC_W1                   |               | 1      |        |            |

|              |       | 00220н - 0022Fн              | 0022н - 0022н | 06Е2н - 06Е2н      | XPC_W2                   |               | 1      |        |            |

| TID          | 10    | 00000н - 000FFн              | 0000н - 000Fн | 06F0н - 06FFн      | TID                      |               | 16     | 16     | 256        |

|              |       | 00000н - 0000Fн              | 0000н - 0000н | 076Сн - 076Сн      | KILL - Passwor           | d[31:16]      | 1      |        |            |

| Re-          | 00    | 00010н - 0001Fн              | 0001н - 0001н | 076Dн - 076Dн      | KILL - Passwor           | d[15:0]       | 1      | 4      | 64         |

| served       | 00    | 00020н - 0002Fн              | 0002н - 0002н | 076Ен - 076Ен      | ACCESS - Password[31:16] |               | 1      |        | 04         |

|              |       | 00030н - 0003Fн              | 0003н - 0003н | 076Fн - 076Fн      | ACCESS - Password[15:0]  |               | 1      |        |            |

| Lock         |       | _                            |               | 06Е5н - 06Е5н      | {LOCK[9:0], 5'h0, BPLI}  |               | 1      | 1      | 16         |

|              |       |                              |               | 0778н - 0778н      | AreaGroup00              | Area00 - 15   | 1      |        |            |

|              |       |                              |               | 0779н - 0779н      | AreaGroup01              | Area00 - 15   | 1      |        |            |

| Deed         |       |                              |               | 077Ан - 077Ан      | AreaGroup02              | Area00 - 15   | 1      |        |            |

| Read<br>Lock |       | _                            |               | 077Вн - 077Вн      | AreaGroup03              | Area00 - 15   | 1      | 7      | 112        |

|              |       |                              |               | 077Сн - 077Сн      | AreaGroup04              | Area00 - 15   | 1      |        |            |

|              |       |                              |               | 077Dн - 077Dн      | AreaGroup05              | Area00 - 15   | 1      |        |            |

|              |       |                              |               | 077Ен - 077Ен      | AreaGroup06              | Area00 - 10   | 1      |        |            |

|              |       |                              |               | 0780н - 0780н      |                          | Area00        | 1      |        |            |

|              |       |                              |               | 0781н - 0781н      | AreaGroup00              | Area01        | 1      |        |            |

|              |       |                              |               | 0782н - 078Ен      | 7 oa o oapoo             | Area02 - 14   | 13     |        |            |

|              |       |                              |               | 078Fн - 078Fн      |                          | Area15        | 1      |        |            |

| BPL          |       |                              |               | 0790н - 079Fн      | AreaGroup01              | Area00- 15    | 16     | 107    | 1,712      |

| ··· <b>-</b> |       |                              |               | 07А0н - 07АГн      | AreaGroup02              | Area00 - 15   | 16     |        | , <u>-</u> |

|              |       |                              |               | 07В0н - 07ВГн      | AreaGroup03              | Area00 - 15   | 16     |        |            |

|              |       |                              |               | 07С0н - 07СFн      | AreaGroup04              | Area00 - 15   | 16     |        |            |

|              |       |                              |               | 07D0н - 07DFн      | AreaGroup05              | Area00 - 15   | 16     |        |            |

|              |       |                              |               | 07Е0н - 07ЕАн      | AreaGroup06              | Area00 - 10   | 11     |        |            |

#### • TID

This LSI has a 96 bits TID that complies with EPC C1G2 standard. The TID consist of the 4 items shown in the following.

- An 8 bits data of EPC whose value is always "E2H" (bit89 to bit96)

- "A 12 bits IC manufacture code whose values is always "010H" (bit77 to bit88)

- Unique 60 bits serial number assigned by Fujitsu Semiconductor (bit17 to bit76)

- RFU 16 bits (bit1 to bit16)

Among the unique 60 bits serial number assigned by Fujitsu Semiconductor, the 8 bits from bit69 to bit76 define MB97R8030 code whose value is "03<sub>H</sub>". And 52 bits from bit17 to bit68 define chip information.

• TID configuration

| MSB          |             |     |    |              |                                          |    | L    | .SB |

|--------------|-------------|-----|----|--------------|------------------------------------------|----|------|-----|

| 96 89        | 88          | 77  | 76 | 69           | 68 17                                    | 16 |      | 1   |

| EPC standard | I(<br>manuf |     |    | "06⊦"        | Chip information                         |    | RFU* |     |

| "Е2н"        | "01         | 0н" | u  | nique serial | number assigned by FUJITSU SEMICONDUCTOR |    |      |     |

#### \*: Reserved for Future Use

#### · Notes on TID

TID has been written in FRAM during shipment test by the Fujitsu Semiconductor. However, FUJITSU SEMICONDUCTOR do not guarantee that the data written in FRAM before IR reflow is still retained after IR reflow. If this may cause problems, TID should be written by the customer after IR reflow.

#### **■ FLAGS AND RANDOM NUMBER GENERATOR**

The inventoried flag, selected flag, and random number generator are compliant with EPCglobal C1G2 Ver. 1.2.0. (Chapter 6.3.2.2, 6.3.2.3, 6.3.2.5)

#### **■ TAG STATES AND SLOT COUNTER**

The Tag states and slot counter are compliant with EPCglobal C1G2 Ver. 1.2.0. (Chapter 6.3.2.4)

#### **■ COLLISION ARBITRATION ALGORITHM**

The collision arbitration algorithm is compliant with EPCglobal C1G2 Ver. 1.2.0. (Chapter 6.3.2.6, 6.3.2.7, 6.3.2.8, 6.3.2.9)

#### **■ COMMAND**

#### 1. Command of RF communication mode.

This LSI supports all mandatory commands and optional commands that defined by EPCglobal C1G2 Ver. 1.2.0. (Chapter 6.3.2.11). In addition, the ChgAreaGroupPwd and ReadLock is supported as custom command. The commands list and codes is shown in the table below.

For BlockWrite and BlockErase command (Optional command), parts of the specifications are different form the EPC C1G2 standard as described in "(1)BlockWrite (Optional command)" and "(2)BlockErase (Optional command)". ChgAreaGroupPwd and ReadLock command (Custom command) are described in "(4)ChgAreaGroupPwd (Custom command)" and "(5)ReadLock (Custom command)". Initialize command(Proprietary command) is described in "(6)Initialize(Proprietary command)".

#### • Command of RF communication mode

| Items       | Command         | Code             |  |  |

|-------------|-----------------|------------------|--|--|

|             | QueryRep        | 00               |  |  |

|             | ACK             | 01               |  |  |

|             | Query           | 1000             |  |  |

|             | QueryAdjust     | 1001             |  |  |

|             | Slect           | 1010             |  |  |

| Mandatory   | NAK             | 11000000         |  |  |

|             | Req_RN          | 11000001         |  |  |

|             | Read            | 11000010         |  |  |

|             | Write           | 11000011         |  |  |

|             | Kill            | 11000100         |  |  |

|             | Lock            | 11000101         |  |  |

|             | Access          | 11000110         |  |  |

| Optional    | BlockWrite      | 11000111         |  |  |

| Ориона      | BlockErase      | 11001000         |  |  |

|             | BlockPermalock  | 11001001         |  |  |

| Custom      | ChgAreaGroupPwd | 111000000000100  |  |  |

| Gustom      | ReadLock        | 111000000000111  |  |  |

| Proprietary | Initialize      | 1110000100001111 |  |  |

#### Differences from EPCglobal C1G2 Ver. 1.2.0

• CRC-16

When the R/W writes the entire or part of the PC or EPC area of the Tag, CRC-16 stored in EPC memory  $00_H$  to  $0F_H$  of the Tag is disabled until an ACK command is received and a response that is not truncated (PC, EPC, CRC-16) is returned. After the completion of responding to ACK command, the correct CRC-16 value calculated during responding is written to EPC memory ( $00_H$  to  $0F_H$ ) as well. If a truncated response to the ACK command is requested before CRC-16 is enabled, the CRC-16 value in the EPC memory, which has not been enabled, is returned as is.

• T4 time (time duration between commands sent by R/W)

The minimum value of T4 time is different from the value defined in EPC standards depending on the length of RTcal.

| Length of RTcal         | Minimum value of T4 time           |

|-------------------------|------------------------------------|

| 44usec ≤ RTcal          | 2.0RTcal (EPC standards compliant) |

| 22usec ≤ RTcal < 44usec | 4.0RTcal                           |

| RTcal < 22usec          | 6.0RTcal                           |

#### (1) BlockWrite (Optional command)

The following table shows the format of the BlockWrite command. Parts of the function of BlockWrite command are different form the EPCglobal C1G2 Ver.1.2.0 as following.

• MemBank : BlockWrite command can be executed in EPC and User memory bank. If BlockWrite command executed to the Reserved and TID bank, the LSI reply an error code.

• WordCount: If the WordCount is specified over 17 (11H), the LSI will reply an error code.

If part of the words to be written is locked by the BlockPermaLock, the LSI reply an error code.

#### • BlockWrite command

|             | Command   | MemBank             | WordPtr                        | WordCount                     | Data                  | RN     | CRC-16 |

|-------------|-----------|---------------------|--------------------------------|-------------------------------|-----------------------|--------|--------|

| # of bits   | 16        | 2                   | EBV                            | 8                             | WordCount ×<br>16     | 16     | 16     |

| Description | 1100 0111 | 01: EPC<br>11: User | Starting<br>Address<br>Pointer | Number of<br>word to<br>write | Data to be<br>written | Handle |        |

#### (2) BlockErase (Optional command)

The following table shows the format of the BlockErase command. Parts function of BlockErase command are different form the EPCglobal C1G2 Ver.1.2.0 as described as follows.

MemBank : BlockErase command can be executed in EPC and User memory bank. If BlockErase executed to the Reserved and TID bank, the LSI reply an error code.

• WordCount: If the WordCount is specified over 17 (11H), this LSI will reply an error code.

If part of the words to be erased is locked by the BlockPermaLock, the LSI reply an error code.

#### BlockErase command

|             | Command   | MemBank             | WordPtr                        | WordCount               | RN     | CRC-16 |

|-------------|-----------|---------------------|--------------------------------|-------------------------|--------|--------|

| # of bits   | 16        | 2                   | EBV                            | 8                       | 16     | 16     |

| Description | 1100 1000 | 01: EPC<br>11: User | Starting<br>Address<br>Pointer | Number of word to erase | Handle |        |

#### (3) BlockPermaLock (Optional command)

This LSI, the unit of 1 Block is defined as 16 bits. The format of the BlockPermaLock command is shown in the table below. Parts function of the BlockPermaLock command are different form the EPCglobal C1G2 Ver.1.2.0 as described as follows.

- MemBank : BlockPermaLock command can be executed for User memory bank. If BlockPermaLock command executed to the EPC, Reserved and TID bank, the LSI reply an error code.

- BlockRange: If the BlockRange is specified over 17 (11H), the LSI reply an error code.

#### BlockPermaLock command

|             | Command   | RFU | Read / Lock             | MemBank | BlockPtr                                                              | Block<br>Range                                          | Mask                                                                   | RN     | CRC-<br>16 |

|-------------|-----------|-----|-------------------------|---------|-----------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------|--------|------------|

| # of bits   | 16        | 8   | 1                       | 2       | EBV                                                                   | 8                                                       | Variable                                                               | 16     | 16         |

| Description | 1100 1001 | 00н | 0: Read<br>1: PermaLock | 11:User | Mask<br>starting<br>address,<br>specified in<br>units of<br>16 blocks | Mask<br>range,<br>specified<br>in units of<br>16 blocks | 0: Retain<br>current<br>permalock<br>setting<br>1: Assert<br>permalock | Handle |            |

#### (4) ChgAreaGroupPwd (Custom command)

The following table "ChgAreaGroupPwd command" shows the format of the ChgAreaGroupPwd command. The R/W can use ChgAreaGroupPwd to change the password of each AreaGroup. To change the password of the AreaGroup, the R/W shall send the existing and new passwords. The initial password set as "0" at shipment stage from factory.

Only the tag in the secured or open state can execute the ChgBlockGroupPwd command.

ChgAreaGroupPwd has the following fields:

- AreaGroupPtr: This LSI has four 4 AreaGroup (01 to 03), which is specified with 2 bit value. 3 bit values from MSB shall be padded with Zero "0"

- Data: specifies the new password.

- · Passwd specifies the current password.

The ChgBlockGroupPwd command also includes the Tag handle and CRC-16. The CRC-16 is calculated over the first command code bit to the last handle bit.

If a Tag in the open or secured state receives ChgAreaGroupPwd with a valid CRC-16 but an invalid handle, it shall ignore the ChgAreaGroupPwd and remain in its current state. If the password set in the Passwd field does not correspond to the stored value, the new password is not written. The Tag will not reply and return to the arbitrate state.

A ChgAreaGroupPwd shall be prepended with a frame-sync.

After issuing ChgAreaGroupPwd, the R/W transmit CW for the lesser of Treply or 20 ms, where Treply is the time between the R/W's ChgAreaGroupPwd command and Tag's backscattered reply. The R/W may observe several possible incomes from a ChgAreaGroupPwd, depending on the success or failure of the Tag's password change operation.

- ChgBlockGroupPwd succeeds: After complete the ChgAreaGroupPwd, the Tag return the response shown

in table "• Tag reply to ChgAreaGroupPwd command". The reply includes a header ("0" bit), Tag handle,

and CRC-16 calculated over the "0" bit and handle. If the R/W observes this reply within 20 ms then the

ChgAreaGroupPwd is completed successfully.

- The tag encounters an error: Tag returns an error code during the CW period rather than the reply shown in table "• Tag reply to ChgAreaGroupPwd command" (See "■COMMAND 4. Error of Serial communication mode" for the error code definition and reply format).

- Failure: If the R/W does not observe a reply within 20 ms then the ChgAreaGroupPwd does not complete successfully. The R/W may issue a Req\_RN command (containing the Tag's handle) to verify that the tag is still in the R/W filed, and may reissue the ChgAreaGroupPwd.

Upon receiving a valid ChgAreaGroupPwd command, the Tag rewrites the AreaGroup password with the specified data. The new password is valid immediately after rewriting. The tag's reply to a ChgAreaGroupPwd use the extended preamble. (i.e., the Tag reply as if TRext = 1 regardless of the TRext value in the Query that initiated the round).

#### ChgAreaGroupPwd command

|             | Command                | AreaGroupPtr | Data          | Password          | RN     | CRC-16 |

|-------------|------------------------|--------------|---------------|-------------------|--------|--------|

| # of bits   | 16                     | 5            | 32            | 32                | 16     | 16     |

| Description | 1110 0000<br>0000 0100 | AreaGroupPtr | New<br>Passwd | Current<br>Passwd | Handle |        |

#### Tag reply to ChgAreaGroupPwd command

|             | Header | RN     | CRC-16 |

|-------------|--------|--------|--------|

| # of bits   | 1      | 16     | 16     |

| Description | 0      | Handle |        |

#### (5) ReadLock (Custom command)

This LSI has the ReadLock function. The ReadLock command specifies the ReadLock status in the unit of Area (256 bits). The format of ReadLock command is shown in table "• ReadLock command".

Only the tag in the secured or open state can execute the ReadLock command.

- ReadLock has the following fields:

- AreaGroupPtr : This LSI has four 4 AreaGroup (1 to 6), which is specified with 3 bit value. 2 bit values from MSB shall be padded with Zero "0".

- ReadLock contains a 32-bit payload defined as follows.

- MASK0-15 0: Ignore the associated Action field and retain the current setting.

- 1: Implement the associated Action field and overwrite the current ReadLock setting.

- Action0-15 : Set the ReadLock status (1: Assert ReadLock, 0: Deassert ReadLock)

- Password: Set the corresponding password to the AreaGroup specified by the AreaGroupPtr. If the password is wrong, the ReadLock status can not be changed.

The AreaGroup6 does not contain Area 11 to Area 15, the setting toward these area is ignored.

The ReadLock command also includes the Tag handle and CRC-16. The CRC-16 is calculated over the first command code bit to the last handle bit.

If a Tag in the open or secured state receives ReadLock with a valid CRC-16 but an invalid handle, it shall ignore the ReadLock and remain in its current state.

A ReadLock shall be prepended with a frame-sync.

After issuing ReadLock, the R/W transmit CW for the lesser of Treply or 20 ms, where Treply is the time between the R/W's ReadLock command and Tag's backscattered reply. The R/W may observe several possible incomes from a ReadLock, depending on the success or failure of the Tag's memory lock operation.

• ReadLock succeeds

- : After complete the ReadLock, the Tag return the response shown in table "• Tag reply to ReadLock command". The reply includes a header ("0" bit),

- Tag handle, and CRC-16 calculated over the "0" bit and handle. If the R/W observes this reply within 20 ms then the ReadLock is completed successfully.

- The tag encounters an error: Tag returns an error code during the CW period rather than the reply shown in Table "• Tag reply to ReadLock command" (See "■COMMAND 4. Error of Serial communication mode" for the error code definition and reply format).

- Failure

: If the R/W does not observe a reply within 20 ms then the ReadLock does not complete successfully. The R/W may issue a Req\_RN command (containing the Tag's handle) to verify that the tag is still in the R/W filed, and may reissue the ReadLock.

Upon receiving a valid ReadLock command, the Tag perform the lock operation.

The tag's reply to a ReadLock use the extended preamble. (i.e., the Tag reply as if TRext = 1 regardless of the TRext value in the Query that initiated the round).

#### ReadLock command

|             | Command                | AreaGroupPtr | Payload                                 | Password        | RN     | CRC-16 |

|-------------|------------------------|--------------|-----------------------------------------|-----------------|--------|--------|

| # of bits   | 16                     | 5            | 32                                      | 32              | 16     | 16     |

| Description | 1110 0000<br>0000 0111 | AreaGroupPtr | Mask/Action<br>(See the table<br>below) | 32 bit password | Handle |        |

#### ReadLock command payload

|   | Payload                               |  |  |  |  |  |  |  |    |   |   |   |   |   |   |   |     |     |   |    |    |    |    |    |    |

|---|---------------------------------------|--|--|--|--|--|--|--|----|---|---|---|---|---|---|---|-----|-----|---|----|----|----|----|----|----|

|   | MASK                                  |  |  |  |  |  |  |  |    |   |   |   |   |   |   |   | Act | ion |   |    |    |    |    |    |    |

| 0 | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |  |  |  |  |  |  |  | 15 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7   | 8   | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

#### Tag reply to ReadLock command

|             | Header | RN     | CRC-16 |

|-------------|--------|--------|--------|

| # of bits   | 1      | 16     | 16     |

| Description | 0      | Handle |        |

#### (6) Initialize (Proprietary command)

The following table shows the format of the Initialize command. This command is provided for manufacturer to initialize the memory area excepting TID bank and part of system area after the IR reflow during tag assembly process. Data area and Lock information area are overwriten with data zero(0) and disabled to be intialized again. Once this command is executed, the System Lock status becomes to be Normal.

Initialize command shall be prepended with a frame-sync. Return link frequency is specified by Query command issued previously.

Initialize command can be executed from all the state excepting Kill state, and no tag is idetified by inventory sequence. Therefore it is not allowed to execute Initialize command if multiple tags are existed in the RF communication fields of reader/writer.

The command sequence is described as following.

- 1. R/W issues Query, in which DR value and M value specifies return link frequency.

- 2. R/W issues initialize command. Data field in the command has to be "00h".

- 3. Tag confirms CRC16. If the CRC16 is invalid, tag ignores the command.

- 4. If SYSLOCK information is NORMAL or KILL, tag ignores the commad.

- 5. The memory area excepting TID bank and part of system area is initialized (data zero(0) is overwritten.)

- 6. NOMAL value is stored in SYSLOCK information.

- 7. Tag responds to the command as shown in the following table.

#### • Initialize command

|             | Command             | Data | CRC-16 |

|-------------|---------------------|------|--------|

| # of bits   | 16                  | 8    | 16     |

| Description | 1110 0001 0000 1111 | 00H  |        |

#### · Tag reply to Initialize command

|             | Header | CRC-16 |  |  |  |  |

|-------------|--------|--------|--|--|--|--|

| # of bits   | 1      | 16     |  |  |  |  |

| Description | 0      |        |  |  |  |  |

#### 2. Error code of RF communication mode

The error code is compliant with EPCglobal C1G2 Ver. 1.2.0 (Annex I).

#### 3. Command of Serial communication mode

This LSI accepts 2 commands specified in Op-code. Op-code is an 8 bits code as shown in the table below. If other codes are inputted, the command is ignored. If XCS is risen during the input sequence of Op-code, the command cant be executed.

Op-code of Serial interface

| Name  | Function                                 | Op-code   |

|-------|------------------------------------------|-----------|

| READ  | Read from memory area in unit of 16 bits | 0000 0011 |

| WRITE | Write to memory area in unit of 16 bits  | 0000 0010 |

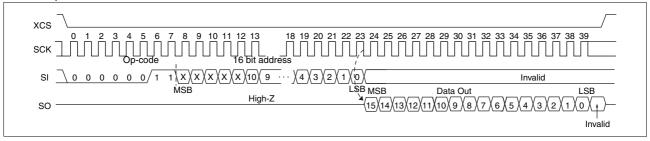

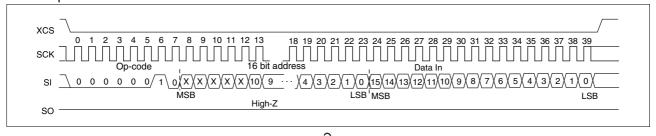

#### (1) READ

The READ command is executed in units of 16 bits (1 word).

The memory addressing is described as table "■ MEMORY 2. Memory map • Memory map". The sequence of READ command is shown in the figure below.

Op-code and 16 bits address are input through SI. synchronously to the rising edge of SCK.

The upper 5 address bits don't care. Then, the data is read through SO synchronously to the falling edge of SCK.

During the data is read, the SI value is invalid. The reading address is automatically incremented by each 16-cycle clock input until XCS is rising. If the most significant address is reached, the counter rolls over to "0000H".

The rising edge of XCS terminate the READ operation.

The READ command can be executed in the User memory, TID, EPC, and Lock status areas. If the specified areas are in Read Locked, "0000<sub>H</sub>" is output instead of the data. If this LSI is in Kill status, the READ command is ignored.

· Sequence of READ command.

#### (2) WRITE

The WRITE command is executed in units of 16 bits (1 word). The memory addressing is described as table ■ MEMORY 2. Memory map • Memory map".

The sequence of WRITE command is shown in the figure below.

Op-code, 16 bits address and 16 bits of writing data are input through SI synchronously to the rising edge of SCK.

The upper 5 address bits don't care. The writing address is automatically incremented by the following 16 bits data input until XCS is rising. If the most significant address is reached, the counter rolls over to "0000H". The rising edge of XCS terminate the write operation.

The WRITE command can be executed in the User memory areas. It writes error information to the SPI Error Information Register. (The error code is described in "**ECOMMAND 4**. Error of Serial communication mode") If this LSI is in Kill status, the WRITE command is ignored.

Sequence of WRITE command

#### 4. Error of Serial Communication Mode

In Serial communication mode, if the LSI encounters an error when executing a READ/WRITE command, the error codes will be stored in the SPI Error Information Register.

When reading error occurred, "0000H" is output instead of the data. When writing error occurred.

#### • SPI Error Information Register

The following table shows the format of error information that stored in the SPI Error Information Register (SPI\_ERR\_Info:address = 8000H, see table "■ MEMORY 2. Memory map • Memory map"). The information can be read by the READ command. If the start bit of addresses for the following command is "0", the error information register will be cleared after an error occurs.

#### • SPI Error Information Register format

| Bit      | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0 |

|----------|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|-----|---|

| Function | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 |   | ERR | OR* |   |

#### \*: ERROR

b1000 : Low voltage detection

b0100 : Write NG b0010 : Read NG

b0001 : NG because RF occurred b0000 : Finished successfully

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. Absolute Maximum Rating

| Parameter                | Symbol   |              | Rating |                       | Unit  | Remarks                                 |

|--------------------------|----------|--------------|--------|-----------------------|-------|-----------------------------------------|

| raiailletei              | Syllibol | Min          | Тур    | Max                   | Ollit | nemarks                                 |

| Maximum input voltage    | Vmax     | _            | _      | 3.0                   | V     | Between PWRP-PWRM                       |

| Power supply voltage     | $V_{DD}$ | - 0.5        | _      | + 4.0                 | V     |                                         |

| Input voltage            | Vin      | - 0.5        | _      | V <sub>DD</sub> + 0.5 | V     |                                         |

| Output voltage           | Vout     | - 0.5        | _      | V <sub>DD</sub> + 0.5 | V     |                                         |

| ESD voltage immunity     | VESD     | - 2          | _      | + 2                   | kV    | Human Body Model                        |

| LSD voltage illillurilly | VESD     | <b>– 100</b> | _      | + 100                 | V     | Machine Model                           |

| Storage temperature      | Tstg     | - 40         | _      | + 85                  | °C    | Excluding FRAM data retention guarantee |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### 2. Recommended Operation Conditions

| D                              | arameter                         | Symbol          |                       | Value |                | Unit | Remarks                                   |

|--------------------------------|----------------------------------|-----------------|-----------------------|-------|----------------|------|-------------------------------------------|

| F                              | arameter                         | Symbol          | Min                   | Тур   | Max            | Oill | nemarks                                   |

| Operating junction temperature | on                               | Tj              | -20                   | _     | +85            | °C   |                                           |

| Retention guaral temperature   | ntee                             | Trtn1           | -20                   | _     | +55            | °C   | Retention<br>guarantee period:<br>10years |

|                                | Antenna input frequency          | Fclk            | 860                   | _     | 960            | MHz  | According to the Radio Law                |

|                                | Reception modulation depth       | (A-B)/A         | 80                    | 90    | 100            | %    |                                           |

| RF                             | Receiving bit rate               | F_fwd           | 26.7                  |       | 128            | kbps | PIE code: mark rate = 1/2                 |

| communication                  | Receiving waveform rise time     | Tr              | 1                     | _     | 500            | μs   |                                           |

|                                | Receiving waveform settling time | Ts              | _                     | _     | 1500           | μs   |                                           |

|                                | Receiving waveform fall time     | Tf              | 1                     | _     | 500            | μs   |                                           |

| 0. (1)                         | Power supply voltage             | V <sub>DD</sub> | 2.3                   | 3.3   | 3.6            | V    |                                           |

| Serial communication           | "H" level input voltage          | VıH             | $V_{\text{DD}} - 0.2$ |       | $V_{DD} + 0.3$ | V    |                                           |

|                                | "L"level input voltage           | VIL             | - 0.3                 | _     | + 0.4          | V    |                                           |

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

#### 3. RF Communication Characteristics

| Par                                  | ameter                       | Symbol             |     | Value |      | Unit | Conditionas/Remarks                                                |

|--------------------------------------|------------------------------|--------------------|-----|-------|------|------|--------------------------------------------------------------------|

| Fai                                  | ameter                       | Symbol             | Min | Тур   | Max  |      | Conditionas/nemarks                                                |

| Minimum oper when reading            | ating power                  | P <sub>R_MIN</sub> |     | -6    | _    | dBm  | Measured for TSSOP16 PKG<br>Tari=25us, RTcal=3Tari,TRcal=2.6RTcal, |

| Minimum operating power when writing |                              | Pw_MIN             | _   | -6    | _    | dBm  | DR=8,FM0,BLF=41kbps,<br>DSB-ASK, Modulation depth=90%*             |

| Maximum operating power              |                              | Рмах               |     | 18    |      | dBm  |                                                                    |

| MB97R803A                            | Equivalent input capacitance | СР                 |     | 0.47  | _    | pF   | Input power = -6dBm,<br>paralel model (At 953MHz)                  |

| (Wafer)                              | Equivalent input resistance  | R₽                 | _   | 2     |      | ΚΩ   | Input power = -6dBm,<br>paralel model (At 953MHz)                  |

| MB97R804B                            | Equivalent input capacitance | СР                 | _   | 0.69  |      | pF   | Input power = -6dBm,<br>paralel model (At 953MHz)                  |

| (TSSOP)                              | Equivalent input resistance  | R₽                 | _   | 1.7   | _    | ΚΩ   | Input power = -6dBm,<br>paralel model (At 953MHz)                  |

| Returning bit rate                   |                              | F_rtrn             | 40  |       | 640  | kbps |                                                                    |

| Error of returning bit rate          |                              | Ftolerance         | ± 5 |       | ± 22 | %    |                                                                    |

| Bit rate change during returning     |                              | Fvariation         | -21 |       | 14   | %    | This is different from the value defined in EPC standards.         |

<sup>\*:</sup> These characteristics are the values for the standalone LSI, and do not specify the values when the LSI is connected to other circuits such as a microcomputer.

#### 4. Serial Communication DC Characteristics

| Parameter                    |                      | Symbol           | Value                 |      |                 | l lasia | Domoules                                                                         |  |

|------------------------------|----------------------|------------------|-----------------------|------|-----------------|---------|----------------------------------------------------------------------------------|--|

|                              |                      |                  | Min                   | Тур  | Max             | Unit    | Remarks                                                                          |  |

| Input leakage current        |                      | lμ               | _                     | _    | ± 5             | μΑ      | $V_{IN} = 0V \text{ to } V_{DD}$                                                 |  |

| Output leakage current       |                      | ILO              |                       | _    | ± 5             | μА      | $V_{\text{OUT}} = 0V \text{ to } V_{\text{DD}}, \text{ when output pin is Hi-Z}$ |  |

| Power supply                 | Operating current    | Icc              | _                     | 70   | 200             | μΑ      | SCK = 2MHz, Vdd=3.0V                                                             |  |

|                              | Power down current 1 | l <sub>PD1</sub> |                       | 0.01 | 5               | μА      | SPI = 0V or open<br>XCS, XWP, SCK, SI = 0V or VDD<br>No RF reception             |  |

|                              | Power down current 2 | IPD2             | _                     | 3    | 5               | uA      | SPI = 0V or open<br>XCS, XWP, SCK, SI = 0V or V <sub>DD</sub><br>RF receiving    |  |

|                              | Standby current      | IsB              |                       | 10   | 50              | μА      | SPI = VDD<br>XCS, XWP, SCK, SI = 0V or VDD                                       |  |

| Output voltage at "H" level  |                      | Vон              | V <sub>DD</sub> × 0.8 | _    | V <sub>DD</sub> | ٧       | I <sub>OH</sub> = -1mA                                                           |  |

| Output voltage at "L" level  |                      | Vol              | 0                     |      | 0.4             | V       | IoL = 2mA                                                                        |  |

| SPI pin pull-down resistance |                      | Rin              | 0.8                   | 1    | 1.2             | МΩ      | $V_{IN} = V_{DD}$                                                                |  |

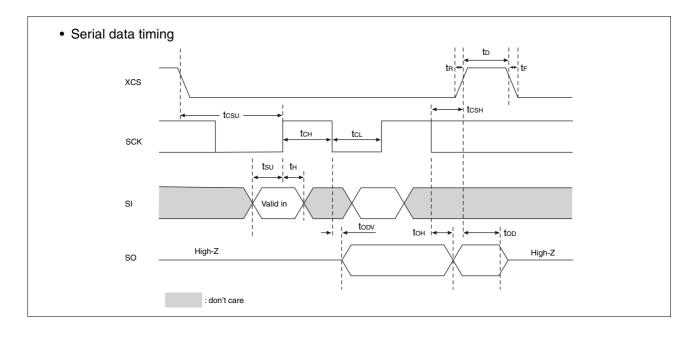

#### 5. Serial Communication AC Characteristics

| Parameter              | Cymbol          | Va  | Unit |      |

|------------------------|-----------------|-----|------|------|

| Farameter              | Symbol          | Min | Max  | Unit |

| SCK clock frequency    | fск             | _   | 2    | MHz  |

| Clock high time        | tсн             | 200 | _    | ns   |

| Clock low time         | t <sub>CL</sub> | 30  | _    | ns   |

| Chip select set time   | <b>t</b> csu    | 10  | _    | ns   |

| Chip select hold time  | <b>t</b> csH    | 10  | _    | ns   |

| Output disable time    | <b>t</b> od     | _   | 20   | ns   |

| Output data valid time | todv            | _   | 35   | ns   |

| Output hold time       | tон             | 0   | _    | ns   |

| Deselect time          | to              | 200 | _    | ns   |

| Data rise time         | t <sub>R</sub>  | _   | 50   | ns   |

| Data fall time         | t⊧              | _   | 50   | ns   |

| Data set up time       | <b>t</b> su     | 10  | _    | ns   |

| Data hold time         | tн              | 10  | _    | ns   |

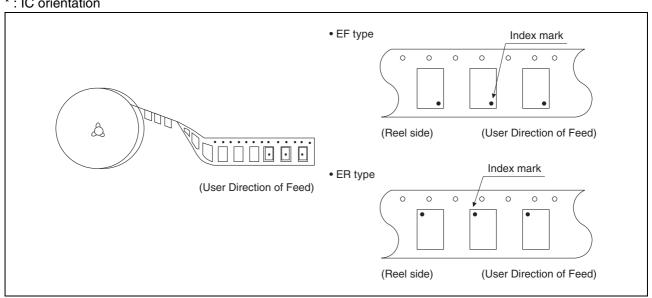

#### **■ ORDERING INFORMATION**

| Part number           | Interface | Shipping method         | Wafer thickness  | Remarks  |

|-----------------------|-----------|-------------------------|------------------|----------|

| MB97R803A-DIAP15      | RF        | Wafer<br>(After dicing) | 150 μm ± 25.4 μm |          |

| MB97R804BPFT-G-JNEFE1 | RF + SPI  | TSSOP16                 |                  | EF type* |

| MB97R804BPFT-G-JNERE1 | 111 + 3F1 | (Tape & Reel)           |                  | ER type* |

#### \*: IC orientation

#### **■ PACKAGE DIMENSION**

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

26

### **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

#### North and South America

FUJITSU SEMICONDUCTOR AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://us.fujitsu.com/micro/

#### **Europe**

FUJITSU SEMICONDUCTOR EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/semiconductor/

#### Korea

FUJITSU SEMICONDUCTOR KOREA LTD. 902 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fsk/

#### **Asia Pacific**

FUJITSU SEMICONDUCTOR ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://sg.fujitsu.com/semiconductor/

FUJITSU SEMICONDUCTOR SHANGHAI CO., LTD. 30F, Kerry Parkside, 1155 Fang Dian Road, Pudong District, Shanghai 201204, China

Tel: +86-21-6146-3688 Fax: +86-21-6146-3660

http://cn.fujitsu.com/fss/

FUJITSU SEMICONDUCTOR PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: +852-2377-0226 Fax: +852-2376-3269 http://cn.fujitsu.com/fsp/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department