## SPARC64<sup>™</sup> XII: Fujitsu's latest 12 Core Processor for Mission Critical Servers

April 20, 2017

Takumi Maruyama

Advanced System Research & Development Unit Fujitsu Limited

All Rights Reserved, Copyright© FUJITSU LIMITED 2017

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

Chip overview

Micro Architecture

System Architecture

Performance

# Fujitsu Processor development

## **Perpetual evolution**

SPARC M12 SPARC64 XIfx server HPC Virtual Machine Architecture UNIX SPARC Software on Chip XII 40nm **High-speed Interconnect** SPARC6 SPARC64 IXfx **HPC-ACE** 45nm System on Chip SPARC64 Fujitsu M10 SPARC6 VIIIfx **Hardware Barrier** server 65nm Multi-core Multi-thread SPARC6 **GS21** L2\$ on Die VTT 90nm 2600 SPARC64 **Non-Blocking \$** SPARC64 130nm **GS21 O-O-O Execution** 28nm 1600 SPARC64 Super-Scalar 180nm GS21 900 Mainframe Single-chip CPU 250nm / **GS21 Store Ahead** 220nm 600 Branch Histor 350nm GS8900 GS8800<sup>7588008</sup> Prefetch SPARC6 : Technology generation GP \$ ECC SPARC64 GS8600 **Register/ALU** Parity Mainframe/UNIX/HPC SPARC64 Instruction Retry II SPARCE incremental development \$ Dynamic Degradation Error Checkers/History 2004~2007 2008~2011 2012~2015 2016~ 2000~2003

### SPARC64<sup>™</sup> XII

20nm

Fujitsu

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

<u>Design concept</u>

Chip overview

Micro Architecture

System Architecture

Performance

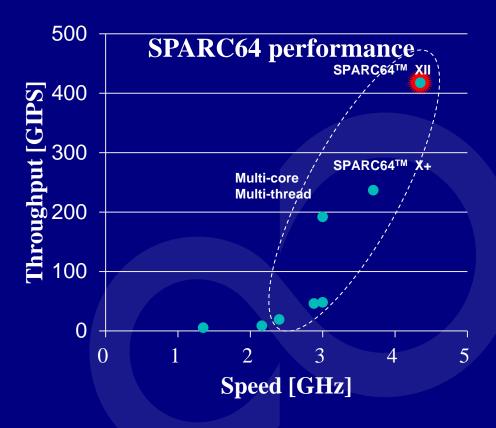

# SPARC64<sup>™</sup> XII Design Concept High Performance: SPEED and THROUGHPUT

## High SPEED (Single thread performance)

- High CPU frequency

- State of the art O-O-O

- Rich execution units

## High THROUGHPUT

Many cores, threadsStrong Cache and Memory

Robust RAS

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

<u>Chip overview</u>

Micro Architecture

System Architecture

Performance

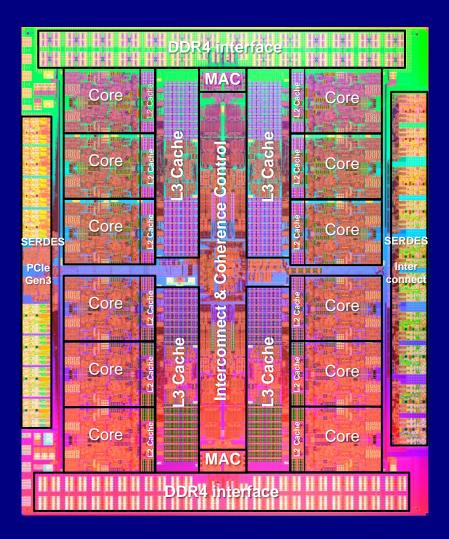

# **SPARC64™ XII Chip Overview**

SPARC64<sup>™</sup> XII

### Architecture Features

- 12 cores x 8 threads

- SWoC (Software on Chip)

- 32MB L3 cache

- Embedded Memory and IO Controller (PCIe GEN3)

## • 20nm CMOS

- 25.8mm x 30.8mm

- 5,450M transistors

- 1,860 signal pins

- 4.25GHz (up to 4.35GHz with High Speed Mode enabled)

- Performance (peak)

- 417GIPS / 835GFlops

- 153GB/s memory throughput

# **SPARC64™ XII Core spec**

| Instruction Set<br>Architecture | SPARC-V9/JPS<br>HPC-ACE<br>VM / SWoC                                                    |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| Integer                         | (156 GPR x 4 + 96 GUB) x 2pipe                                                          |  |  |  |  |  |

| Execution Units                 | (ALU/SHIFT x2) x 2pipe<br>(ALU/AGEN x2) x 2pipe<br>(MULT/DIVIDE x1) x 2pipe             |  |  |  |  |  |

| FP                              | (128 FPR x 4 + 64 FUB) x 2pipe                                                          |  |  |  |  |  |

| Execution Units                 | (FMA x4 / FDIV x2) x 2pipe<br>(IMA/Logic x4) x2pipe<br>(Decimal x1 / Cypher x2) x 2pipe |  |  |  |  |  |

| L1\$                            | L1I\$ 64KB/4way<br>L1D\$ 32KB/4way x 2pipe                                              |  |  |  |  |  |

| L2\$                            | 512KB/16way                                                                             |  |  |  |  |  |

Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

Chip overview

Micro Architecture

System Architecture

Performance

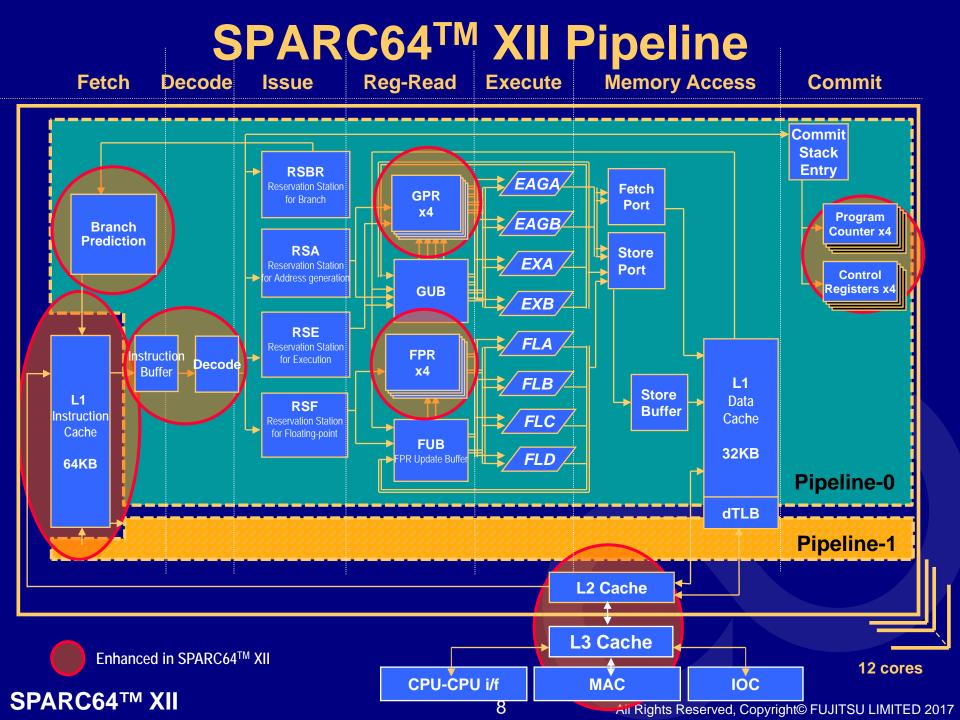

# Common Micro-Architecture features between SPARC64<sup>™</sup> X+ and XII

### Processor Core

- Fetch 8 instructions, Decode 4 instructions, Execute 6 instructions per instruction pipeline

- Aggressive O-O-O execution, including memory access (load and store)

- High single thread performance

- SWoC (Software on Chip) Accelerates specific software function by hardware

- Outside the Core

- Embedded Memory and IO Controller (PCIe GEN3)

- Robust RAS (Reliability, Availability, Serviceability) ★

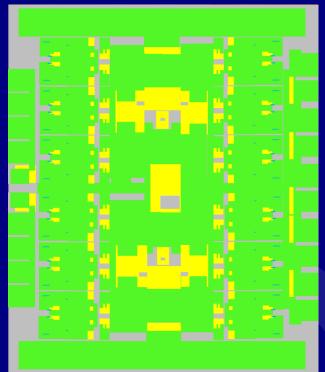

# Reliability, Availability, Serviceability

| Units                     | Error detection and correction scheme |

|---------------------------|---------------------------------------|

| Cache (Tag)               | ECC<br>Duplicate & Parity             |

| Cache (Data)              | ECC<br>Parity                         |

| Register                  | ECC (INT/FP)<br>Parity(Others)        |

| Execution Unit            | Parity/Residue                        |

| Cache dynamic degradation | Yes                                   |

| HW Instruction Retry      | Yes                                   |

| History                   | Yes                                   |

→ Guarantees Data Integrity (Number of checkers increased to ~66,000)

### SPARC64<sup>™</sup> XII RAS diagram

Green: 1bit error Correctable Yellow: 1bit error Detectable Gray: 1bit error harmless

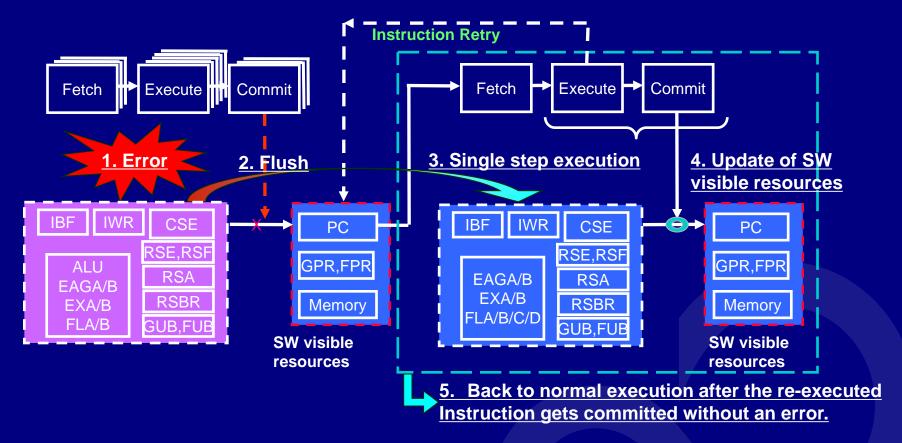

# **Hardware Instruction Retry**

When an error is detected, Hardware re-execute the instruction automatically to remove the transient error by itself.

# Enhanced Micro-Architecture from SPARC64<sup>™</sup> X+

### Processor Core

Dual instruction pipelines sharing L1 I-cache, and 8-way SMT (4-way SMT per instruction pipeline) ★

- Better Branch Prediction Scheme

- Various Queue-size increase

- Deeper pipeline to increase Frequency

- High Speed Mode

### Outside the core

3 level hierarchy cache, and 4 LCU (Last level cache and Core Unit) structure ★

DDR4-2400 memory

Doubled PCIe GEN3 ports (8 lane x 4)

# **Micro-architecture enhancements 1/2**

## Increase core throughput, keep single thread performance

Dual instruction pipelines per core

Each pipeline has its own resources except

### Sharing L1 I-Cache and TLB between the two pipelines

- Especially effective in DB apps

- 4-way SMT instruction pipeline

- More throughput compared with the previous 2-way SMT

- Resources are dynamically shared between the threads.

### **Core Resource allocation**

| #Active threads | L1 I\$ | IB       | Rsv.<br>Station | Rename<br>Registers | Execution<br>Units | FP/SP<br>Port | L1 D\$ | CSE      |

|-----------------|--------|----------|-----------------|---------------------|--------------------|---------------|--------|----------|

| 1               | 100%   | 50%      | 50%             | 50%                 | 50%                | 50%           | 50%    | 50%      |

| 2               | 100%   | 50% x2   | 50% x2          | 50% x2              | 100%               | 50% x2        | 100%   | 50% x2   |

| 4               | 100%   | 25% x4   | 25% x4          | 25% x4              | 100%               | 25% x4        | 100%   | 25% x4   |

| 8               | 100%   | 12.5% x8 | 50% x2          | 12.5% x8            | 100%               | 12.5% x8      | 100%   | 12.5% x8 |

### SPARC64<sup>™</sup> XII

#### All Rights Reserved, Copyright© FUJITSU LIMITED 2017

# **Micro-architecture enhancements 2/2**

### 3 level cache and 4 LCU structure to realize Low Latency and High throughput

L2 cache latency < L3 cache latency x 0.5</li>

L2 cache to Core : 32 Bytes x 2 pipelines

L3 cache to Core : 32 Bytes x 3 cores

## MEZASI

Fujitsu's unique cache protocol for LCU

- ELC (Extra Level Cache)

- Unused L3 cache blocks act as Victim Cache

- IO-DCA (IO Direct Cache Access)

- Direct DMA write to L3 cache from IO device

- Speculative memory access

- Memory access in parallel with other L3 cache blocks access

### 16B 32B PIPE0 PIPE1 L1I L1D L1D L2 cache 3 cores L3 cache block 4 LCUs Inter L3 cache block **Coherence Control** CPU-CPU i/ MAC IOC

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

Chip overview

Micro Architecture

System Architecture

Performance

# **Fujitsu SPARC M12 server**

### ◆ Fujitsu's latest UNIX server with SPARC64<sup>™</sup> XII.

- M12-2: mid-range server

- M12-2S: scalable high-end server

# **SPARC M12 System Architecture**

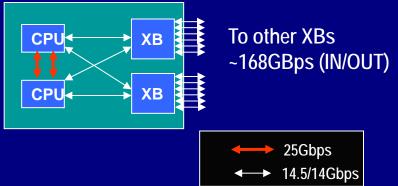

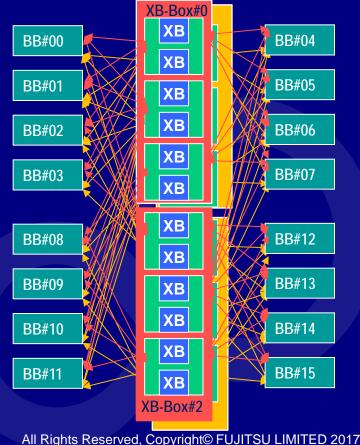

- $\diamond$  Scales from 1 to 32 CPU sockets (2,048 $\rightarrow$ 3,072 threads)

- Directory-based cache coherency

- High-speed interconnect, up to 25 Gbps per lane in SPARC64<sup>™</sup> XII

## System Configuration

- Building Block (BB) is 2 CPUs and 2 XBs

- Up to 4 BBs can be connected by XBs

- 16 BBs can be connected via XB-Boxes

- BB topology inherits current M10-4S with SPARC64<sup>™</sup> X+

### Building Block (2 CPU Sockets)

### SPARC64<sup>™</sup> XII

### 16 BBs (32 CPU Sockets)

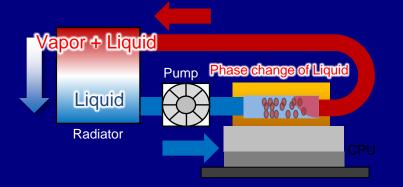

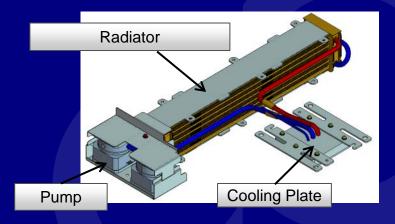

# **SPARC M12 System Cooling**

VLLC (Vapor and Liquid Loop Cooling) Newly developed cooling mechanism for SPARC M12.

Evaporative cooling, taking heat away when liquid changes to vapor

The pumps circulate coolant in the VLLC system

The radiator dissipates the heat absorbed by the cooling plate into the air.

→ Achieves 2x cooling performance of the current LLC

### SPARC64<sup>™</sup> XII

#### All Rights Reserved, Copyright© FUJITSU LIMITED 2017

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

Chip overview

Micro Architecture

System Architecture

Performance

# **SPARC64<sup>TM</sup> XII benchmark numbers**

|                              |                 | 1CPU                       | 2CPU                       | 16CPU      |

|------------------------------|-----------------|----------------------------|----------------------------|------------|

| SPECint®_rate2006            |                 | 956                        | 1,910                      | 14,500     |

| SPECjbb®2015<br>Composite    | Max<br>Critical | 52,659 jOPS<br>34,771 jOPS | 98,333 jOPS<br>63,354 jOPS | n/a<br>n/a |

| SPECjbb®2015<br>Multiple-JVM | Max<br>Critical | 54,434 jOPS<br>34,771 jOPS | n/a<br>n/a                 | n/a<br>n/a |

| STREAMtriad                  |                 | 127GB/s                    | n/a                        | 1,533GB/s  |

Source except STREAMtriad : www.spec.org

Fujitsu SPARC M12-2S: SPARC64 XII (4.25GHz, up to 4.35GHz) x 1,2,16CPU OS : Oracle Solaris 11.3 Compiler: Oracle Developer Studio 12.6 JVM : HotSpot<sup>™</sup> 64-Bit Server VM, version 1.8.0\_121

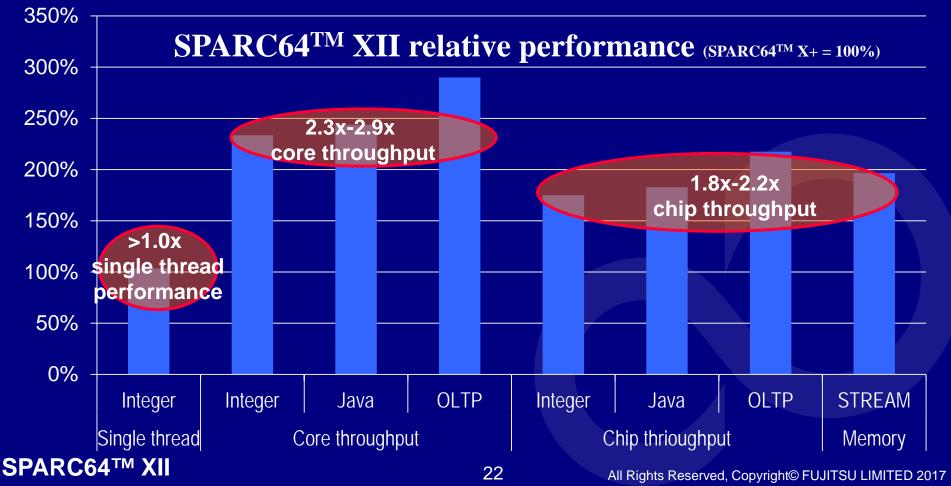

# **SPARC64<sup>TM</sup> XII** Performance

• 2x chip throughput and 2.5x core throughput

compared to previous SPARC64<sup>™</sup> XII, keeping single thread performance

### Keys: 8way SMT design, Higher CPU frequency, and microarchitecture improvement

## Fujitsu Processor Development History

SPARC64<sup>TM</sup> XII

Design concept

Chip overview

Micro Architecture

System Architecture

Performance

# Summary

◆ SPARC64<sup>™</sup> XII is Fujitsu's 12<sup>th</sup> SPARC processor which has been designed to be used for Fujitsu's latest UNIX server.

The processor enhancements are to increase throughput, while keeping its high single thread performance and its robust RAS features

◆ SPARC64<sup>™</sup> XII measured results have shown 2x chip throughput of SPARC64<sup>™</sup> X+

◆ Fujitsu will continue to develop SPARC64<sup>™</sup> series to meet the needs of a new era.