# **SPARC® Enterprise**

T5120/T5220/T5140/T5240

サーバ・アーキテクチャ

マルチスレッド・テクノロジー搭載

UltraSPARC® T2/UltraSPARC T2 Plus プロセッサの威力

White Paper

2008 年 4 月

## 目次

### 全体概要 3

### 第1章 マルチスレッド・テクノロジの進化 4

WEB2.0 のビジネス・チャレンジ 4 マルチスレッド・テクノロジの革新 5 SPARC ENTERPRISE T5120 / T5220 / T5140 / T5240 9

# 第2章 革新的なマルチスレッド・テクノロジを搭載した、 ULTRASPARC T2/ULTRASPARC T2 PLUS プロセッサ 15

ULTRASPARC T2/ULTRASPARC T2 PLUS: 世界初の大量スレッド処理SoC 15次世代へ進化したマルチスレッド設計 17

ULTRASPARC T2/ULTRASPARC T2 PLUS プロセッサのアーキテクチャ 19

## 第3章 サーバ・アーキテクチャ 26

システムレベルのアーキテクチャ 26 SPARC ENTERPRISE T5120 の概要 31 SPARC ENTERPRISE T5220 の概要 33 SPARC ENTERPRISE T5140 の概要 35 SPARC ENTERPRISE T5240 の概要 37

### 第4章 エンタープライズ・クラスの管理とソフトウェア 40

システム管理テクノロジ 40 サーバ管理ソフトウェア 41 マルチスレッド・テクノロジのスケーラビリティとサポート 42 エンド・ツー・エンドの仮想化テクノロジ 44 障害管理と予測的セルフヒーリング 47

### 第5章 まとめ 49

詳細情報 50

# 全体概要

Webの活用は、新たな機器の普及や、Web2.0のアプリケーション、さらにグローバルで毎日インターネットを活用するユーザにより根本的に変化しています。また、アプリケーションやサービスの性質も変化しています。ユーザは、特にインストールすることなく、アップグレード、ライセンス取得、承認行為、そして購入する時でさえ、処理作業が不要な状況になってきています。Webを介してユーザ同士が直接やり取りし、内容の変更や改善が可能となります。情報は共有され、多くの人気サービスは無料で使用できます。非常に小規模の取引でさえも活性化し、規模拡大を目指しています。ソーシャル・ネットワーキング・サービス等の共同サイトが世界中の同じ考えを持つ人々同士に情報や膨大な範囲の話題・問題を共有できるようにしました。ビジネスのやりとりも圧倒的にWebベースになっています。

この進化しつづける領域で生き残ることは、データセンターにとって非常に大きな挑 戦になっています。小規模で開始し、迅速に拡大できるサービスが必要とされていま す。数ヶ月で容量が倍増するものもあるためです。インフラについても、この大規模 なスケーラビリティへの要求を、管理負荷を増加させることなく実現させなければな りません。しかし、大半のデータセンターは面積や電力にかなりの制約を受けており、 さらにエネルギー消費コストも増加しています。データセンターがエネルギー消費や 汚染を減らす役割への新たな評価もあります。企業は無駄なインフラを統合し、管理 を簡易化して、現在使用しているシステムを有効活用するため、仮想化はかなり重要 なツールとなっています。データの消失やデータ破壊によるコスト増大から、セキュ リティに関しても、かつてこれほど重要視されたことはありません。これらの問題解 決のために企業自身が欠点や限界のあるインフラを独自に構築することは困難です。 業界初のシステム・オン・チップ(SoC)を採用した UltraSPARC T2/UltraSPARC T2 Plus プロセッサや、SPARC Enterprise T5120/T5220/T5140/T5240 を使用することで、Web2.0 インフラを構築し、データセンターで発生する問題を解決するようなパフォーマンス やエネルギー効率を実現できます。次世代のマルチスレッド・テクノロジは、最大 64 スレッドをわずか1RU(ラック・ユニット)でサポートし、様々な制約を受けた電力 や冷却機能の中で、高密度なコンピュータを提供しています。高度な統合により、待 ち時間、ホット・スポットを削減し、セキュリティや信頼性を改善しています。バラ ンスのとれたシステム設計は広範囲にわたるアプリケーションをサポートしていま す。管理インタフェースを統一し、業界標準を採用したことで、管理コストが削減さ れ、また SPARC Enterprise T1000/T2000 の革新的な筐体デザインを共有することによ り、データセンターに省スペース化、効率化、TCO 削減を提供します。オープンソー スのライセンス供与のもと、プロセッサと Solaris OS の双方が使用可能な状態であれ ば、企業は自由に新たな技術を取り入れ、世界規模の技術コミュニティとして活動で きます。

# 第1章 マルチスレッド・テクノロジの進化

マルチスレッド・テクノロジを用いたUltraSPARC T1 プロセッサをベースにした SPARC Enterprise T1000/T2000 は非常に高い賞賛を得ています。最大 5 倍のスループットを 1/4 のスペースと電力で達成し、これらの製品は電力会社\*1から初のリベートを獲得することとなり、この流れが今も世界中で行われています。現在、マルチスレッド・テクノロジは、Webや他のアプリケーションなど多岐にわたり常時変化する要求に応えるべく進化し続けています。

\*1 2006年8月, Pacific Gas and Electric (PG&E)社 は、SPARC Enterprise T1000 /T2000への買い替えに伴い電力を払い戻すサービスを開始

# Web2.0 のビジネス・チャレンジ

WebサービスやSOA(サービス指向型アーキテクチャ)の普及で明らかなように、充実した新しいコンテンツや高帯域サービスを以前よりも大勢のユーザに提供できることが期待されています。多くの業界にまたがる企業はより多くの市場開拓に取り組み、コストを削減し、彼ら自身の顧客をより正確に調査できることを期待しています。それと同時に、広帯域な有線・無線のクライアント機器により、何百万もの人々がネットワーク・コンピューティングへ日々アクセスしています。このような流れから、データセンターのスケーラビリティや必要容量が見直され、それと同時に、根本的な面積、電力、冷却能力による課題に直面しています。

### • Webシステムにおけるスケールアップ型の拡張

Webアプリケーションはインフラの配置に新たなペースや必要性を生み出しています。企業は、開発時間やサービス開始までの時間を短縮しなくてはならない一方で、冗長性のある高品質で高性能なアプリケーションやサービスを提供しなければなりません。企業の多くは迅速にスケール変更をできるような余力を持ち、小規模からスタートしなければなりません。というのも、新たな顧客や革新的なWebサービスには数ヶ月で容量が倍増してしまうものもあるからです。

同時に、企業は現在のデータセンターで利用可能な電力、冷却、スペース中で、環境 負荷を低減しなければなりません。運用コストがIT予算の最大40%を占める中で、シ ステム管理コストについても見直しが必要となっています。簡易化とスピードが最重 要事項であり、これが、ダイナミックに景気に反応する能力与えます。企業はまた、 ベンダーのロックイン状態を無くすことを目指しています。それは企業が過去、現在、 そして将来の投資を守ろうと考えているためです。オープン・スタンダードで構築さ れたオープンプラットフォームは、参入/退出コストを削減すると同時に、最大限の 柔軟性を提供する手助けとなります。

### • データセンター運用における仮想化と環境効率化の推進

多くのデータセンターは、サービスの規模と共に、業務的および技術的な処理を並行 して行なうため、標準プラットフォームの配置を少なくすることに重点を置いていま す。このプロセスには、使用中の広範囲にわたるサーバ・インフラを、ビジネスの俊 敏性を高め、災害復旧を改良し、運用コストを削減するための効果的な仮想化ソ リューションとの統合が含まれます。このように着目すると、データセンターが消費 する電力のワットあたりのパフォーマンス量を改善することで、エネルギー削減や、 データセンターの容量制限の解決を促進することができるのです。

環境効率は具体的なメリットをもたらします。二酸化炭素排出量を削減することでエコロジー改善となり、法的な面で企業の社会的責任を達成し、企業が支払う電気代も改善します。システムはより密度の高く能力のあるコンピューティング・インフラに統合されるので、データセンター用面積の需要が少なくなります。注意深く計画を進めると、この方法は過度の熱負荷が原因のハードウェア障害を削減することとなり、サービスの使用可能時間や信頼性を改善することができます。高レベルの標準RAS(信頼性・可用性・保守性)を装備したサーバは非常に需要があると考えられます。

### • *企業におけるスピードと安全性*:

企業は顧客やパートナーとの全てのコミュニケーションを保護することに対して非常に関心があります。リスクに応じて、エンド・ツー・エンドの暗号化がセキュリティや、守秘義務による信用への高まりから必要となっています。暗号はまた、ストレージにとっても重要であり、保存・蓄積されたデータの安全を守り、改ざんやデータの不整合を検出するメカニズムを作り出しています。

しかし、増加する暗号化の費用は、コンピュータのリソースへの負担増となります。 セキュリティもまた、顧客の経験や低速度のトランザクションに対しボトルネックを 与えないような回線速度が必要となります。パフォーマンスへの影響やコストの増加 が無く、クライアントのセキュリティやプライバシーを確保するのに役立ち、企業に はコンプライアンスに役立つものがソリューションとして提供されなければなりま せん。

# マルチスレッド・テクノロジの革新

既存のプロセッサやシステムの機能を追い抜くためには、新しいアプローチが必要で した。

### ムーアの法則とこれまでのプロセッサ設計の収益逓減

たびたび引用されるムーアの法則では、最小部品コストに関連する集積回路におけるトランジスタの集積密度は、18~24ヶ月ごとに倍になると述べられています。ムーアの法則が提唱されてから30年以上経ち、プロセッサのパフォーマンスは新たな段階に向かっています。プロセッサの設計者は、目標である命令レベルの並列性(instruction-level parallelism: ILP)と共に、複雑なプロセッサを構築するためにチップ面積を利用しました。現在、この従来のプロセッサは、シングル・インストラクション・パイプラインを高速化するため、様々な高度な方式で、非常に高い周波数を実現しています。

- 大容量キャッシュ

- スーパースカラー設計

- アウト・オブ・オーダー

- 超高速クロック周波数

- パイプライン

- 投機実行、プリフェッチ

これらの技術は、重要なマルチギガヘルツの周波数を持った高速プロセッサを誕生させた一方で、複雑でパワー重視のプロセッサを生み出す結果となり、現在のデータセンターで見られるようなタイプの業務に適してはいません。実際、多くのデータセンターの業務は、これらのプロセッサに提供され苦労して得たILPを活用することができていません。高度に共有化されたメモリや高度な同時ユーザ、計算業務などのアプリケーションは、単一スレッドでの処理(ILP)よりも一般的に多数の同時スレッド処理(thread-level parallelism, TLP)に集中しています。

事態をますます悪化させているのは、既存のアプリケーションにあるILPのほとんどがすでに抽出され、メリットが少なくなっていることです。さらに、マイクロプロセッサの周波数スケーリングは、マイクロプロセッサの電力問題のために横ばい状態です。より高速なクロックで、一連のプロセッサの生成は、以前より一層パワーのあるものが要求されているようであり、実際は、マイクロプロセッサの周波数スケーリングは、2-3GHz内で横ばい状態です。パイプラインのスーパースカラー・プロセッサを配置することはより能力が必要であり、プロセッサを冷却する根本的な機能によってこの方法を制限しています。

# マルチコア・プロセッサにおけるマルチプロセッシング

これらの問題を解決するために、マルチプロセッサ業界の大半はムーアの法則で提供されたトランジスタを使用して、単一の物理的なダイ上に2もしくは4つの標準的なプロセッサ・コアをグループ分けし、マルチコア・プロセッサ(もしくはマルチスレッド・プロセッサ、CMP)を設計してきました。多くのマルチスレッド設計で作り出された個別のプロセッサ・コアには、以前の単一プロセッサ・チップほどのパフォーマンスは認められず、事実、単一コア・プロセッサより単一スレッド・アプリケーションの方がより遅いと認識されていました。しかし、複数のプログラム(または、複数のスレッド)が並列に処理(スレッドレベルでの並列処理)出来るため、チップ全体として性能は向上しています。

残念ながら、大半の現在使用可能な(もしくはまもなく使用可能になる予定の)チップ・マルチプロセッサは既存の(シングル・スレッド)プロセッサ設計からコアを単純に複製しています。これでは、総パフォーマンスの中でわずかな改善しか得られません。それは、メモリ速度やハードウェア・スレッド・コンテクスト・スイッチングといったキー・パフォーマンス問題については着手できていないためです。その結果、これらの設計がいくつかの付加的なスループットやスケーラビリティを生み出す一方で、相当量の電力を消費し、著しい熱を発生させ、全体のパフォーマンスで釣り合いのとれた高速化にはならないのです。

# 最先端マルチスレッド・テクノロジ

我々は、早くからプロセッサ速度とメモリ・アクセス速度の間の不均衡を認識していました。プロセッサ速度が2年ごとに2倍なっていくのに対して、メモリのアクセス性能は6年ごとにしか倍増しません。その結果、メモリ待ち時間がアプリケーションのパフォーマンスにおいて大きな影響力を持ち、クロック速度におけるメリットを大きく消失しています。この大きな不釣合いは、メモリがアクセス性能ではなく、密度やコストを重視した結果です。

残念ながら、プロセッサとメモリ速度の間に関連したギャップは超高速プロセッサに85%のアイドル状態の時間を残し、メモリ処理の完了を待つことになります。皮肉なことに、従来のプロセッサの実行パイプラインはより早くより複雑になるにつれ、メモリ待ち時間の影響は大きくなります。更に悪いことに、アイドル状態のプロセッサは電力が必要であり、熱を発生させます。周波数(ギガヘルツ)が実際のパフォーマンスには追従できていないのが現状です。

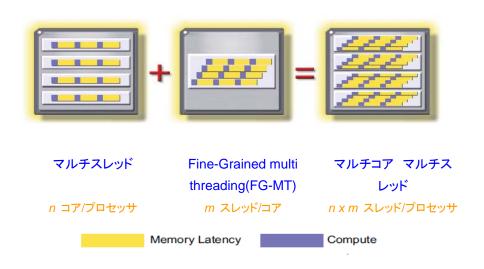

マルチスレッディングは、UltraSPARC T1プロセッサと共に最初に導入され、CMPの優位性を利用し、重要な機能も付加しています。それは周波数よりむしろスレッドと共に拡大することです。従来の単一スレッド化したプロセッサや大半のCMPプロセッサと異なり、ハードウェアのマルチスレッド・プロセッサのコアは、アクティブなスレッド間での急速なスイッチングを許容しています。それ以外のスレッドはメモリで失速します。図1はマルチスレッド、Fine-Grained multi threading (FG-MT)、マルチコア・マルチスレッド・テクノロジの違いを示しています。ここで鍵となるのは、マルチスレッド・プロセッサ内の各コアは各クロック・サイクル上のマルチプル・スレッド間でスイッチするよう設計されていることです。その結果、プロセッサの実行パイプラインはアクティブな状態で実際の作業を行っているのと同時に、失速したスレッドのメモリ動作が継続しています。

図 1. マルチコア マルチスレッド・テクノロジは、マルチプロセッシングとFG-MTを結合したものです。

マルチスレッディングはどんなクロック・サイクルでも実業務を行うために実行パイプラインの能力を上げているので、実質的な価値を提供できます。多くの実行スレッドがリソースを共有しているので、実行パイプラインが大きく強化されています。プロセッサとメモリ・サブシステムはプロセッサ実行パイプラインに並んでアクティブなままなので、メモリの待ち時間というネガティブな要素が効率的に解消します。それぞれのコアは単純なパイプラインを実装し、そのパイプラインは周波数よりもスレッドの拡張性を重視しているため(ILP上のTLPを重視)、より冷却でき、起動の際のエネルギーの省エネルギーを実現しています。この革新的な方式がマルチスレッド・プロセッサ技術です。(コアごとのマルチプル・アクティブ・スレッド・コンテクストとマルチプル・物理インストラクション・実行パイプライン(各コアに1つ))。さらに、UltraSPATC T2/UltraSPARC T2 Pulsプロセッサでは更なるスケーラビリティの向上のため、コアあたり2つの実行パイプラインを実装しています。

.

# 革新的なマルチコア・マルチスレッド・テクノロジ:UltraSPARC T2/ UltraSPARC T2 プロセッサ

複雑な単一スレッド・プロセッサとは違い、チップダイ上のマルチスレッド・プロセッサのコアを実装するため、マルチスレッド・プロセッサはできるだけトランジスタ利用します。UltraSPARC T2/UltraSPARC T2 Pulsプロセッサはマルチスレッドモデルが次のレベルに達したもので、コアごとに2つの独立したパイプラインをサポート、プロセッサあたり最大8つのコアを搭載し、動作クロックを上昇させることなくUltraSPARC T1プロセッサのスループットが2倍になったものです。さらにこれらのプロセッサは、65nmプロセス技術を使用し、業界初のSoCを実装するために設計されています。

- プロセッサあたり最大64スレッド(8コアx,8スレッド)

- オン・チップLevel1、オン・チップLevel2のキャッシュ

- コアごとの浮動小数点機能

- コアごとの暗号化アクセラレータ

- オン・チップ10Gigabit Ethernetインタフェース x2(UltraSPARC T2のみ)

- オン・チップPCI Express インタフェース

- オンチップのキャッシュ・コヒーレンス・ユニット(UltraSPARC T2 Plusのみ)

このSoC設計により、UltraSPARC T2プロセッサは8つの浮動小数点ユニット(コアあたり1つ)を組み込むことでCPUの汎用性を十分に高めています。強化された浮動小数点の機能は、UltraSPARC T2を、従来のマルチスレッディングに配慮したデータセンター・スループット・アプリケーションと同様、コンピュータを駆使したアプリケーションの世界に公開しました。コストをかけていないセキュリティや暗号化の加速はコア単位のストリーミング・アクセラレータによって提供されます。さらに、プロセッサからプロセッサへのデータの転送は、UltraSPARC T2プロセッサでは、PCI-Expressインタフェースと2つの10Gigabit Ethernetインタフェースによって高速化されます。

UltraSPARC T2 Plusでは、マルチソケットシステム設計を実現するために、10Gigabit Ethernetインタフェースの代わりに、キャッシュ・コヒーレンス・ユニットが搭載されています。

# **SPARC Enterprise T5120 / T5220 / T5140 / T5240**

SPARC Enterprise T5120/T5220/T5140/T5240は費用効果の高い汎用性のあるプラットフォームの形式で、UltraSPARC T2/UltraSPARC T2 Plusプロセッサのかなりのリソースを使用して設計されています。SPARC Enterprise T5120/T5220はそれぞれ、前モデルよりも最大2倍のスループットを出し、パフォーマンス全体、ワット単位のパフォーマンスに関して競合をリードしています。SPARC Enterprise T5140/T5240では、UltraSPARC T2 Plusプロセッサを2チップ搭載し、大容量のメモリをサポートすることにより、さらにスケーラビリティを拡大させています。またこれ全てのシステムはマルチスレッドの業務処理から浮動小数点処理の業務までマルチスレッディングのメリットを広げています。

SPARC Enterprise 15120 server

SPARC Enterprise 15220 server

SPARC Enterprise 15140 server

SPARC Enterprise T5240 server

### 概要

128スレッドのサポート、大容量メモリ、暗号化アクセラレータ、10Gigabit Ethernetインタフェース、I/O技術により、これらのサーバは従来のシステム設計とは異なってきています。1U SPARC Enterprise T5120/T5140は高いスループットを、深刻な電力、冷却、スペースの制限の中で出すことができ、1または2つの64スレッドのUltraSPARC T2プロセッサをスペースや電力に効率的な1U ラックマウント・パッケージに利用できるようにします。SPARC Enterprise T5120/T5140は、スケールアウト型のコンピュータ・ノードとして、アプリケーション層、Webサービスに十分なビルディングブロックを提供しています。ポータル・ディレクトリ、ファイル・サーバ、バックアップといったネットワーク・インフラのアプリケーションはこのサーバに非常に適しています。

SPARC Enterprise T5220/T5240は、2U ラックマウント型であり、スループットだけでなく、増設I/Oと内部ディスク・オプションにより拡張性も提供しています。これまで以上のI/Oと内部ディスクにより、アプリケーション・サーバの配置やWebやアプリケーション層の統合、仮想化、統合プロジェクトへの適用が可能です。また、SPARC Enterprise T5220/T5240はOLTPデータベースの配置においても理想的です。

SPARC Enterprise T5120/T5220/T5140/T520 は他のサーバ製品ラインと同様、よりコンパクトに設計され、ダイナミックな現代のデータセンターのニーズに応えようと努力しています。

### • 効率的かつ予測可能なスケーラビリティ

64スレッドと大容量メモリのサポートで、SPARC Enterprise T5120/T5220は初めて UltraSPARC T2チップで提供された10Gigabit Ethernet、I/O、暗号化アクセラレータを 利用しています。こうして、極めて高度な電力、熱、スペースの効率性を実現したパフォーマンスとスケーラビリティを提供しています。

SPARC Enterprise T5140/T5240は、この卓越した計算密度やメモリ密度を拡張し、SPARC Enterprise T5140では、ほんの1Uラックユニット程度のスペース、700ワット以下の電力消費(実効値)で最大128スレッドを提供します。これらのシステムは、それぞれのチップに統合されたPCI Expressインタフェースにより、T5120/T5220の2倍の1/O帯域を提供します。

### • "Time to Market"への加速

SPARC Enterprise T5120/T5220/T5140/T5240は、初期のUltraSPARCシステムとのバイナリの互換性を維持し、Solaris OS上で動作します。そして、市場への投資とスピードを提供します。

### • 簡易化された管理

SPARC Enterprise T5120/T5220/T5140/T5240は、ILOMサービス・プロセッサを提供しています。ILOMサービスは、CLI、WebベースのGUI、IPMI機能を提供して遠隔地からの監視・管理をサポートします。これらのシステム上のILOMはSPARC Enterprise T1000/T2000の管理ツールであるAdvanced Lights Out Management (ALOM)の互換モードを提供しています。

### • 仮想化と統合用の業界最高のツール

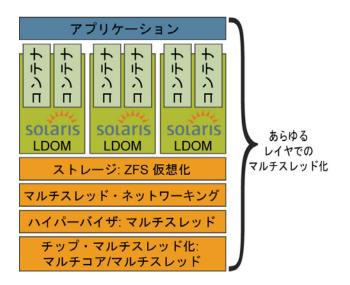

マルチスレッド・テクノロジは統合に適しており、各階層の技術スタックで仮想化の ための低レベルのマルチスレッド・サポートを提供します。論理ドメインは

UltraSPARC T2/UltraSPARC T2 Plusプロセッサのソケットあたり64スレッドを有効利用して、マルチゲストのオペレーティング・システム・インスタンスをサポートする一方で、SolarisコンテナはSolaris OSインスタンスの中で仮想化を提供します。先進のZFSファイル・システムは、ストレージの仮想化により大幅な拡張性を提供します。

### • "eco-responsible"を継承

Sun Fire/SPARC Enterprise T1000/T2000は業界初の" eco-responsible"サーバです。 SPARC Enterprise T5120/T5220/T5140/T5240もこの考え方を踏襲し、広範囲に渡る業務

用、技術用の処理で、ワットあたりのパフォーマンスにおいて最高の成果を出しています。さらに、UltraSPARC T2プロセッサは業界で初めて、そして唯一のコアとメモリの両レベルで独自の電力管理機能を内蔵していました。

### • システムとデータセンターの信頼性

信頼性は、業務継続とコストダウンの鍵となります。SoC設計によって提供されたより高いレベルの統合により、SPARC EnterpriseT5120/T5220/T5140/T5240は同一基準のもと、より高度なRASを提供しています。低消費電力やワットあたりの高パフォーマンスは発生した熱量や関連する諸問題を大きく改善します。Solaris予測的セルフヒーリングといったような技術がハードウェアと統合され、システムを利用可能な状態で維持できるようにします。

#### • ゼロ・コスト・セキュリティ

現在、電子的な侵入や窃盗が多発しており、今日ほど安全な通信やデータ保護が重要 視されたことはありません。各 UltraSPARC T2/UltraSPARC T2 Plus プロセッサには、 最大 8 つの暗号化アクセラレータが搭載されるため、ネットワーク上の通常のテキス トを送信したり、ストレージ・システムに通常のテキストを保存しておいたりする必 要はありません。SPARC Enterprise T5120/T5220/T5140/T5240 は、競合他社のプロセッ サや専用暗号化アクセラレータ・カードと比べて、1 秒あたりより複雑な暗号化機能を サポートして、システムへのオーバーヘッドを最小化しています。

### 革新的なシステム設計

富士通は、データセンターのシステム設計者において、個々のシステムの機能ではカ バー出来ない、特殊で差し迫ったニーズがあることを理解しています。

密度、パフォーマンス、スケーラビリティは、すべて必要な検討項目ですが、システム側には実用性も必要であり、電力、冷却、保守性を考慮した現在のデータセンターの戦略に適合したものでなければなりません。

SPARC Enterprise T5120/T5220/T5140/T5240 は、革新的なデザイン哲学を共有しています。そのデザイン哲学には以下のものが含まれます。

- ・ 最大演算密度: SPARC Enterprise T5120/T5220/T5140/T5240 は、CPU コアやメモリ、ストレージ、I/O に関して優れた密度を提供しています。 密度について、このようにフォーカスすることで、競合する 2U のラックマウントサーバを 1U のラックマウントサーバに置き換えることにより、50%のスペースを節約することが出来ます。

- ・ 優れたストレージ容量:SPARC Enterprise T5120/T5220/T5140/T5240 は、優れた密度と柔軟性を持つ内蔵ストレージを提供しています。より小型のディスクドライブの採用や、革新的な構造、エアフロー、可搬性のあるデザインの採用により、より小さいスペースに、システムのエアフローを高め、より多くのディスク容量を搭載することが出来ます。

- ・ 継続的な投資の保護:富士通は投資の保護を最大限にするように設計しています。 マルチスレッドテクノロジーのような革新的なテクノロジーと同様に、Solaris の バイナリ互換性はアプリケーションが修正を加えることなく動作することを意味 しています。

### 表 1 は SPARC Enterprise T5120/T5220/T5140/T5240 の比較です。

表 1. SPARC Enterprise T5120 / T5220 / T5140 / T5240 特長

|          | SPARC Enterprise T5120    | SPARC Enterprise T5220    | SPARC Enterprise T5140   | SPARC Enterprise T5240    |  |

|----------|---------------------------|---------------------------|--------------------------|---------------------------|--|

| Feature  | Server                    | Server                    | Server                   | Server                    |  |

| CPU      |                           |                           | デュアル                     | デュアル                      |  |

|          | 4, 8core 1.2 GHz          | 4, 8core 1.2 GHz または      | 4, 6, 8 core 1.2GHz      | 6,8core 1.2GHzまたは         |  |

|          |                           | 8core 1.4 GHz             |                          | 8core 1.4GHz <sup>c</sup> |  |

|          | UltraSPARC T2             | UltraSPARC T2             | UltraSPARC T2 Plus       | UltraSPARC T2 Plus        |  |

| スレッド数    | 最大 64                     | 最大 64                     | 最大 128                   | 最大 128                    |  |

| オテリ帝皇    | 最大 64 GB                  | 最大 64 GB                  | 最大 64GB                  | 最大 128GB <sup>d</sup>     |  |

| メモリ容量    | 1,2また4GB FB-DIMM          | 1,2また4GBFB-DIMM           | 1,2 または 4GB FB-DIMM      | 1,2または4GB FB-DIMM         |  |

| 磁気ディスク装置 | <b>-</b> 4/25: 1 GAG      | <b>-</b> + 9/2 5 · 1 GAG) | 最大 4 (2.5-inch SAS)      | 最大 8 または 16(2.5-inch      |  |

|          | 最大 4(2.5-inch SAS)        | 最大 8(2.5-inch SAS)        |                          | SAS) <sup>c</sup>         |  |

| otr. EL  | 73 または 146 GB disk        | 73 または 146 GB disk        | 73 または 146 GB disk       | 73 または 146 GB disk        |  |

| 容量       | drives                    | drives                    | drives                   | drives                    |  |

| 記憶装置     | CD-RW/DVD-RW              | CD-RW/DVD-RW              | CD-RW/DVD-RW             | CD-RW/DVD-RW              |  |

| USB      | USB 2.0 ポート x4            | USB 2.0 ポート x4            | USB 2.0 ポート x4           | USB 2.0 ポート x4            |  |

|          | PCI Express x8:1スロット      | PCI Express x8:2スロット      | PCI Express x8:1スロット     | PCI Express x8 : 4 スロット   |  |

|          | PCI Express x4 or         | PCI Express x4 : 2スロッ     | PCI Express x8 or XAUI:  | PCI Express x8 or XAUI:   |  |

| PCI      | XAUI :2 スロット <sup>a</sup> | ٢                         | 2 スロット <sup>a</sup>      | 2 スロット <sup>a</sup>       |  |

|          |                           | PCI Express x4 or XAUI    |                          |                           |  |

|          |                           | スロット:2スロット <sup>a</sup>   |                          |                           |  |

|          | オン・ボード Gigabit            | オン・ボード Gigabit            | オン・ボードGigabit            | オン・ボードGigabit             |  |

|          | Ethernet(10Base-T/100Bas  | Ethernet(10Base-T/100Bas  | Ethernet(10Base-T/100Bas | Ethernet(10Base-T/100Bas  |  |

| Ethernet | e-TX/1000Base-T) :4ポー     | e-TX/1000Base-T) :4 ポー    | e-TX/1000Base-T) :4 ポー   | e-TX/1000Base-T) :4ポー     |  |

|          | ٢                         | ٢                         | $F^{\mathrm{b}}$         | <b>⊢</b> <sup>b</sup>     |  |

|          | 10 Gigabit Ethernet(XAUI  | 10 Gigabit Ethernet(XAUI  | 10 Gigabit Ethernet(XAUI | 10 Gigabit Ethernet(XAUI  |  |

|          | スロット):2ポート                | スロット) :2 ポート              | スロット) :2 ポート             | スロット):2ポート                |  |

| 電源       | AC 電源 x2 (活性交換、           | AC 電源 x2 (活性交換、           | AC 電源 x2 (活性交換、          | AC 電源 x2 (活性交換、           |  |

| 电机       | N+1 冗長)                   | N+1 冗長)                   | N+1 冗長)                  | N+1 冗長)                   |  |

| ファン      | ファントレイ x4 (活性交            | ファントレイ x3 (活性交            | ファントレイ x6 (活性交           | ファントレイ x5 (活性交            |  |

|          | 換、2 台/トレイ、N+1 冗長)         | 換、2 台/トレイ、N+1 冗長)         | 換、2 台/トレイ、N+1 冗長)        | 換、2 台/トレイ、N+1 冗長)         |  |

a: 10Gigabit Ehternet ポートにアクセスするためにはオプションの XAUI アダプタカードが必要。

XAUI アダプタカードは PCI Express スロットを占有

- b: XAUI アダプタカードを使用すると、1 つの RJ45 Gigabit Ethernet ポートが使用できなくなります。

- 2 つの XAUI ポートを使用した場合には、Gigabit Ethernet ポートは 2 ポートのみ利用可能。

- c:1.4GHzプロセッサおよびディスクドライブ 16 台搭載可能装置を使用時には、200-240V の電源が必要

- d:128GB の最大メモリ構成には、オプションのメモリメザニンキットが必要

# 優れた信頼性、可用性、保守性(RAS)

SPARC Enterprise T5120/T5220/T5140/T5240 は、卓越した信頼性、可用性、保守性(RAS) を提供しています。高い信頼性を持つ部品の採用と、使用する部品点数を低く抑えることにより、システムエラーの発生を最低限に抑えています。

SPARC Enterprise T5140/T5240 では、2 つの PCI Express コントローラと、複数プロセッサ構成が可能なことから、システム障害からの回復力を高めています。

さらに、これらのサーバは、冗長構成が可能な、活性交換可能なディスクドライブ、 電源、ファンと共に、プロセッサコアやスレッドのオフライン機能などの機能を持っ ています。SPARC Enterprise T5120/T5220/T5140/T5240 における以下のようなデザイン 上の重要な要素は、IT サービスにおける信頼性を改善させる鍵となっています。

- 部品点数の削減

- プロセッサコアとスレッドのオフライン機能

- 冗長構成が可能な、活性交換可能なコンポーネント

- パリティ保護とエラー訂正機能

- システム監視

- ILOM サービスプロセッサ

- 優れたエネルギー効率

- 強力な仮想化技術

- 包括的な障害管理

### 第2章

# 第2章 革新的なマルチスレッド・テクノロジを搭載 した、UltraSPARC T2/UltraSPARC T2 Plus プロセッサ

UltraSPARC T2/UltraSPARC T2 Plusは業界初のシステム・オン・チップ (SoC: System on Chip) と呼べるプロセッサです。今日までシステム・レベルて提供されてきた多くの機能と、コア/スレッドを1つのプロセッサ上に統合した革新的なプロセッサです。

# UltraSPARC T2/UltraSPARC T2 Plus: 世界初の大量

# スレッド処理 SoC

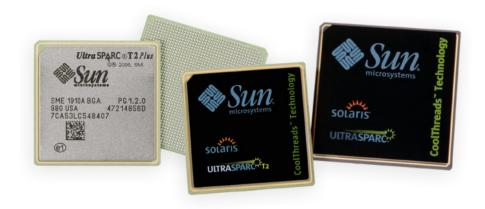

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/ SPARC Enterprise T5240に搭載されるUltraSPARC T2/UltraSPARC T2 Plusプロセッサは、Sun 社のプロセッサ開発戦略チップ・マルチスレッディング・テクノロジー(CMT: Chip Multithreading Technology) に基づき設計/開発された次世代のプロセッサです。 UltraSPARC T2/UltraSPARC T2 Plusプロセッサには、最大8つの「コア (演算ユニット)」が搭載されています。各コアは、8つのスレッドを実行可能であり、各コアとチップ上の2次キャッシュ・メモリは、帯域幅268GB/秒を誇るクロスバーにより相互接続されています。この基本構造の強化により、UltraSPARC T2/UltraSPARC T2 Plusプロセッサは、UltraSPARC T1プロセッサの倍にあたる64スレッドまでの処理が可能となり、結果、スループット性能は、UltraSPARC T1プロセッサを大きく上回るものとなりました。 それにもかかわらずUltraSPARC T2/UltraSPARC T2 Plusプロセッサのサイズは UltraSPARC T1 プロセッサよりコンパクトです。

図 3. UltraSPARC T2 Plus (左) /UltraSPARC T2 (中央) /UltraSPARC T1 (右) の各プロセッサ

表 1 に、UltraSPARC T2/UltraSPARC T2 PlusプロセッサとUltraSPARC T1プロセッサの比較を示します。

表 1. UltraSPARC T1 および UltraSPARC T2 / UltraSPARC T2 Plus プロセッサの特長

| 特長                  | UltraSPARC T1                          | UltraSPARC T2                                                             | UltraSPARC T2<br>Plus                                   |

|---------------------|----------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------|

| コア数/プロセッサ           | 最大 8                                   | 最大 8                                                                      | 最大 8                                                    |

| スレッド数/コア            | 4                                      | 8                                                                         | 8                                                       |

| スレッド数/プロ<br>セッサ     | 32                                     | 64                                                                        | 64                                                      |

| ハイパバイザー             | あり                                     | あり                                                                        | あり                                                      |

| ソケット数               | 1                                      | 1                                                                         | 2または4ª                                                  |

| メモリ                 | メモリ・コントローラ<br>×4、<br>4 DIMM/コント<br>ローラ | メモリ・コントローラ<br>×4、<br>最大 16 FB-DIMM                                        | メモリ・コントロー<br>ラ×2、<br>最大 16/32<br>FB-DIMM                |

| キャッシュ               | シュ、<br>3MB L2 キャッシュ                    | 16KB 命令キャッシュ、<br>8KB データ・キャッシュ、<br>4MB L2 キャッシュ<br>(8 バンク、16 ウェイ・アソシアティブ) | シュ、<br>4 MB L2 キャッシュ                                    |

| テクノロジー              | 90nm テクノロジー                            | 65 nm テクノロジー                                                              | 65 nm テクノロジー                                            |

| 浮動小数点演算ユ<br>ニット     | 1 FPU/チップ                              | 1 FPU/コア、8 FPU<br>/チップ                                                    | 1 FPU/コア、8 FPU<br>/チップ                                  |

| 整数演算ユニット            | 実行ユニット×1                               | 実行ユニット×2/コ<br>ア                                                           | 実行ユニット×2/コ<br>ア                                         |

| 暗号化処理機能             | 高速モジュール算術<br>演算(RSA)                   | ストリーム処理ユ<br>ニット/コア、市場で<br>広く使用されている<br>10 種類の暗号化アル<br>ゴリズムに対応             | ニット/コア、市場<br>で広く使用されてい                                  |

| ネットワーク・<br>インタフェース  | _                                      | 10Gb Ethernet×2                                                           | _                                                       |

| I/O <b>インタフェー</b> ス | _                                      | PCI Express(x8)                                                           | PCI Express(x 8)、<br>コヒーレンシ・ロ<br>ジックとリンク<br>(4.8Gb/sec) |

a. Sun SPARC Enterprise T5140/Sun SPARC Enterprise T5240では、2ソケット

# 次世代へ進化したマルチスレッド設計

開発チームが次世代 マルチスレッド・プロセッサの設計を始めたとき、主に次の目標 を想定しました。

- UltraSPARC T1 プロセッサのスループット性能を 2 倍に引き上げ、増え続ける Web アプリケーションの需要を満たす

- 浮動小数点性能を向上させ、これまで以上に大きく、多様性のあるワークロード をサポートする

- ネットワーク集中型コンテンツに対応するため、ネットワーク機能を高速化する

- データセンターの暗号化をエンド・ツー・エンドで行う

- サービス水準を引き上げ、停止時間を短縮する

- データセンターのキャパシティを改善しながら、コストを削減する

マルチスレッディングアーキテクチャはきわめて柔軟性が高いため、プロセッサ/コア/統合化コンポーネントをモジュール方式でさまざまに組み合わせることができます。社内のエンジニアリング作業では、上記の考慮事項に基づいて、すぐれたUltraSPARC T1 のアーキテクチャをさらに改良することに関して、各種の方法が比較検討されました。社内のエンジニアリング作業では、上記の考慮事項に基づき、UltraSPARC T1 のアーキテクチャをさらに改良する方向で、様々な比較検討なされました。例えば、単純にコアの数を増やせばスループット性能は向上しますが、使用するダイ面積も広くなり、浮動小数点プロセッサなどの統合コンポーネントの統合が難しくなります。最終的な UltraSPARC T2/UltraSPARC T2 Plusプロセッサの設計において、パフォーマンス向上時の最大のボトルネックはメモリ・レイテンシであると結論付けました。そこで、各コアがサポートするスレッド数を増やすこと、ネットワーク帯域幅を増やすことで、UltraSPARC T2/UltraSPARC T2 Plusは UltraSPARC T1プロセッサの倍のスループットを得るというアプローチに落ち着きました。

各UltraSPARC T2/UltraSPARC T2 Plusプロセッサは最大 8 コアからなり、各コアでは 最大 8 スレッド (64 スレッド/プロセッサ) のスイッチングが可能です。さらに、 各コアには 2 つの整数実行ユニットが搭載されているため、1 つの UltraSPARC コア で同時に 2 つのスレッドを実行することが出来ます。図2に、8コアのUltraSPARC T2 /UltraSPARC T2 Plusプロセッサが処理するスレッド・モデルを示します。

図 4.8 コアの UltraSPARC T2 /UltraSPARC T2 Plus プロセッサ 1 つで最大 64 スレッドを実行でき、各コアで同時に最大 <math>8 つのスレッドを実行できます。

# UltraSPARC T2/UltraSPARC T2 Plus プロセッサの

# アーキテクチャ

UltraSPARC T2/UltraSPARC T2 Plusプロセッサの洗練された堅牢なアーキテクチャによって、スループットコンピューティング・イニシアチブをより一層推進します。そして、アプリケーション性能の最大化を目指します。

## UltraSPARC T2 プロセッサ・アーキテクチャ

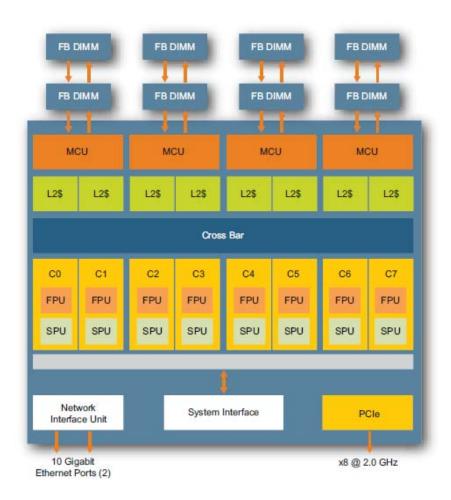

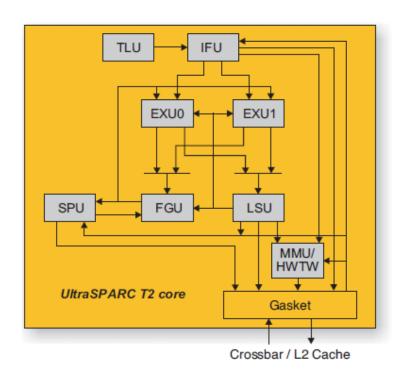

図 5 に UltraSPARC T2 プロセッサのブロック・ダイアグラムを示します。

図 5. SoCの採用により、UltraSPARC T2 プロセッサは 8 つのコア、メモリ管理、暗号化処理機能、10 Gigabit Ethernet×2、および PCI Express(x8)を単一チップ上に統合します。

UltraSPARC T2 プロセッサの 8 つのコアは、フル・オンチップの非ブロッキング型 8×9 クロスバー・スイッチによって相互接続されます。このクロスバーは、各コアを L2 キャッシュの 8 つのバンクに接続し、さらに I/O 用のシステム・インタフェース・ユニットに接続します。クロスバーは約 268GB/秒の帯域幅を提供し、コアからバンク

への 書き込みでは8byte、バンクからコアへの読み取りでは16byte をサポートします。システム・インタフェース・ユニットは、個々のキャッシュ・バンクによって、ネットワークと I/O をメモリに直結します。FB-DIMM の採用により、メインメモリ、キャッシュ間で上り/下り専用レーンをサポートし、パフォーマンスを向上すると同時にレイテンシを低減させています。このアプローチによって、DDR2 以上の帯域幅が得られ、読み取りで最大 42.4 GB/秒、書き込みで最大21 GB/秒の帯域幅が得られます。

各コアにフル・パイプラインの浮動小数点演算ユニットとグラフィック・ユニット (FGU: Floating point / Graphics Unit) を実装するとともに、ストリーム処理ユニット (SPU: Stream Processing Unit) も実装しています。FGU は UltraSPARC T1 をはるかに上回る浮動小数点演算性能を発揮し、SPUは、市場で広く使用されている10 種類の暗号化アルゴリズム(DES, 3DES, AES, RC4, SHA1, SHA256, MD5, 鍵長 2048 bit の RSA, ECC, CRC32)で暗号化を高速に処理します。これら暗号化処理ユニットのオンチップ化により、CPU性能の劣化を気にすることなく、追加コストを気にすることなく、高速なエンド・ツー・エンドの暗号処理が可能となります。

## UltraSPARC T2 Plusプロセッサ・アーキテクチャ

図 6 にUltraSPARC T2 Plusプロセッサのブロック・ダイアグラムを示します。

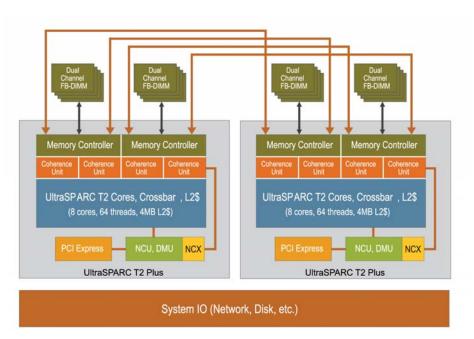

図 6. UltraSPARC T2 Plus プロセッサは、4 本のコヒーレンシ・リンクを用いて、他の最大4つのプロセッサと接続します。。

UltraSPARC T2 Plusアーキテクチャは、デュアル・オンチップ10 Gb Ethernetインタフェースの代わりに、オンチップで4つのコヒーレンシ・ユニット (CU) を提供します。さらにこのプロセッサでは、2 つのメモリ・チャネルが4つのコヒーレンシ・チャネル (コヒーレンシ・リンク) に置き換えられ、コヒーレンシ・ユニットあたり1つのコヒーレンシ・チャネルが提供されています。これらのリンクは、FB-DIMMに似た物理インタフェースを介してキャッシュ・コヒーレンシ (スヌーピー) プロトコルを実行し、各方向で200GB/秒を超える最高4.8G転送/ポートを行います。UltraSPARC T2 プロセッサのメモリ・リンク速度は4.0Gb/秒でしたが、UltraSPARC T2 Plusプロセッサでは4.8Gb/秒に向上しています。

UltraSPARC T2 Plusプロセッサでは、2ソケットと4ソケットの実装をともにサポートしています。一般的な2ソケット実装を図7に示します。UltraSPARC T2 Plusのデュアル・ソケット実装は、プロセッサの4つのコヒーレンシ・リンクを相互接続するため、回路を追加する必要はありません。

図 7. UltraSPARC T2 Plus の一般的なデュアル・ソケット構成

## コア・アーキテクチャとパイプライン

UltraSPARC T2プロセッサとUltraSPARC T2 Plusプロセッサのコア・デザインは同じです。図 8 に、UltraSPARC T2プロセッサのシングルUltraSPARCコア(プロセッサあたり最大8コアをサポート)のブロック・ダイアグラムを示します。

図 6. UltraSPARC T2 のコアのブロック・ダイアグラム

各コアに実装されているコンポーネントは、次のとおりです。

- トラップ・ロジック・ユニット (TLU: Trap Logic Unit) TLUはマシン・ステートを更新し、例外と割り込みを処理します。

- 命令フェッチ・ユニット (IFU: Instruction Fetch Unit) IFUは 16 KB の命令 キャッシュ (32byte ライン、8 ウェイ・セット・アソシアティブ) と 64 エント リのフル・アソシアティブ命令変換ルックアップ・バッファ (ITLB: Instruction Translation Lookup Buffer) からなります。

- 整数実行ユニット (EXU: Integer Execution Unit) コアごとに2つのEXUが提供され、4 スレッドで 1 つのユニットを共有します。スレッドごとに 8 つのレジスタ・ウィンドウが用意されており、整数レジスタ・ファイル (IRF: Integer Register File) のエントリ数はスレッドごとに 160 です。

- **浮動小数点/グラフィック・ユニット** (FGU: Floating Point/Graphics Unit) FGUは各コア内部にあり、コアに割り当てられた 8 スレッドすべてで共有されます。浮動小数点レジスタ・ファイルのエントリ数は、スレッドごとに 32 です。

- **ストリーム処理ユニット**(SPU: Stream Processing Unit ) コアごとに 1 つずつ、暗号コプロセッサを搭載するSPUが組み込まれています。

- メモリ管理ユニット(MMU: Memory Management Unit ) MMUは、ハードウェア・テーブル・ウォーク (HWTW: Hardware Table Walk) を実行し、8 KB/64 KB/4MB/256MBのページングをサポートします。

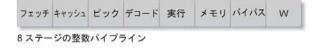

各 UltraSPARC T2/UltraSPARC T2 Plusプロセッサのコアは、8 ステージの整数パイプラインと 12 ステージの浮動小数点パイプラインから構成されます(図 7)。各サイクルで実行する 2 つのスレッドを選択するため、「ピック(Pick)」という新しいパイプライン・ステージが追加されています。

| フェッチ キャッシュ | ピック | デコード | 実行 | Fx1 | Fx2 | Fx3 | Fx4 | Fx5 | Fx6 | FW |

|------------|-----|------|----|-----|-----|-----|-----|-----|-----|----|

|------------|-----|------|----|-----|-----|-----|-----|-----|-----|----|

12 ステージの浮動小数点パイプライン

図 7. UltraSPARC T2 のコアごとの整数パイプラインと浮動小数点パイプライン

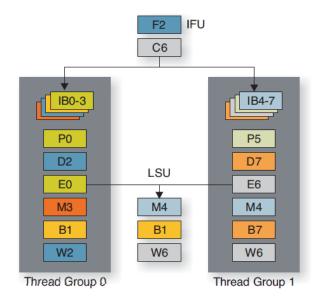

デュアル・パイプラインの機能を説明するために、図 8 にロード・ストア・ユニット (LSU: Load Store Unit) を使用する整数パイプラインを示します。インストラクション・キャッシュは、コア内の 8 つすべてのスレッドによって共有されます。 least-recently-fetched (フェッチが最も古い) アルゴリズムを使用して、次にフェッチするスレッドが選択されます。各スレッドはスレッド固有のインストラクション・バッファ (IB: Instruction Buffer) に書き込まれ、8 スレッドのそれぞれがコア内の 2 つのスレッド・グループのうちのどちらか一方に静的に割り当てられます。

図 8. スレッドはほとんど制限を受けずに、パイプラインのステージ間でインターリーブされます (整数パイプラインの場合、文字はパイプライン・ステージを表し、数字はスケジュールされているスレッドを示します)。

「ピック」ステージでは、各スレッド・グループ内のサイクルごとにスレッドが 1 つ

選択されます。各スレッド・グループ内でのピッキング(選択)は、相互に独立しており、least-recently-picked(ピックが最も古い)アルゴリズムを使用して、次に実行するスレッドが選択されます。デコード・ステージは、ピック・ステージでは処理されないリソースの衝突を解決します。図に示すように、スレッドはほとんど制約を受けずに、パイプライン・ステージ間でインターリーブされます。2 つのスレッド・グループのどちらかに分割する前に、どのスレッドがフェッチ・ステージまたはキャッシュ・ステージにあってもかまいません。ロード/ストアと浮動小数点ユニットは、8 つすべてのスレッド間で共有されます。これらの共有ユニット上でスケジューリングされるのは、どちらかのスレッド・グループから1 つのスレッドだけです。

# 統合ネットワーク機能

ネットワーク・インタフェース・ユニットのオンチップ化により、UltraSPARC T2 プロセッサは、より優れたネットワーク性能を発揮します。すべてのネットワーク・データはメイン・メモリから直接読み込まれます。ネットワーク機能をメモリの近くに配置することにより、レイテンシの低減、メモリ帯域幅の拡張、I/O プロトコル変換にともなう非効率な処理が排除されます。

UltraSPARC T2 プロセッサは、統合 SerDes (シリアライザ・デシリアライザ) により 10Gigabit Ethernet ポートを 2 つ提供し、最速 3 千万パケット/秒でパケット・クラシフィケイション (パケットの分類) を行います (プロトコル・スタックのレイヤ 2 ~4 に基づく)。複数の DMA エンジン (DMA 送信チャネル×16、受信チャネル×16)が DMA と各スレッドを連動させ、ポートとスレッド間のバインドに柔軟性をもたらします。また、仮想化テクノロジにより、8 つまでパーティショニングが可能であり、様々なハードウェア・スレッドの割り込みをバインドできます。

## ストリーム処理ユニット(SPU)

UltraSPARC T2 コア上の各SPUは、コアと同じ周波数で動作します。独立した 2 つのサブ・ユニットがコアのクロスバー・ポートを共有する DMA エンジンとともに提供されています。

- Modular Arithmetic Unit (MAU) は、FGU 乗算器を共有し、RSA 暗号化/復号、バイナリおよび整数多項式関数、および楕円曲線暗号 (ECC: Elliptic Curve Cryptography) \*2を実行します。

\*2 楕円曲線暗号は将来Solaris™OSリリースでサポート予定

- 暗号/ハッシュ・ユニットは、RC4, DES, DES3, AES-128/192/256, MD5, SHA1, SHA-256 のサポートを提供します。

SPU は、UltraSPARC T2プロセッサ上10Gigabit Ethernet ポートで、暗号化/復号処理を実行するよう設計されています。

# PCI Express インタフェースをチップに内蔵

UltraSPARC T2 / UltraSPARC T2 Plus は、ポイント・ツー・ポイントのデュアル・シンプレックス・チップ・インターコネクトによって、レーンごとに双方向に  $4\,GB$ /秒で動作する PCI Express インタフェースを搭載しています。統合 IOMMU は、 PCI

Express BDF 番号を使用し、I/Oの仮想化とプロセス・デバイスの分離をサポートします。総 I/O 帯域幅は 3 ~ 4 GB/秒で、最大ペイロード・サイズは 128 ~ 512byte です。オフチップ PCI Express スイッチとの統合用に1つの x8 SerDes インタフェースが用意されています。

# 電源管理

UltraSPARC T2/UltraSPARC T2 Plus プロセッサには、プロセッサ上のコアとメモリの 双方を制御する電源管理機能が実装されています。この管理機能には、実行命令数の 制御、アイドル状態にあるスレッド/コアのパーキング機能、コア/メモリのクロッ クオフが含まれます。以下は、想定する利用例です。

- 実行されない条件分岐などに対する制限

- データ・パス/制御ブロック/アレイにおける広範なクロック・ゲーティング

- デコード・ステージに余分なストール・サイクルを注入できるパワー・スロット リング

# 第3章 サーバ・アーキテクチャ

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/ SPARC Enterprise T5240 は、消費電力と複雑性を最小限に留めつつ、且つ、信頼性を高め、その中で、パフォーマンスを最大化するよう設計されています。本章では、システムのアーキテクチャと構成するコンポーネントにつき、解説します。

# システムレベルのアーキテクチャ

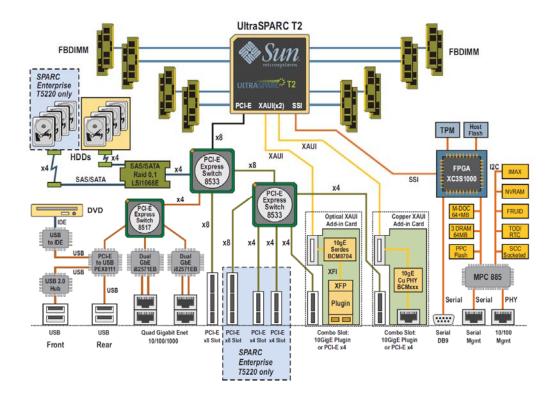

SPARC Enterprise T5120/SPARC Enterprise T5220で同じマザーボードを使用しています (図 9)。このマザーボードは 20 層からなるプリント回路基板 (PCB: Print Circuit Board) であり、UltraSPARC T2 プロセッサ、メイン・メモリ用の FB-DIMM ソケット、ILOM サービス・プロセッサ、ディスク・コントローラ、および I/O サブシステムが組み込まれています。I/O オプションには、USB、DVD、4つのGigabit Ethernet、さらに、PCI Express 拡張オプション用ソケットへの分岐を制御する 2 段階の PLX PCI Express があります。点線で囲まれた領域は、SPARC Enterprise T5220 のみの機能です。

図 9. SPARC Enterprise T5120/SPARC Enterprise T5220 共通マザーボードの ブロック・ダイアグラム

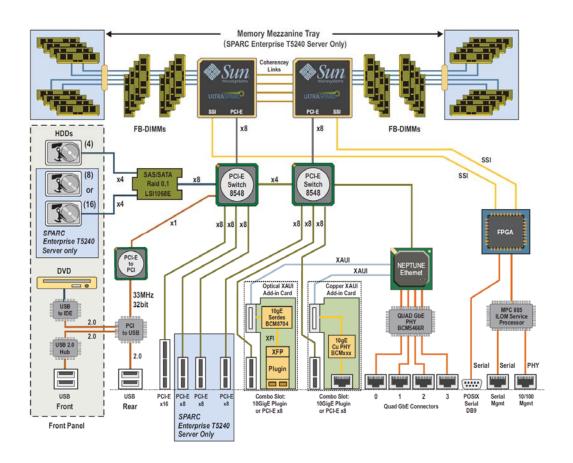

また、SPARC Enterprise T5140/SPARC Enterprise T5240の間でも、同じマザーボードを使用しています(図 10)

図 10. SPARC Enterprise T5140 / SPARC Enterprise T5240 共通マザーボードの ブロック・ダイアグラム

SPARC Enterprise T5140/SPARC Enterprise T5240 のマザーボードには、主に次のような特長があります。

- 4つのコヒーレンシ・リンクで接続された、UltraSPARC T2 Plusプロセッサのデュ アル・ソケット

- SPARC Enterprise T5240に増設メモリを搭載するための、メモリ・メザニン・アセンブリキット(4GBのFB-DIMM使用時システム最大128GB)

- Neptuneチップ(10Gigabit Ethernet)との統合により、10Gigabit Ethernet機能に加え、標準で4つのGigabit Ethernetポート(10/100/1000-BASE-T)を提供

これらのすべてのシステムのマザーボードは前世代から大幅に簡素化されました。配電ボード(PDB: Power Distribution Board)に接続された1対のメタル・バス・バーを介して、12 Vの電力がマザーボードに給電されます。単一のフレックス回路コネクタがPDBへ重要なあらゆるパワー・コントロール信号とDVDドライブのシグナリングを送

ります。1つまたは2つのmini-SASケーブルで、ディスク・ドライブのバックプレーンとマザーボードを接続し、内蔵ディスク・ドライブへのデータ・パスを提供します。。

## メモリ・サブシステム

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 では、UltraSPARC T2/UltraSPARC T2 Plusプロセッサ上のオンチップ・メモリ・コントローラが高速シリアル・リンクを介して、FB-DIMM と直接通信します。UltraSPARC T2 プロセッサには4つのデュアル・チャネルFB-DIMMメモリ・コントローラ・ユニット (MCU)、そしてUltraSPARC T2 Plusプロセッサでは2つのMCUが実装されています。各MCUは、4.0Gb/秒(UltraSPARC T2)または4.8Gb/秒(UltraSPARC T2 Plus)の総レートでデータを転送します。

マザーボードにメモリ・ソケット位置が合計16か所あるため、チャネル毎に2列の667MHz FB-DIMMのためのボード・スペースがあります。SPARC Enterprise T5240 では、さらに16個のFB-DIMMスロットを追加できる、オプションのメモリ・メザニン・アセンブリキットをサポートしています。メモリ・メザニン・アセンブリキット(図 11)を使用することで、SPARC Enterprise T5240は、4GBのFB-DIMM使用時で最大128GBのメモリがサポートできます。

図 11. オプションのメモリ・メザニン・アセンブリキットを使用することで、Sun SPARC Enterprise T5240は、最大128GBのメモリ容量をサポート。

## I/O サブシステム

UltraSPARC T2/UltraSPARC T2 Plusプロセッサには、双方向4GB/秒で動作する8レーンのPCI Express (x8) ポートが1つ組み込まれています。このポートはPLXテクノロジーを採用したPCI Expressエクスパンダ・チップによるI/Oデバイス用のインタフェースであり、PCI Express拡張カード・スロット、もしくは、PCI Expressベースのデバイスを接続します。

ディスク・コントローラ -4 レーンの PCI Express (x4) ポートに接続される LSI Logic SAS1068E SAS コントローラ・チップにより制御されます。

- モジュール方式のディスク・バックプレーン -システムに応じて、4,8,16ディスクのバックプレーンが1つまたは複数のx4SASリンクによりLSIディスク・コントローラに接続されます。16ディスクのバックプレーンは、28ポートのLSILogic SAS Expander によるディスク・ドライブの増設にも対応しています。

- 4ポートの Gigabit Ethernet -SPARC Enterprise T5120/SPARC Enterprise T5220では、2つの PCI Express (x4) ポートから、2つのインテル Ophir デュアル Gigabit Ethernet チップに接続し、筐体背面で合計 4 つの 10/100/1000Mbps Ethernet インタフェースを提供します。SPARC Enterprise T5140/SPARC Enterprise T5240では、Neptune チップ (Gigabit Ethernet) が 2 つの 10/100/1000 BASE-T ポートと、2 つの 10/100/1000 BASE-T インタフェースを提供します。これらのインタフェースは、背面パネルの 4 つの RJ45 コネクタとして実装されています。

- 2 ポートの 10Gigabit Ethernet SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 は、XAUI/PCI Express の共有スロットを通じ、2つの10Gigabit XAUI 接続を提供します。SPARC Enterprise T5120/SPARC Enterprise T5220 では、これらのポートはUltraSPARC T2プロセッサに統合されているデュアル 10Gigabit Ethernet ポートによって提供されます。SPARC Enterprise T5140/SPARC Enterprise T5240 では、Neptune チップによって10Gigabit Ethernet インタフェースが提供されます。10Gigabit Ethernet ポートが接続されると、2つの Gigabit Ethernet ポートが使用できなくなります。

- USB および DVD ーすべてのサーバ上でシングル・レーン PCI Express ポートから PCI ブリッジ・デバイスに接続されます。セカンド・ブリッジ・チップが 32bit 33MHz PCI バスを複数の USB 2.0 ポートに提供します。システムの USB インターコネク トはこれらのポートから制御されます。さらに、DVD は USB ポートの 1 つを IDE フォーマットに変換する別のブリッジ・チップにより制御されます。

## 筐体設計の刷新

SPARC Enterprise T5140/SPARC Enterprise T5240 サーバの基本的な筐体設計は、SPARC Enterprise T5120/SPARC Enterprise T5220 サーバと共通です。そのため、製品群全体で一貫したルック・アンド・フィールを実現できるだけではなく、一貫したコンポーネント配置とコンポーネントの共有によって、管理を簡素化しています。さらに、一貫性のみならず、データセンター用に差別化できる箇所には主要なテクノロジーを配備するという、データセンターを考慮した設計を施しています。

システムとコンポーネントの保守性の強化 今日のデータセンター環境において、各サーバとコンポーネントを検索し識別することは、課題の1つになっています。SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 は、特定しやすいサーバとモジュールにより、データセンターの自動構成に対応できるよう最適化されています。カラーコード化されたオペレータ・パネルでは分かりやすい診断が行え、システムはホットアイル/コールドアイルのマルチラック配備に対応した設計と なっており、前面と背面の診断 LED によって障害のあるコンポーネントを特定することができます。障害コンポーネントの識別には、Fault Remind 機能が使用されます。

• 筐体、コンポーネント、およびサブアセンブリの堅牢な設計

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 は、信頼性と安定した冷却運転を維持できるよう綿密に設計された筐体を採用しています。筐体の六角形の通気口などの特長も、高い強度、最大限の気流、そして電力効率の最大化を実現するための最適なアイディアに基づいて設計されています。次世代のハード・ディスク・ドライブのキャリアは筐体の六角形の通気方式を採用し、システムへの気流を増加させながら、7%小さくなった前面プレートでストレージ密度を高めています。

各システムのリムーバブル・ディスク・ケージは、ファン・トレイ・アセンブリ に直接差し込まれるため、ディスク・ドライブの上下に冷却気流を送り、さらに、メモリ DIMM とメザニン・ボードの上下にも冷却気流を送るため、システムを効 率的に冷却します。デュアル冷却ファン・モジュールは筐体から分離され、他のシステム・コンポーネントに回転振動が伝わらないようになっています。また、ファン電源ボードをファン・トレイ・アセンブリに一体化させることで、ファンの取り外しや取り付けの際の感電を防ぎます。

計算密度/I/O 密度/ストレージ密度にもかかわらず、SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240は従来のテクノロジーを用いて適切な冷却を維持します。実際、ファン・トレイは多数のファンを搭載できますが、多様なシステムの冷却に実際に必要となるファン数だけが構成されます。

DC-DC の電力変換を最小限に抑えることによっても、システム全体の効率性に貢献しています。12 V の電力をマザーボードに供給することで、電力変換を不要にしています。このようなアプローチが発熱を抑え、システムの効率をさらに向上しています。

• 気流を最大にするためにケーブルを最小限に

配線を最小限にし、かつ信頼性を向上させるために、各筐体に適した様々な小型 ボードとライザー・カードが使用されています。これらのボードやカードがSPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 の拡張機能を提供しています。

- 配電ボードにより、2つの電源装置からマザーボードに、さらに(コネクタ・ボードを経由して)ディスク・バックプレーンに電源が供給されます。

- コネクタ・ボードにより、多数の配線ケーブルが不要となりました。コネクタ・ボードは、制御信号と多くのデータ信号をディスク・バックプレーン/ファン・ボード/PDB に分配するダイレクト・カード・プラグイン・インターコネクトとして機能します。

- ファン・ボードは、筐体前面のプライマリ・ファンとセカンダリ・ファンの 双方に対して、電力と制御用信号を提供します。各デュアル・ファン・モジュー

ルは、 PCB に直接差し込み、さらにそれをコネクタ・ボードに差し込むため、ケーブルは必要ありません。

- PCI Express ライザー・カードは、マザーボードに直接差し込みます。PCI Express を占有しません。

- 2 つの XAUI ライザ・カードが UltraSPARC T2 プロセッサまたは Neptune Ethernet チップ上の 10Gigabit Ethernet インタフェースにアクセスするスロットを提供します。XAUI カードを使用しない場合は、PCI Express インタフェースとして使用可能です。各スロットには、ファイバーもしくは銅線接続用XAUI カード、または最大で x8 フォーム・ファクタ・エッジ・コネクタを備えた業界標準のロープロファイル PCI Express カードを搭載できます。カードは水平に取り付けます。

- ディスク・バックプレーンは、2 つの筐体のディスク・ケージに搭載されていて、マザーボードからの1つまたは2つの4チャネルが独立した mini-SASケーブルにより、データを送受信します。SPARC Enterprise T5120/SPARC Enterprise T5140 には4 ディスクのバックプレーンが用意され、SPARC Enterprise T5220 は8 ディスクの、そして SPARC Enterprise T5240 には8 ディスクまたは16 ディスクのバックプレーンがそれぞれ用意されています。

- 前面 USB パネル・カードは、ディスク・バックプレーンに直接差し込んで、 筐体前面に2つの USB ポートを提供しています。

# SPARC Enterprise T5120 の概要

コンパクトなSPARC Enterprise T5120は、省スペースで消費電力の少ない1Uのラックマウント・サーバであり、優れた演算性能を高い電力効率、設置効率で発揮します。価格対性能比に優れ導入コストが抑えられるこのサーバは、密接に統合された高性能10Gigabit Ethernetと相まって、きわめて高いネットワーク・パフォーマンスを必要とする水平展開型のトランザクション処理や、Webサービスの提供に最適であり、HPCコンピューティング・ノードとして最適なサーバです。このサーバは、消費電力が大幅に削減され、設置面積もわずかであり、現在、データセンターが抱えている課題に対処できるように設計されています。シングル・プロセッサ対応のSPARC Enterprise T5120には、4コアまたは8コアのUltraSPARC T2プロセッサが搭載されます。、筐体前面に2つのUSBポートを提供しています。

### エンクロージャ

1U のSPARC Enterprise T5120 は、標準 19 inchラックに搭載可能なよう設計されています。(表 3).

表 3. SPARC Enterprise T5120 の寸法と重量

| 寸法  | 国際単位    |

|-----|---------|

| 幅   | 425 mm  |

| 奥行き | 714 mm  |

| 高さ  | 44 mm   |

| 重量  | 16.6 kg |

SPARC Enterprise T5120 に組み込まれている主要コンポーネントは、次のとおりです。

- 1.2GHz UltraSPARC T2 プロセッサ (4コアまたは8 コア) x1

- FB-DIMMスロット x16 (最大 64 GB、 1GB/2GB/4GB FB-DIMM をサポート)

- オンボード 10/100/1000 BASE-T Ethernet ポート x4

- PCI Express(x8)スロット x1 (ロープロファイル/MD2)

- PCI Express(x4)スロット x2 (ロープロファイル/MD2、オンチップ10Gigabit Ethernet使用時に用いるXAUIアダプタと兼用)

- USB 2.0 ポート x4 (前面x2、背面x2)

- 2.5" SASディスク・ドライブ x4 (標準2台、最大4台)

- ILOM (Integrated Lights out Management) システム・コントローラ

- AC電源ユニット x2 (N+1、ホットスワップ対応)

- ファン・アセンブリ x4 (2ファン/アセンブリ) 環境モニタ/制御下で計8つまで搭載可能、N+1 の冗長構成

# 前面図と背面図

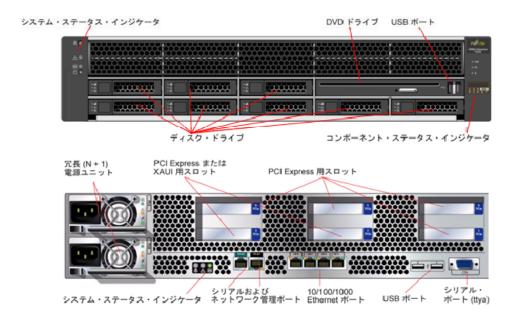

図 10 に SPARC Enterprise T5120 の前面パネルと背面パネルを示します。

図 10. SPARC Enterprise T5120 の前面パネルと背面パネル

SPARC Enterprise T5120 の外装部は以下のとおりです。

- システムとコンポーネントのステータス・インジケータ。システム状態をロケータ(ホワイト)/保守の必要性(オレンジ)/正常状態(グリーン)として点灯表示(前面/背面)

- ホットプラグ対応SAS ディスク・ドライブ x4 (前面パネルから装脱着可)

- CD-RW/DVD-RWドライブ x1 (前面)

- USB ポート x4 (前面パネル x2、背面パネル x2)

- ファン内蔵のホットプラグ/ホットスワップ対応の電源装置 x2台 (N+1冗長構成) (背面)

- 各電源装置の動作状態を点灯表示する電源装置インジケータ(背面)

- 自動検知 10/100/1000 BASE-T Ethernet ポート x4

- シリアル・デバイス用 DB-9 TTYA シリアル・ポート x1 (ILOM システム・コントローラには接続不可)

- PCI Express カード・スロット x3 (2スロットは UltraSPARC T2 上のオンチップ 10Gigabit Ethernet インタフェース接続時用 XAUI アダプタと兼用)

- ILOM システム・コントローラ用管理ポート x2。

ILOM コントローラへのデフォルト接続用シリアルポート (RJ45)

ネットワーク管理ポート10/100BASE-T (RJ45)

# SPARC Enterprise T5220 の概要

拡張性に優れたSPARC Enterprise T5220 は、Java<sup>TM</sup> 2 Platform, Enterprise Edition (J2EE<sup>TM</sup> プラットフォーム) テクノロジー・アプリケーション・サービス、エンタープライズ・アプリケーション・サービス(ERP/CRM/SCM)、分散データベースなどのトランザクション処理や Web サービスの提供基盤として最適です。拡張性と仮想化テクノロジの融合したSPARC Enterprise T5220 は、ネットワーク・サービス、アプリケーション・サービスの統合インフラとしても最適なプラットフォームです。

### エンクロージャ

SPARC Enterprise T5220 は、拡張性に優れながらもコンパクトな 2U ラックマウント・サーバです。限りある設置スペースを有効に利用しながら、処理性能と I/O拡張性を両立するサーバ統合に最適なプラットフォームです(表4)。

表 4. SPARC Enterprise T5220 の寸法および重量

| サーバ/寸法 | 国際単位    |

|--------|---------|

| 幅      | 425 mm  |

| 奥行き    | 714 mm  |

| 高さ     | 88 mm   |

| 重量     | 23.6 kg |

SPARC Enterprise T5220 に組み込まれている主要コンポーネントは、次のとおりです

- 1.2GHzまたは1.4GHz UltraSPARC T2 プロセッサ (4コアまたは8 コア) ×1

- FB-DIMMスロット x16 (最大 64 GB、 1GB/2GB/4GB FB-DIMM をサポート)

- オンボード 10/100/1000 BASE-T Ethernet ポート x4

- PCI Express(x8)スロット x2 (ロープロファイル/MD2)

PCI Express(x4)スロット x2 (ロープロファイル/MD2)

- PCI Express(x4)スロット x2 (ロープロファイル/MD2、オンチップ10Gigabit Ethernet使用時に用いるXAUIアダプタと兼用)

- USB 2.0 ポート x4 (前面x2、背面x2)

- 2.5" SASディスク・ドライブ x4 (標準2台、最大8台)

- ILOM (Integrated Lights out Management) システム・コントローラ

- AC電源ユニット x2 (N+1、ホットスワップ対応)

- ファン・アセンブリx3(2ファン/アセンブリ)

環境モニタおよび制御の下で計6つ搭載可能、N+1の冗長構成

## 前面図と背面図

図 11 に、SPARC Enterprise T5220 の前面パネルと背面パネルを示します。

図11. SPARC Enterprise T5220 の前面パネルと背面パネル

SPARC Enterprise T5220の外装部は以下のとおりです。

- システムとコンポーネントのステータス・インジケータ。システム状態をロケータ(ホワイト)/保守の必要性(オレンジ)/正常状態(グリーン)として点灯表示(前面/背面)

- ホットプラグ対応SAS ディスク・ドライブ x8 (前面パネルから装脱着可)

- CD-RW/DVD-RWドライブ x1 (前面)

- USB ポート x4 (前面パネル x2、背面パネル x2)

- ファン内蔵のホットプラグ/ホットスワップ対応N+1 電源装置 x2 (N+1冗長構成。 背面の電源装置インジケータが、各電源装置の状態を点灯表示)

- 自動検知 10/100/1000 BASE-T Ethernet ポート x4

- シリアル・デバイス用 DB-9 TTYA シリアル・ポート x1 (ILOM システム・コントローラには接続不可)

- PCI Express カード・スロット x6 (2スロットは UltraSPARC T2 上のオンチップ 10Gigabit Ethernet インタフェース接続時用 XAUI アダプタと兼用)

- ILOM システム・コントローラ用管理ポート x2

ILOM コントローラへのデフォルト接続用シリアルポート (RJ45)

ネットワーク管理ポート10/100BASE-T (RJ45)

# SPARC Enterprise T5140 の概要

最大2つのUltraSPARC T2 Plusプロセッサと、最大128のスレッドをサポートするコンパクトなSPARC Enterprise T5140は、省スペースで消費電力の少ない1Uのラックマウント・サーバで卓越した演算パフォーマンスを発揮します。価格対性能比に優れ、導入コストが抑えられるこのサーバは、水平展開型のトランザクション処理やWebサービスの提供に最適であり、サーバ統合および仮想化サーバとして最適です。このサーバは消費電力が大幅に削減され、設置面積もわずかであり、今日のデータセンターが抱える課題に対処できるように設計されています。SPARC Enterprise T5140には、4コア/6コア/8コアのUltraSPARC T2 Plusプロセッサが2つ搭載されています。

# エンクロージャ

1UのSPARC Enterprise T5140のエンクロージャは、標準19 inchラックに搭載可能なように設計されています (表 5)。

表 5. SPARC Enterprise T5140 の寸法および重量

| 寸法     | 国際単位    |

|--------|---------|

| 幅      | 425 mm  |

| 奥行き    | 714 mm  |

| 高さ     | 44 mm   |

| 重量(最大) | 16.8 kg |

SPARC Enterprise T5140サーバに組み込まれている主要コンポーネントは、次のとおりです。

- 1.2GHz UltraSPARC T2 Plusプロセッサ(4コア/6コア/8 コアのいずれか)×2

- FB-DIMMスロット×16 (1GB/2GB/4GB FB-DIMMをサポート。最大64GB)

- オンボード10/100/1000 Mbps Ethernetポート×4

- 専用のロープロファイルPCI Express (x8) スロット (コネクタ形状はx16)

- コンビネーション型XAUIまたはロープロファイルPCI Express (x8) スロット×2

- USB 2.0ポート×4 (前面×2、背面×2)

- 2.5inch SASディスク・ドライブ×4台 (標準2台、最大4台)

- ILOM (Integrated Lights out Managemet) システム・コントローラ

- 効率性に優れた720 W 電源ユニット×2 (N+1、ホットスワップ対応)

- ファン・アセンブリ×6台(2ファン/アセンブリ,N+1の冗長構成)

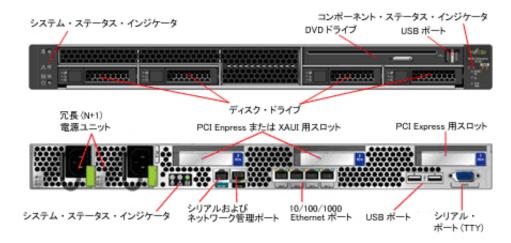

## 前面図と背面図

図 11 に、SPARC Enterprise T5140 の前面パネルと背面パネルを示します。

図11. SPARC Enterprise T5140 の前面パネルと背面パネル

SPARC Enterprise T5140の外装部は以下のとおりです。

- システムとコンポーネントのステータス・インジケータ。システム状態をロケータ(ホワイト)/保守要求(オレンジ)/正常状態(グリーン)として点灯表示(前面/背面)

- ホットプラグ対応SASディスク・ドライブ×4台(前面パネルから装脱着可)

- DVD-RWドライブ×1台(前面)

- USB 2.0 ポート×4 (前面パネル×2、背面パネル×2)

- ファン内蔵のホットスワップ対応電源装置 ×2台 (N+1冗長構成。背面)

- 各電源装置の状態を点灯表示する電源装置インジケータ(背面)

- 各ホットプラグ/ホットスワップ対応電源装置に1つのACプラグ

- 自動検知10/100/1000 BASE-T Ethernet ポート×4

- シリアル・デバイス用DB-9 TTYAシリアル・ポート×1 (ILOM システム・コントローラには接続不可)

- PCI Expressカード・スロット×3

(2スロットのいずれかがNeptune EthernetチップXAUIインタフェース接続時用XAUIアダプタと兼用)

- ILOMシステム・コントローラ用管理ポート×2

ILOMコントローラへのデフォルト接続用シリアル・ポート (RJ45)

ネットワーク管理ポート10/100BASE-T (RJ45) )

#### SPARC Enterprise T5240 の概要

拡張性に優れたSPARC Enterprise T5240は、JavaTM 2 Platform, Enterprise Edition(J2EE プラットフォーム)テクノロジーによるアプリケーション・サービス、エンタープライズ・アプリケーション・サービス(ERP/CRM/SCM)、分散データベースなど、処理の増加にも柔軟に対応できるトランザクション処理やWebサービスの提供に最適です。2 つのUltraSPARC T2 Plusプロセッサをサポートし、拡張性に優れ、仮想化技術が統合されたSPARC Enterprise T5240は、ネットワーク・サービス、アプリケーション・サービスの統合インフラとしても最適なプラットフォームです

#### エンクロージャ

SPARC Enterprise T5240は、コンパクトながら拡張性のある2Uラックマウント筐体(表 5)で、貴重なスペースを無駄にすることなく、処理とI/Oニーズに合わせて柔軟な拡張が可能です(表 6)。

表 6. SPARC Enterprise T5240 の寸法および重量

| 寸法      | 国際単位    |

|---------|---------|

| 幅       | 425 mm  |

| 奥行き     | 714 mm  |

| 高さ      | 88 mm   |

| 重量 (最大) | 23.9 kg |

SPARC Enterprise T5240サーバに組み込まれている主要コンポーネントは、次のとおりです。

- 1.2 GHz UltraSPARC T2 Plusプロセッサ (6または8コア) ×2 または1.4 GHz\*3

UltraSPARC T2 Plusプロセッサ (8コア) ×2

- FB-DIMMスロット×16または32 (オプションのメモリ・メザニン・アセンブリキット使用時)

(1GB/2GB/4GB FB-DIMMをサポート。最大128GB)

- オンボード10/100/1000 Mbps Ethernet ポート×4

- 専用のロープロファイルPCI Express (x8) スロット×4 (うち、1スロットのコネクタ形状はx16)

- コンビネーション型XAUIまたはロープロファイルPCI Express (x8) スロット×2

- USB 2.0ポート×4 (前面×2、背面×2)

- 2.5inch SASディスク・ドライブ×8台または16台\*3

- ILOM (Integrated Lights out Managemet) システム・コントローラ

- 効率性に優れた1,100W電源ユニット×2 (N+1、ホットスワップ対応)

- ファン・アセンブリ×5台(2ファン/アセンブリ、N+1の冗長構成)

\*3: 1.4 GHz プロセッサのサポートまたは16 ディスク・バックプレーンのサポートに、ハイライン電力入力 (200V - 240V) が必要です。

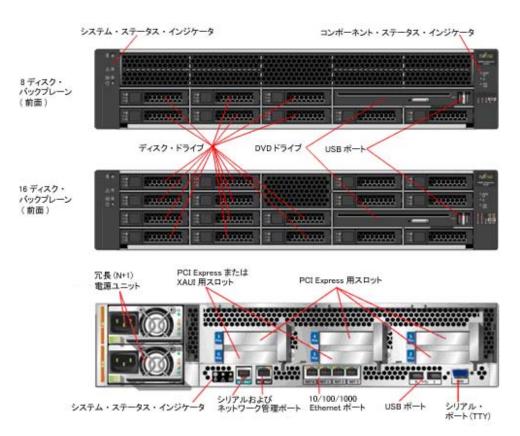

#### 前面図と背面図

図 11 に、SPARC Enterprise T5240 の前面パネルと背面パネルを示します。

図11. SPARC Enterprise T5220 の前面パネルと背面パネル

SPARC Enterprise T5240の外装部は以下のとおりです。

- システムとコンポーネントのステータス・インジケータ。

システム状態をロケータ(ホワイト)/保守要求(オレンジ)/正常状態(グリーン)として点灯表示(前面/背面)

- ホットプラグ対応SASディスク・ドライブ×8台または16台 (前面パネルから装脱着可)

- DVD-RWドライブ×1台(前面)

- USB 2.0 ポート×4 (前面パネル×2、背面パネル×2)

- ファン内蔵のホットプラグ/ホットスワップ対応電源装置×2 台(N+1冗長構成。 背面)

- 各電源装置の状態を点灯表示する電源装置インジケータ(背面)

- 自動検知10/100/1000 BASE-T Ethernet ポート×4

- シリアル・デバイス用DB-9 TTYAシリアル・ポート×1 (ILOM システム・コントローラには接続不可)

- PCI Expressカード・スロット×6

(2スロットのいずれかがNeptune EthernetチップXAUIインタフェース接続時用 XAUIアダプタと兼用)

• ILOMシステム・コントローラ用管理ポート×2 ILOMコントローラへのデフォルト接続用シリアル・ポート (RJ45) ネットワーク管理ポート10/100BASE-T (RJ45)

## 第4章 エンタープライズ・クラスの管理とソフトウェア

新しいテクノロジーに対応するツールとアプリケーションが市場で揃うには、多くの場合、時間を要するものです。また、新しいテクノロジーを実運用環境中に取り込み、その上で可用性の高いサービスを実現するためには、安定した開発ツール/オペレーティングシステム/ミドルウェア/管理ソフトウェアが必要とされるものです。

UltraSPARC T2/UltraSPARC T2 Plus プロセッサは、革新的なテクノロジーでありながら従来のSPARCシステムとバイナリ・レベルで互換性を維持しているため、納入直後からプリインストールされたSolaris OSとプリロードされたツールを利用して、即時機能させることが可能です。さらに、豊富な開発ツールが完備されているため、

UltraSPARC T2 / UltraSPARC T2 Plus プロセッサがもたらす能力を、即実運用環境へ 導入し、アプリケーション開発とそのチューニングに着手することができます。

#### システム管理テクノロジ

どのような企業でもシステム数が増加すれば、ライフサイクル全般にわたってITシステム基盤の管理が複雑になり、困難を増していきます。より効率的なシステム管理には、主要なシステム・コンポーネントの動作を監視するシステム・コントローラとともに、主なシステム管理作業を自動化出来る先進的なフレームワークが必要とされます。

### ILOM(Integrated Lights-Out Management )システム・コントローラ

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240/SPARC Enterprise T5240には、システム・コントローラ、ILOM が搭載されています。 ILOM は、システム管理に求められる次の機能を提供します。

- IPMI 2.0 に準拠したサービス・プロセッサ。IPMI 管理機能をサーバのファームウェア、OS、アプリケーションに提供。 さらに イーサネット管理インタフェース経由でのアクセスも可能

- CPU、DIMM、電源装置など、インベントリと環境を管理。HTTPS/CLI/SNMP に よるアクセスが可能

- テキスト指向のリモート・コンソール・インタフェースを提供

- システム・ファームウェアのアップグレード

ILOM は、オペレーティングシステムの種類を問いません。ILOM は、システムの動作に影響を与えることなく、サーバのリモート管理を可能とします。ILOM は、ハードウェア障害や警告、その他のイベントを電子メールにて管理者に通知することも出来ます。仮に、オペレーティングシステムがオフラインの場合でも、サーバの電源がオフになっても、ILOM は機能し続けます。ILOM は、これらのサーバの次の条件を監視します。

- CPU の温度

- ハードディスク・ドライブの有無

- エンクロージャ内の温度

- ファンの速度と動作状態

- 電源装置の状態

- 電圧

- Solaris のウォッチドッグ、ブート・タイムアウト、自動サーバ再起動のイベント

#### サーバ管理ソフトウェア

IT (情報技術) の普及により複雑化したサーバを管理するためには、サーバを統合的 に監視・制御できるソフトウェアが必要です。富士通では、Solaris, Linux, Windowsサーバを統合管理できるサーバ管理ソフトウェア Server System Manager を提供しています。また統合運用管理ソフトウェア Systemwalker との連携により業務運用を自律化、ビジネス環境の変化に即対応し、ビジネスの継続を支えます。

#### **Server System Manager (SSM)**

Server System Manager は、富士通UNIXサーバ SPARC Enterprise、基幹IAサーバ PRIMEQUEST、PCサーバ PRIMERGYで構築されたヘテロ環境のシステムを統合管理できる、サーバ管理ソフトウェアです。複数のプラットフォームの混在環境において、各サーバのハードウェアの構成表示や状態監視などを行うサーバ管理機能をGUIで提供します。

Server System Managerを利用することにより、1台の管理クライアントから複数のサーバの状態を監視することができます。各サーバのハードウェア構成は、プラットフォーム共通のイメージ(ツリー形式)で表示され、サーバの構成部品の状態を一目で把握でき、統一された操作でサーバの管理を行えます。また、ラックに搭載している装置のレイアウト表示や、CPU、メモリの資源使用状況のリアルタイム表示も可能です。

Server System ManagerはILOMと連携しています。サーバの構成部品に異常が発生すると、ILOMを通じてServer System Managerの管理画面に故障箇所が表示されるため、故障部品を容易に特定できます。さらにこれらの異常発生をメールやSNMP Trapにより通報することができます。また、特定サーバのイベントや特定レベルのイベントのみ通報を行うフィルタリング設定も可能です。

さらに、Solarisコンテナ の管理を、管理クライアントから行うことができます。GUI ウィザード (対話形式) を用いて、仮想Solaris環境 (zone) の作成、設定変更、削除や起動、停止が行えます。

Server System Managerを利用することで、サーバの運用管理作業が容易になり、ハードウェア故障時の対応を迅速に行えます。そのため、運用管理者の作業負担が軽減します。

#### **Enhanced Support Facility (ESF)**

Enhanced Support Facility は、ILOMと連携してSPARC Enterpriseの運用管理性・保守性を向上させるソフトウェアです。本体装置の構成、状態の表示や故障情報の表示が行えます。また、OS上からディスクや電源、PCIカード等の状態を監視し、トラブルが発生すると検知した情報を表示することができます。他にも、システム情報の一括採取や、/etc/systemsファイルの設定チェックなどが可能です。

#### Systemwalker Centric Manager

Systemwalker Centric Managerは、システム運用のライフサイクル(導入/設定~監視~復旧~評価)に従い、ソフトウェア資源の配付、システムやネットワークの集中監視、リモートからのトラブル復旧などの優れた機能で運用管理作業を軽減します。また、このライフサイクル管理によりマルチプラットフォーム環境やインターネット環境など、最新のビジネス環境におけるシステムの統合管理、運用プロセスの標準化(ITIL)、運用セキュリティの統制を支援します。

#### マルチスレッド・テクノロジのスケーラビリティとサポート

Solaris 10 OSは、UltraSPARC T2/UltraSPARC T2 Plusプロセッサ搭載システムの能力を余すところなく引き出せるよう設計されています。Solaris 10 OS は、垂直/水平方向への拡張に優れているばかりでなく、仮想化/利用率/可用性/セキュリティ/パフォーマンスを高めるため、大きな役割を果たしています。Solaris 10 OS は、SPARC/x64/x86 ベースのシステム上で動作し、既存のアプリケーションとの互換性をも保証しています。

UltraSPARC T2/UltraSPARC T2 Plusプロセッサを搭載するシステムの最大の魅力は、Solaris OSとSolaris上で動作するアプリケーションから見た時、それがかつてのSMPシステムの如く扱える点にあります。Solaris 10 OSには、マルチスレッドアーキテクチャ上でアプリケーション・パフォーマンスを向上させるための多数の機能が組み込まれています。

#### • マルチスレッド・テクノロジ への対応

Solaris 10 OSは、UltraSPARC T2 / UltraSPARC T2 Plusプロセッサを64の論理プロセッサの固まりとして認識し、使用可能なすべてのパイプライン間で負荷が効果的に分散するよう、スレッド間の相関関係に応じ、効果的にスレッドを割り当てます。。

#### • きめ細かい管理が可能

Solaris 10 OSには、個々のプロセッサを有効にしたり無効にしたりする機能が備わっています。UltraSPARC T2/UltraSPARC T2 Plusプロセッサの場合、この機能が拡張され、個々のコアおよびスレッド(論理プロセッサ)を有効または無効にすることができます。さらに、プロセッサ・セットなど、Solaris OSの標準機能が論理プロセッサ・

グループを定義し、それらのグループに対してプロセスまたはスレッドをスケジューリングする機能を持ち合わせています。

#### • インタフェースのバインド

Solaris OS では、必要に応じて、個々のプロセスとスレッドをプロセッサまたはプロセッサ・セットに自在にバインドできます。

#### • 仮想化されたネットワーク機能と I/O および高速暗号化処理サポート

Solaris OSには、UltraSPARC T2プロセッサ上の拡張機能をサポートし、仮想化するテクノロジーが組み込まれています。これには、オンチップ10Gb Ethernetポート/PCI Expressインタフェース/暗号化処理機構が含まれます。ハイパフォーマンス・ネットワーク・アーキテクチャの一部として、マルチスレッディングを認識するデバイス・ドライバが用意されているので、仮想化フレームワーク内で動作するアプリケーションは、I/Oとネットワーク・デバイスを実質的に共有します。また、Solaris Cryptographic Frameworkによって高速な暗号化がサポートされます。

#### Solaris OS ONUMA の最適化

SPARC Enterprise T5140/SPARC Enterprise T5240 サーバでは、UltraSPARC T2 Plusプロセッサがメモリを管理し、非均一メモリ・アクセス(NUMA: Non-Uniform Memory Access)アーキテクチャとして実装されています。 NUMAアーキテクチャでは、プロセッサが自分のメモリにアクセスするため に必要となる速度は、別のプロセッサによって管理されるメモリにアクセス するために必要となる速度と若干異なります。 Solaris OSでは、アプリケーションがNUMAアーキテクチャにおけるパフォーマンスを向上できるよう なテクノロジーを提供します。

- メモリ配置の最適化(MPO: Memory Placement Optimization)

Solaris 10 OSでは、MPOによって サーバの物理メモリ全体におけるメモリの配置を改善し、パフォーマンスを高めています。MPOを使用することで、Solaris 10 OSは、システム内の均衡を十分に保ちつつ、メモリにアクセスするプロセッサの近くにメモリを配置します。その結果、データベースとHPCアプリケーションの多くが、より迅速に動作できるようになります。

- Hierarchical Lgroup Support (HLS)

HLS は、Solaris OSのMPOの機能を向上させます。HLSを活用すると、

Solaris OSは、複雑なメモリ・レイテンシ階層を持つシステムのパフォー

マンスを最適化することができます。また、Solaris OSはHLSによりメモ

リがどの程度離れているかを識別できるため、レイテンシが最小のリ

ソースをアプリケーションに割り当てることができます。あるアプリ

ケーションに対し、デフォルトでローカル・リソースを使用できない場

合は、Solaris OSはHLSにより、もっとも近くにあるリモート・リソースを割り当てます。

#### ● Solaris<sup>TM</sup> ZFS

Solaris ZFS(zettabyte file system)により、データ管理/自動化/ストレージ統合が劇的に進歩します。世界初の 128 bit ファイルシステムによる究極のスケーラビリティです。Solaris ZFS は、トランザクション型のオブジェクト・モデルに基づいているため、I/Oの発行順序における従来の制約の大半が解消され、パフォーマンスが飛躍的に向上します。さらに、Solaris ZFS は、エラーとして報告されないデータ破損を検出し、修正する 64 bit チェックサム機能であらゆるデータを保護し、データの整合性を維持します。

#### • セキュリティ保護された堅牢なエンタープライズクラス環境

Solaris が何より優れているのは、バイナリ・コンパティビリティを維持している点です。バイナリ・レベルで互換性が維持されていることから、既存の SPARCプラットフォーム上で動作しているアプリケーションをそのままUltraSPARC T2 / UltraSPARC T2 Plusプラットフォーム上へと移植出来るのです。

また、Solaris は、この他にも様々な先進的な機能を備えています。マルチレベルのセキュリティ保護機能、障害の自動検出/分離/修復機能(Fault Management ArchitectureおよびSolaris<sup>TM</sup> Predictive Self Healing)、アプリケーションのチューニング(Solaris<sup>TM</sup> Dtrace: Dynamic Tracing)などです。

#### エンド・ツー・エンドの仮想化テクノロジ

異なるアプリケーションをより強力なシステム上で東ね、使用率を向上させるとともに管理台数を減らし、TCOを低減する、この有力な手段として、今、仮想化テクノロジーに注目が集っています。SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240 は、仮想化テクノロジーが充実したシステムです。プロセッサからメモリ、ネットワーク、I/Oまで、あらゆるレベルできめ細かくリソースを分割することが可能です。しかも、これらの仮想化テクノロジーは、システムの1標準機能として提供されるものであり、利用に際して、追加費用は一切必要ありません。

#### マルチスレッド対応のハイパーバイザー

UltraSPARC T1 プロセッサと同様、UltraSPARC T2/UltraSPARC T2 Plusプロセッサもマルチスレッド対応のハイパーバイザーを実装しています。このハイパーバイザーは、プロセッサに密に統合され、バーチャル・マシンとして機能する軽量のファームウェアです。ハイパーバイザーは、チップ・マルチスレッドに対応し、UltraSPARC T2/UltraSPARC T2 Plusプロセッサと連動し機能します。競合他社とは異なり追加費用が一切必要なく、且つ、オーバーヘッドも小さいハイパーバイザーです。

図 12.テクノロジー・スタックのあらゆるレベルで、並列化と仮想化を行います

図 12のようにハイパーバイザーの上部に仮想化テクノロジーに対応する各レイヤが 構築されています。SPARC Enterpriseの強みは、プロセッサからアプリケーションまで、 アーキテクチャのあらゆるレイヤにおいて完全にマルチスレッド対応していることで す。

Solaris OSは1992 年からマルチスレッド環境に対応しています。このSolaris OSのマルチスレッド化を通して得た知識と経験から、今日の全方位的なエンド・ツー・エンドの並列化と仮想化環境が形作られていると言っても過言ではありません。プロセッサ、ハイパーバイザーのみならずネットワーク、ファイル・システムもマルチスレッド環境に最適化されています。このエンド・ツー・エンドの環境があってこそ、初めてシステム全体でアプリケーション性能をリニアに高めて行くことができるのです。。

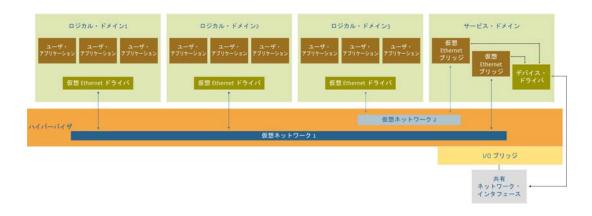

#### ロジカル・ドメイン(LDoms)

マルチスレッドテクノロジーを実装する全てのシステム上で利用可能なロジカル・ドメイン(LDoms)は、CPU/メモリ/ネットワークといったコンピューティング・リソースをハイパーバイザーで抽象化し、分離した動作領域上で異なるオペレーティングシステムを動作させる仮想化テクノロジーの一つです。たとえば、UltraSPARC T2 プロセッサの場合、最大 64 まで動作領域 を分割することができます。各動作領域上では、それぞれ異なるオペレーティング・システムが実行可能です。LDoms は Solaris コンテナをもホスティングします。異なる次元で異なる種類の仮想化テクノロジーを組み合わせることにより、さらに利用率を高めることが可能です。

LDoms は、ハードウェア/ハイパーバイザー/仮想デバイス/ゲスト・ドメイン/コントロール・ドメイン/サービス・ドメインから構成されます。ハイパーバイザは、各ホスティングされたオペレーティングシステムと、ハードウェア間のインタフェースとして機能します。ハイパーバイザーが制御し、サポートするオペレーティングシステムのインスタンスを「ゲスト・ドメイン」と呼びます。ゲスト・ドメインの作成や、制御を目的としたハイパーバイザー/ハードウェア/その他のドメイン間の通信

は、「コントロール・ドメイン」により制御されます。ゲスト・ドメインには、システムとハイパーバイザーをともに制御し、さらに I/O を割り当てる「サービス・ドメイン」から、仮想デバイス・アクセス権が与えられます。

仮想化ネットワークをサポートするため、LDoms は、仮想レイヤ2スイッチを実装します。ゲスト・ドメインは、複数の仮想スイッチ(vswitch)に接続可能であり、複数のゲスト・ドメインを一つの仮想スイッチに接続することも可能です。vswitch は、実際の物理ネットワーク・ポートに対応付けることができます。また、対応するポートがない状態で設定することもできます。この場合、vswitch が行うのは、同一サーバ内のドメイン間通信です。この手法により、ゲスト・ドメインはネットワークとの直接通信チャネルも得られます(図 17)。各ゲスト・ドメインは、NIC 全体と NIC が提供する帯域幅を所有していることになりますが、実際に利用可能なのは、総帯域幅の一部分だけです。したがって、各 NIC を必要に応じて設定し、ドメイン毎に帯域幅を設定することができます。vswitch デバイスを専用の物理 Ethernet ポートに接続することによって専用の帯域幅を利用できます。

図 13. データはロジカル・ドメインと仮想デバイス間を直接移動します。

#### Solaris™コンテナ

OS レベルで仮想化を行う Solaris コンテナは、システム・リソースを効率的に管理し、環境を仮想化し、しかもセキュリティ保護されたアプリケーション実行環境を提供する複数のテクノロジから構成されるものです。Solaris コンテナには、フェア・シェア・スケジューラと連動する重要なテクノロジが組み込まれています。

#### Solaris<sup>TM</sup> Zones

Solaris 10 OS は、Solaris Zonesという独自のパーティショニング・テクノロジーを提供します。Solaris Zonesにより、アプリケーション実行用に分離したセキュリティで保護された環境を作成することが出来ます。ゾーンは、1 つの Solaris OS インスタンス内で生成される仮想化されたオペレーティングシステム環境です。ゾーンにより、アプリケーションとプロセスをシステムの他の部分から分離することが出来ます。こ

の分離は、セキュリティと信頼性の強化に役立ちます。ある特定ゾーンのプロセスが 他のゾーンで実行されているプロセスに影響を与えることはありません。

#### リソース管理

Solaris OS に用意されているリソース・マネージャを使用すると、特定のアプリケーションにCPU などのリソースを割り当てることができます。マルチプロセッサ・システムにおける CPU (UltraSPARC T2/UltraSPARC T2 Plusプロセッサの場合はスレッド)は、論理上、プロセッサ・セットに分割し、リソース・プールにバインドし、そこから Solaris Zonesに割り当てることができます。リソース・プールによって、CPUリソースの消費が重ならないよう、負荷を分散することが可能です。また、プロセッサ・セットとクラス割り当てのスケジューリングに対応する持続的な構成メカニズムも備わっています。さらに、リソース・プールの動的機能により、需要の変化に応じて、システム・リソースを調整することも可能です。

#### 障害管理と予測的セルフヒーリング

Solaris 10 OS には、障害管理と予測的自己修復を可能とする新しい管理アーキテクチャが盛り込まれています。予測的セルフヒーリングは、さまざまなハードウェアおよびアプリケーション障害を自動的に診断し、分離し、回復するSolaris 10 OS の画期的な機能の一つです。これにより、ソフトウェア障害や主要なハードウェア・コンポーネントの障害、ソフトウェアの誤った設定による問題発生時でも、アプリケーションを停止させずにサービスを継続させることが可能となります。

#### • Solaris<sup>TM</sup> Fault Manager

Solaris Fault Manager は、ハードウェアおよびソフトウェア・エラーを自動検出/診断し、エージェントが障害部位をオフラインにするものです。人的な修復作業が必要とされる場合、管理者が対応に迷うことがないよう、診断メッセージは、ナレッジ・ベースとリンクされています。これにより、障害の発生から自動診断を経て、人的介入が完了するまでの時間を大幅に短縮することが出来ます。診断システムそのものの動作を監視することも可能です。

#### • Solaris<sup>TM</sup> Service Manager

Solaris Service Manager は、アプリケーション・サービスに標準的な制御メカニズムをもたらすものです。管理者による誤操作から、プログラムのエラー、ハードウェア障害まで、不測の事態によりサービスが停止してしまった場合、サービスを自動的に再起動します。Solaris Service Manager は、サービス間の依存関係に基づき再起動するので、システムの起動時間を最大75% まで短縮することが出来ます。アプリケーションにシンプルな XML ファイルを追加するだけで、Solaris Service Manager の機能がフル活用出来ますので、導入も容易です。

予測的セルフヒーリングと障害管理により制御可能なSPARC Enterprise T5120/ SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240の主要な機能は以下の通りです。

- CPU オフラインは、動作不安定なコアをオフラインにします。オフライン化されたコアは、リソース・キャッシュに格納され、プロセッサが交換されない限り、リブート後であってもシステムから分離されたままです。プロセッサの交換後、リソース・キャッシュからクリアされます。

- Memory Page Retirement は、障害フラグの付いたメモリ・ページをリタイアさせるものです。ページは、リソース・キャッシュに格納され、部位特定された DIMM が交換されない限り、リブート後であってもシステムから分離されたままです。

DIMM の交換後、リソース・キャッシュからクリアされます。

- I/O Retirement は、エラーと障害を記録します。

- fmlog は、システムが検出した障害を記録します。

#### 第5章 まとめ

データセンターが抱える今日の複合的な課題に応えて行くためには、プロセッサのみならずオペレーティングシステム、ミドルウェア、アプリケーション、そして、管理テクノロジーまで、総合的なアプローチが必要だと考えています。将来の話ではなく、今現在、企業がパフォーマンスとキャパシティのニーズに応えながら、電力とスペース、そして発熱の問題に対処できるソリューションがSPARC Enterpriseにはあります。

UltraSPARC T1プロセッサの後継にあたるUltraSPARC T2 / UltraSPARC T2 Plusプロセッサは、大量のスレッドを処理する業界初の真のシステム・オン・チップ・プロセッサです。従来までシステムレベルで提供されていた10Gigabit Ethernetインタフェース/PCI Express/暗号化処理機能のオンチップ化により、ネットワーク・コンピューティングを支えるプロセッサのあるべき姿を再定義しました。誰もがネットワークを使い、ネットワークを利用する誰もが必要とする機能であれば、標準化すれば良い、皆が使うものは「オプション」ではない、と判断した結果です。

UltraSPARC T2/UltraSPARC T2 Plusプロセッサを搭載したSPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240は、卓越したスループット性能を優れた電力効率、設置効率で発揮するスケーラビリティの高いサーバ・プラットフォームです。限られた設置スペースの中で、処理性能を最大化し、且つ、電力使用量と発熱量を抑える、全てのデータセンターが抱える課題に対する回答です。

卓越したスループット性能を現場で活かして頂くため、SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240には、仮想化テクノロジーが標準機能として備わっています。プロセッサからアプリケーションに至る全包囲的なエンド・ツー・エンドの仮想化テクノロジーとマルチスレッド環境があるからこそ、システム全体でアプリケーション性能をリニアに高めることができるのです。

SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5140/SPARC Enterprise T5240は、ネットワーク上でビジネスを展開する全てお客様に向け、我々が自信を持って提供する卓越したスループット性能を、世界最高水準の設置効率と電力効率で発揮するエコロジーで且つ、エコノミーな次世代プラットフォームです。

#### 詳細情報

富士通製品および SPARC Enterprise T5120/SPARC Enterprise T5220/SPARC Enterprise T5140/SPARC Enterprise T5240に関する詳細は、当社営業または販売パートナーまでお問い合わせいただくか、下記ウェブサイトの関連資料を参照してください。

#### http://primeserver.fujitsu.com/sparcenterprise/

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Limited.

SPARC is a trademark used under license from SPARC International, Inc. of the U.S.A.

Sun, Sun Microsystems, the Sun Logo, Solaris and all Solaris based marks and logos are trademarks or registered trade marks of Sun Microsystems, Inc, in the U.S. and other countries, and are used under license.

SPARC64 is a trademark of Fujitsu Limited under license from SPARC International, Inc. of the U.S.A.

All other company/product names mentioned may be trademarks or registered trademarks of their respective holders and are used for identification purposes only.

# **FUJITSU**