Archived content

NOTE: this is an archived page and the content is likely to be out of date.

Fujitsu’s next generation server technology

Huge Memory Capacity

Fujitsu’s next generation server technology will provide huge memory capacity, 512 GB memory per CPU.

A configuration with a single building block including 4 CPUs will support 2 TB memory size, and a configuration with 16 building blocks will support 32 TB memory size.

Particularly when analyzing Big Data or performing data mining processing, this enormous amount of memory will generate results much faster.

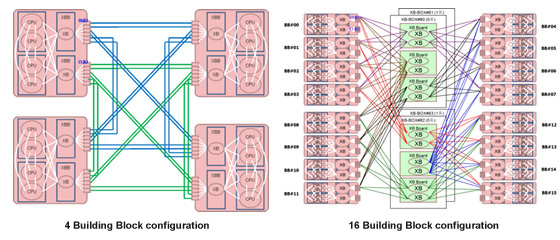

Building Block Architecture

A base unit, referred to as a “Building Block”, will be able to consist of up to 4 CPUs and 2 TB memory size. The Building Block architecture will offer high scalability with the capability to extend from a single building block up to 16 blocks.

Fujitsu’s ultra-high speed interconnect technology will be adopted for the building block connections. This technology will provide high speed transmission at up to 14.5 Gbps between CPUs and building blocks.

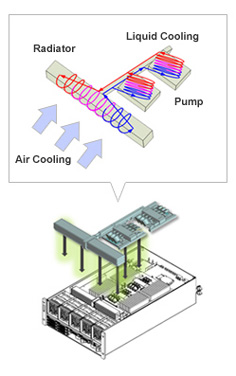

Innovation in Cooling Technology “Liquid Loop Cooling”

The next generation SPARC servers will utilize new “Liquid Loop Cooling” technology, that offers the benefit of both air-cooling and liquid-cooling. With Liquid Loop Cooling, coolant circulates heat from CPUs to the radiator to be air-cooled.

The benefits of this technology are:

- Reduced size of heat-sinks and fans

- Smaller chassis size, less noise

- Improved flexibility of component layout

- Minimized physical distance between CPU and memory

- Suppressed temperature in CPU

- Improved component life

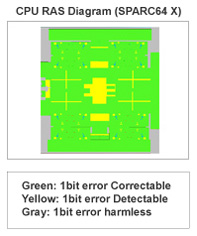

RAS

Fujitsu’s server development incorporates the DNA of over 50 years of mainframe development. Based on this strong heritage, Fujitsu takes pride in the continual improvement of reliability.

As the figure “CPU RAS Diagram” shows, the SPARC64 processor adopts an error detection mechanism and a self-healing mechanism whereby the hardware itself corrects errors in all circuits. The SPARC64 processor is designed to ensure data integrity in almost all areas of the processor, and minimizes the impact on applications if an error occurs.

(NOTE) RAS stands for “Reliability”, “Availability” and “Serviceability”, and consists of features that provide stable system support.

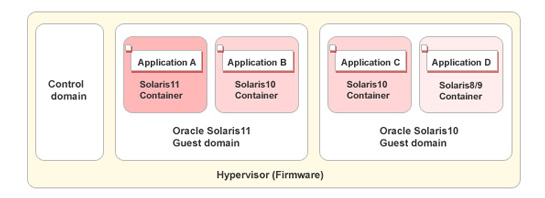

Virtualization Technology “Oracle VM Server for SPARC”

With Oracle VM Server for SPARC, multiple virtual hardware domains can be built at the firmware layer, and operating systems can run on each domain independently. This will allow for rich resources of the next generation server such as CPU, memory and I/O, to be allocated to each domain in a flexible way.

In addition, licensing for Oracle Database in a certain domain will only be required when CPUs are allocated to the domain. This will offer cost advantage since other Virtual Machines require licenses for all CPUs that are installed in the physical server.

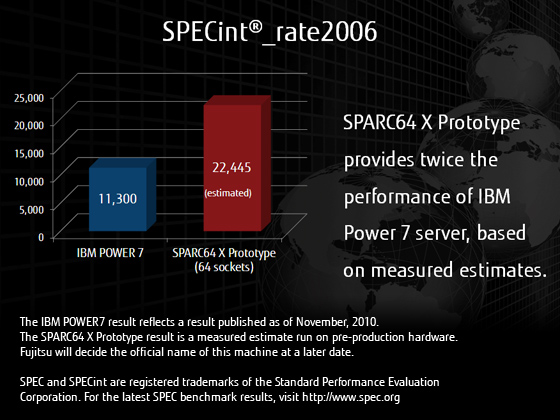

Performance

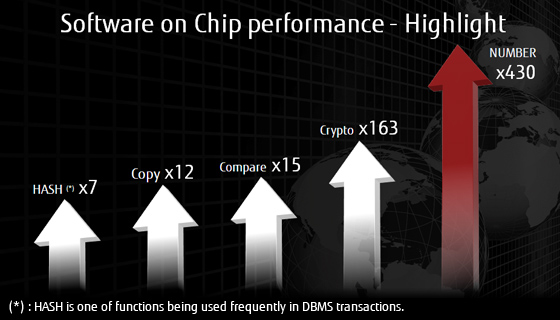

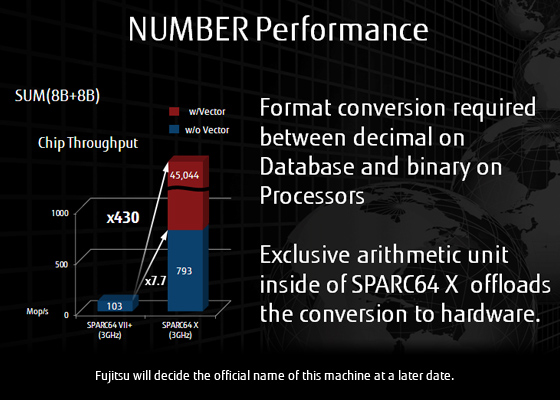

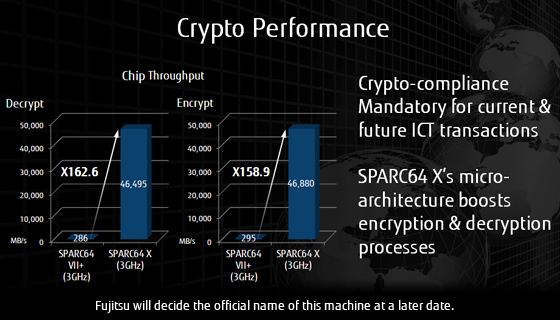

Advanced technologies including Software on Chip in the SPARC64 X processor will provide extreme performance improvements.