# **SPARC Enterprise M-series Servers Architecture**

Architecture Flexible, Mainframe-Class Computer Power

White Paper

Copyright © 2007, 2011, FUJITSU LIMITED. All rights reserved.

Oracle and/or its affiliates provided technical input and review on portions of this material.

Oracle and/or its affiliates and Fujitsu Limited each own or control intellectual property rights relating to products and technology described in this document, and such products, technology and this document are protected by copyright laws, patents, and other intellectual property laws and international treaties.

This document and the product and technology to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of such product or technology, or of this document, may be reproduced in any form by any means without prior written authorization of Oracle and/or its affiliates and Fujitsu Limited, and their applicable licensors, if any. The furnishings of this document to you does not give you any rights or licenses, express or implied, with respect to the product or technology to which it pertains, and this document does not contain or represent any commitment of any kind on the part of Oracle or Fujitsu Limited, or any affiliate of either of them.

This document and the product and technology described in this document may incorporate third-party intellectual property copyrighted by and/or licensed from the suppliers to Oracle and/or its affiliates and Fujitsu Limited, including software and font technology.

Per the terms of the GPL or LGPL, a copy of the source code governed by the GPL or LGPL, as applicable, is available upon request by the End User. Please contact Oracle and/or its affiliates or Fujitsu Limited.

This distribution may include materials developed by third parties.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark of The Open Group in the United States and other countries.

Oracle and Java are registered trademarks of Oracle and/or its affiliates. Fujitsu and the Fujitsu logo are registered trademarks of Fujitsu Limited.

All SPARC trademarks are used under license and are registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon architectures developed by Oracle and/or its affiliates. SPARC64 is a trademark of SPARC International, Inc., used under license by Fujitsu Microelectronics, Inc. and Fujitsu Limited. Other names may be trademarks of their respective owners.

United States Government Rights - Commercial use. U.S. Government users are subject to the standard government user license agreements of Oracle and/or its affiliates and Fujitsu Limited and the applicable provisions of the FAR and its supplements.

Disclaimer: The only warranties granted by Oracle and Fujitsu Limited, and/or any affiliate of either of them in connection with this document or any product or technology described herein are those expressly set forth in the license agreement pursuant to which the product or technology is provided. EXCEPT AS EXPRESSLY SET FORTH IN SUCH AGREEMENT, ORACLE OR FUJITSU LIMITED, AND/OR THEIR AFFILIATES MAKE NO REPRESENTATIONS OR WARRANTIES OF ANY KIND (EXPRESS OR IMPLIED) REGARDING SUCH PRODUCT OR TECHNOLOGY OR THIS DOCUMENT, WHICH ARE ALL PROVIDED AS IS, AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID. Unless otherwise expressly set forth in such agreement, to the extent allowed by applicable law, in no event shall Oracle or Fujitsu Limited, and/or any of their affiliates have any liability to any third party under any legal theory for any loss of revenues or profits, loss of use or data, or business interruptions, or for any indirect, special, incidental or consequential damages, even if advised of the possibility of such damages.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

# **Table of Contents**

| Chapter 1 | Intro | oduction                                       | 1  |

|-----------|-------|------------------------------------------------|----|

| Chapter 2 | SPA   | ARC Enterprise M-series Servers                | 2  |

| 2.1       | Сар   | abilities Overview                             | 3  |

| 2.2       | Entr  | y-Level System — SPARC Enterprise M3000 Server | 6  |

| 2.3       | Midr  | range Systems — SPARC Enterprise M4000 and     |    |

|           | M50   | 000 Servers                                    | 7  |

|           | 2.3.1 | SPARC Enterprise M4000 Server                  | 7  |

|           | 2.3.2 | SPARC Enterprise M5000 Server                  | 7  |

| 2.4       | High  | n-End Systems — SPARC Enterprise M8000 and     |    |

|           | M90   | 000 Servers                                    | 9  |

|           | 2.4.1 | SPARC Enterprise M8000 Server                  | 9  |

|           | 2.4.2 | SPARC Enterprise M9000 Server                  |    |

|           |       | (32 CPU Configuration)                         | 9  |

|           | 2.4.3 | SPARC Enterprise M9000 Server                  |    |

|           |       | (64 CPU configuration)                         | 10 |

| 2.5       | Mee   | ting the Needs of Commercial and Scientific    |    |

|           | Con   | nputing                                        | 12 |

| Chapter 3 | Sys   | tem Architecture                               | 13 |

| 3.1       | Syst  | tem Component Overview                         | 13 |

|           | 3.1.1 | System Interconnect                            | 13 |

|           | 3.1.2 | The SPARC64 VI and SPARC64 VII/VII+            |    |

|           |       | Processors                                     | 14 |

|           | 3.1.3 | Memory                                         | 14 |

|           | 3.1.4 | Memory Mirroring                               | 15 |

|           | 3.1.5 | System Clock                                   | 18 |

|           | 3.1.6 | PCI-Express and PCI-X Technology               | 18 |

|           | 3.1.7 | Service Processor – Extended System Control    |    |

|           |       | Facility                                       | 18 |

|           | 3.1.8 | Power and Cooling                              | 19 |

|           | 3.1.9 | Operator Panel                                 | 21 |

| Chapter 4 | Sys   | tem Bus Architecture — Jupiter Interconnect    | 22 |

| 4.1       | Inte  | rconnect Architecture                          | 22 |

|           | 4.1.1 | SPARC Enterprise M3000 Server Interconnect     |    |

|           |       | Architecture                                   | 22 |

|           | 4.1.2 | SPARC Enterprise M4000 Server Interconnect     |    |

|           |       | Architecture                                   | 23 |

|           | 4.1.3 | SPARC Enterprise M5000 Server Interconnect     |    |

|           |       | Architecture                                   | 24 |

i

|         | 4.1.4   | SPARC Enterprise M8000 and M9000 Servers            |    |

|---------|---------|-----------------------------------------------------|----|

|         |         | Interconnect Architecture                           | 24 |

| 4.2     | 2 Syst  | tem Interconnect Reliability Features               | 26 |

| 4.3     | 3 Scal  | able Performance                                    | 26 |

| Chapter | 5 SPA   | ARC64 VI and SPARC64 VII/VII+ Processors            | 28 |

| 5.1     | l Next  | t-Generation Processor Technology                   | 28 |

|         | 5.1.1   | Chip Multiprocessing (CMT)                          | 28 |

|         | 5.1.2   | Vertical Multithreading (VMT)                       | 29 |

|         | 5.1.3   | Simultaneous Multithreading (SMT)                   | 29 |

| 5.2     | 2 Arch  | nitecture of SPARC64 VII and SPARC64 VII/VII+       |    |

|         | Proc    | cessors                                             | 30 |

|         | 5.2.1   | Cache System                                        | 31 |

|         | 5.2.2   | SPARC64 VI Processor Micro-Architecture             |    |

|         |         | Overview                                            | 32 |

|         | 5.2.3   | SPARC64 VII/VII+ Processor Micro-Architecture       |    |

|         |         | Overview                                            | 33 |

|         | 5.2.4   | SPARC64 VII/VII+ Processors Instruction             |    |

|         |         | Processing                                          | 34 |

|         | 5.2.5   | Instruction Fetch block                             | 35 |

|         | 5.2.6   | Instruction Execution Block                         | 36 |

| 5.3     | 3 Relia | ability, Availability, and Serviceability Functions | 38 |

|         | 5.3.1   | Internal RAM Reliability and Availability Features  | 38 |

|         | 5.3.2   | Internal Registers and Execution Units Reliability  |    |

|         |         | Features                                            | 40 |

|         | 5.3.3   | Synchronous Update Method and Instruction           |    |

|         |         | Retry                                               | 41 |

|         | 5.3.4   | Increased Serviceability                            | 42 |

| Chapter | 6 1/0 9 | Subsystem                                           | 43 |

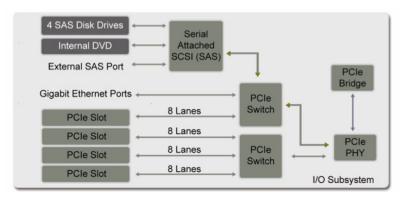

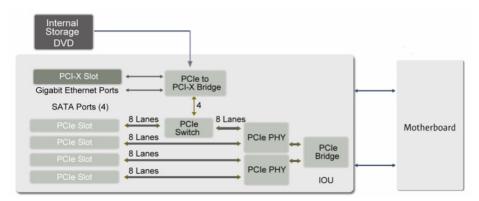

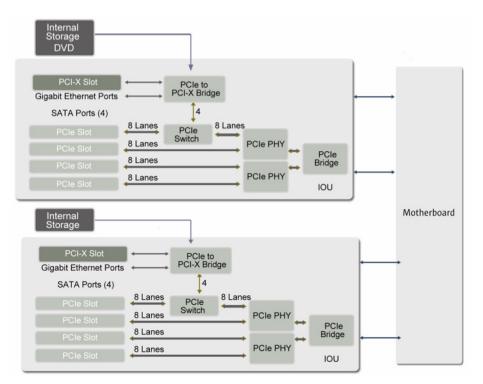

| 6.1     | I I/O 9 | Subsystem Architecture                              | 43 |

|         | 6.1.1   | SPARC Enterprise M3000 Server I/O Subsystem .       | 44 |

|         | 6.1.2   | SPARC Enterprise M4000 and M5000 Servers            |    |

|         |         | I/O Subsystem                                       | 44 |

|         | 6.1.3   | SPARC Enterprise M8000 and M9000 Servers            |    |

|         |         | I/O Subsystem                                       | 46 |

| 6.2     | 2 Inter | rnal Peripherals                                    | 47 |

| 6.3     | B Exte  | ernal I/O Expansion Unit                            | 48 |

| Chapter | 7 Reli  | ability, Availability, and Serviceability           | 50 |

| 7.1     | I Red   | undant and Hot-Swap Components                      | 50 |

| 7.2     | 2 Dyna  | amic Domains                                        | 51 |

|         | 7.2.1   | eXtended System Board (XSB)                         | 51 |

|         | 7.2.2   | Mixed CPU Configurations                            | 55 |

| 7.3        | Dyna  | Dynamic Reconfiguration              |    |  |  |  |

|------------|-------|--------------------------------------|----|--|--|--|

| 7.4        | Adva  | Advanced Reliability Features        |    |  |  |  |

| 7.5        | Erro  | r Detection, Diagnosis, and Recovery | 57 |  |  |  |

| Chapter 8  | Syst  | tem Management                       | 58 |  |  |  |

| 8.1        | Exte  | ended System Control Facility        | 58 |  |  |  |

|            | 8.1.1 | Redundant XSCF                       | 59 |  |  |  |

|            | 8.1.2 | DSCP Network                         | 59 |  |  |  |

|            | 8.1.3 | XSCF Control Package                 | 59 |  |  |  |

|            | 8.1.4 | Role Based System Management         | 60 |  |  |  |

|            | 8.1.5 | Enhanced Support Facility            | 60 |  |  |  |

|            | 8.1.6 | Systemwalker Centric Manager         | 60 |  |  |  |

| Chapter 9  | The   | Oracle Solaris 10                    | 61 |  |  |  |

| 9.1        | Obse  | ervability and Performance           | 61 |  |  |  |

| 9.2        | Avai  | ilability                            | 62 |  |  |  |

| 9.3        | Secu  | urity                                | 64 |  |  |  |

| 9.4        | Virtu | ualization and Resource Management   | 65 |  |  |  |

| Chanter 10 | 0 Sum | nmary                                | 66 |  |  |  |

# 1. Introduction

Organizations now rely on technology more than ever before. Today, compute systems play a critical role in every function from product design to customer order fulfillment. In many cases, business success is dependent on continuous availability of IT services. Once only required in pockets of the datacenter, mainframe-class reliability and serviceability are now essential for systems throughout the enterprise. In addition, powering datacenter servers and keeping services running through a power outage are significant concerns.

While availability is a top priority, costs must also remain in budget and operational familiarity maintained. To deliver networked services as efficiently and economically as possible, organizations look to maximize use of every IT asset through consolidation and virtualization strategies. As a result, modern IT system requirements reach far beyond simple measures of compute capacity. Highly flexible servers are required with built-in virtualization capabilities and associated tools, technologies, and processes that work to optimize sever utilization. New computing infrastructures must also help protect current investments in technology and training.

Fujitsu SPARC Enterprise M-series servers are highly reliable, easy to manage, vertically-scalable systems with many of the benefits of traditional mainframes — without the associated cost, complexity, or vendor lock-in. In fact, these servers deliver a mainframe-class system architecture at open systems prices. With symmetric multiprocessing (SMP) scalability from one to 64 processors, memory subsystems as large as 4 TB, and high-throughput I/O architectures, SPARC Enterprise M-series servers easily perform the heavy lifting required by consolidated workloads. Furthermore, these servers run the powerful Oracle Solaris 10 Operating System (Oracle Solaris 10 OS) and include leading virtualization technologies. By offering Dynamic Domains, eXtended system boards, Dynamic Reconfiguration, and Oracle Solaris Containers technology, SPARC Enterprise M-series servers bring sophisticated mainframe-class resource control to an open systems compute platform \*1.

1

<sup>\*1:</sup>SPARC Enterprise M3000 server do not support Dynamic Domains, eXtended system boards, and Dynamic Reconfiguration capabilities.

# 2. SPARC Enterprise M-series Servers

Massive compute power, a resilient system architecture, flexible resource control features, and the advanced capabilities of Oracle Solaris 10 combine in SPARC Enterprise servers to provide organizations a best-in-class enterprise platform. As an added benefit, SPARC Enterprise M-series servers (Figure 2-1) also offer improved performance over previous generations of Fujitsu servers, with a clear upgrade path that protects existing investments in software, training, and datacenter practices. By taking advantage of SPARC Enterprise servers, IT organizations can create a more powerful infrastructure, optimize hardware utilization, and increase application availability — resulting in lower operational cost and risk.

Figure 2-1. The SPARC Enterprise M-series servers provide organizations with scalable power, reliability, and flexibility.

## 2.1 Capabilities Overview

The members of the SPARC Enterprise server family share many of the same characteristics that foster power, reliability, and flexibility. SPARC Enterprise servers feature a balanced, highly scalable SMP design that utilizes the latest generation of SPARC64 processors connected to memory and I/O by a new high-speed, low latency system interconnect that delivers exceptional throughput to applications. Also architected to reduce planned and unplanned downtime, these servers include stellar reliability, availability, and serviceability capabilities to avoid outages and reduce recovery time. Design features such as advanced CPU integration and data path integrity, memory extended ECC and memory mirroring, end-to-end data protection, hot-swappable components, fault resilient power options, and hardware redundancy boost the reliability of these servers.

SPARC Enterprise M4000, M5000, M8000, and M9000 servers also provide unmatched configuration flexibility. As in other Fujitsu high-end servers, administrators can use Dynamic Domains to physically divide a single SPARC Enterprise M4000, M5000, M8000, and M9000 servers into multiple electrically isolated partitions, each running independent instances of Oracle Solaris. Hardware or software failures in one Dynamic Domain do not affect applications running in other domains, unless the failed resource is shared across both domains.

Dynamic Reconfiguration can then reallocate hardware resources among Dynamic Domains — without interrupting critical systems. SPARC Enterprise servers advance resource control one-step further with eXtended System Board (XSB) technology, supporting the allocation of sub-system board resources such as CPUs, memory, and I/O components to Dynamic Domains. The fine-grain resource control provided by eXtended System Board technology helps enterprises to further optimize resource utilization.

Adding even more value, the range of compute power offered by the SPARC Enterprise server family provides the levels of vertical scalability required for many deployment classes, letting organizations match the right system to the task. Rackmount SPARC Enterprise M3000 server is the entry-level server that has many characteristics of SPARC Enterprise servers, and shares benefits such as operability and manageability common to the servers. The server combines high performance, high quality, and ecological sustainability with a resilient system architecture, the advanced functions of the Solaris 10 OS, a compact form factor (2U in a rack cabinet), and the top CPU power in the entry-level class of servers.

Rackmount SPARC Enterprise M4000 and M5000 servers are economical, powerful, and reliable servers well-suited for entry-level and mid-range system requirements (Table 2-1). SPARC Enterprise M8000 and M9000 servers deliver the massive processing power needed for high-end computing (Table 2-2).

Table 2-1. Characteristics of SPARC Enterprise M3000, M4000, and M5000 servers

|                                  | SPARC Enterprise SPARC Enterprise M3000 server M4000 server                                                     |                                                                                                                                       | SPARC Enterprise<br>M5000 server                                                                                                        |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Enclosure                        | • 2 rack units                                                                                                  | • 6 rack units                                                                                                                        | • 10 rack units                                                                                                                         |

| SPARC64 VI<br>Processors         | • N/A                                                                                                           | <ul><li>2.15 GHz</li><li>5 MB L2 cache</li><li>Up to four dual-core chips</li></ul>                                                   | <ul><li>2.15 GHz</li><li>5 MB L2 cache</li><li>Up to eight dual-core chips</li></ul>                                                    |

| SPARC64 VII<br>Processors        | <ul> <li>2.52 GHz/2.75 GHz</li> <li>5 MB L2 cache</li> <li>One CPU chip<br/>(quad-core or dual-core)</li> </ul> | <ul> <li>2.4 GHz with 5 MB<br/>L2 cache</li> <li>2.53 GHz with<br/>5.5 MB L2 cache</li> <li>Up to four<br/>quad-core chips</li> </ul> | <ul> <li>2.4 GHz with 5 MB<br/>L2 cache</li> <li>2.53 GHz with<br/>5.5 MB L2 cache</li> <li>Up to eight quad-<br/>core chips</li> </ul> |

| SPARC64 VII+<br>Processors       | <ul> <li>2.86 GHz with</li> <li>5.5 MB L2 cache</li> <li>One CPU chip<br/>(quad-core or dual-core)</li> </ul>   | <ul><li>2.66 GHz with<br/>11 MB L2 cache</li><li>Up to four<br/>quad-core chips</li></ul>                                             | <ul> <li>2.66 GHz with</li> <li>11 MB L2 cache</li> <li>Up to eight quad-<br/>core chips</li> </ul>                                     |

| Memory                           | <ul><li> Up to 64 GB</li><li> 8 DIMM slots</li></ul>                                                            | <ul><li>Up to 256 GB</li><li>32 DIMM slots</li></ul>                                                                                  | <ul><li> Up to 512 GB</li><li> 64 DIMM slots</li></ul>                                                                                  |

| Internal I/O<br>Slots            | • Four PCI Express                                                                                              | <ul><li>Four PCI Express</li><li>One PCI eXtended</li></ul>                                                                           | <ul><li>Eight PCI Express</li><li>Two PCI eXtended</li></ul>                                                                            |

| External I/O<br>Chassis          | • N/A                                                                                                           | • Up to two units                                                                                                                     | • Up to four units                                                                                                                      |

| External<br>Onboard<br>Interface | <ul><li>4 Gigabit Ethernet ports</li><li>SAS port</li></ul>                                                     | • 2 Gigabit Ethernet ports                                                                                                            | • 2 Gigabit Ethernet ports per IOU                                                                                                      |

| Internal<br>Storage              | <ul><li>Serial Attached<br/>SCSI</li><li>Up to four drives</li></ul>                                            | <ul><li>Serial Attached<br/>SCSI</li><li>Up to two drives</li></ul>                                                                   | <ul><li>Serial Attached<br/>SCSI</li><li>Up to four drives</li></ul>                                                                    |

| Dynamic<br>Domains               | • One                                                                                                           | • Up to two                                                                                                                           | • Up to four                                                                                                                            |

Table 2-2. Characteristics of SPARC Enterprise M8000, M9000-32, and M9000-64 servers

|                                  | SPARC Enterprise<br>M8000 server                                                                                                  | SPARC Enterprise<br>M9000 server<br>(32 CPU configuration)                                                                        | SPARC Enterprise<br>M9000 server<br>(64 CPU configuration)                                                                        |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Enclosure                        | One cabinet                                                                                                                       | One cabinet                                                                                                                       | Two cabinets                                                                                                                      |  |  |

| SPARC64 VI<br>Processors         | <ul> <li>2.28 GHz with 5 MB<br/>L2 cache</li> <li>2.4 GHz with 6 MB<br/>L2 cache</li> <li>Up to 16<br/>dual-core chips</li> </ul> | <ul> <li>2.28 GHz with 5 MB<br/>L2 cache</li> <li>2.4 GHz with 6 MB<br/>L2 cache</li> <li>Up to 32<br/>dual-core chips</li> </ul> | <ul> <li>2.28 GHz with 5 MB<br/>L2 cache</li> <li>2.4 GHz with 6 MB<br/>L2 cache</li> <li>Up to 64<br/>dual-core chips</li> </ul> |  |  |

| SPARC64 VII<br>Processors        | <ul><li>2.52 GHz/2.88 GHz</li><li>6 MB L2 cache</li><li>Up to 16 quad-core chips</li></ul>                                        | <ul><li>2.52 GHz/2.88 GHz</li><li>6 MB L2 cache</li><li>Up to 32 quad-core chips</li></ul>                                        | <ul><li>2.52 GHz/2.88 GHz</li><li>6 MB L2 cache</li><li>Up to 64<br/>quad-core chips</li></ul>                                    |  |  |

| SPARC64 VII+<br>Processors       | <ul> <li>3.0 GHz with 12 MB<br/>L2 cache</li> <li>Up to 16<br/>quad-core chips</li> </ul>                                         | <ul> <li>3.0 GHz with 12 MB<br/>L2 cache</li> <li>Up to 32<br/>quad-core chips</li> </ul>                                         | <ul> <li>3.0 GHz with 12 MB<br/>L2 cache</li> <li>Up to 64<br/>quad-core chips</li> </ul>                                         |  |  |

| Memory                           | <ul><li> Up to 1 TB</li><li> 128 DIMM slots</li></ul>                                                                             | <ul><li>Up to 2 TB</li><li>256 DIMM slots</li></ul>                                                                               | <ul><li>Up to 4 TB</li><li>512 DIMM slots</li></ul>                                                                               |  |  |

| Internal I/O<br>Slots            | • 32 PCI Express                                                                                                                  | • 64 PCI Express                                                                                                                  | • 128 PCI Express                                                                                                                 |  |  |

| External I/O<br>Chassis          | • Up to 8 units                                                                                                                   | • Up to 16 units                                                                                                                  | • Up to 16 units                                                                                                                  |  |  |

| External<br>Onboard<br>Interface | • Gigabit Ethernet ports per IOUA*a                                                                                               | • Gigabit Ethernet ports per IOUA*a                                                                                               | • 2 Gigabit Ethernet ports per IOUA*a                                                                                             |  |  |

| Internal<br>Storage              | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 16 drives</li></ul>                                                                | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 32 drives</li></ul>                                                                | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 64 drives</li></ul>                                                                |  |  |

| Dynamic<br>Domains               | • Up to 16                                                                                                                        | • Up to 24                                                                                                                        | • Up to 24                                                                                                                        |  |  |

<sup>\*</sup>a:IOUA is an optional card.

# 2.2 Entry-Level System — SPARC Enterprise M3000 Server

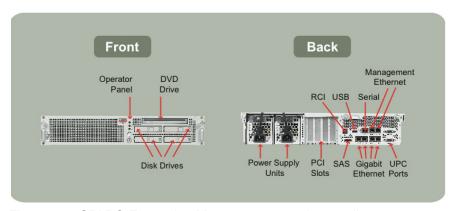

The SPARC Enterprise M3000 server enclosure measures two rack-units (RU) and supports one processor chip and up to 64 GB of memory. The SPARC64 VII/VII+ (dual-core or quad-core) processor chip is mounted on the motherboard. The I/O subsystem of the SPARC Enterprise M3000 server features four short internal PCI Express slots, four internal disk drives, one internal DVD drive, and an external SAS port for attaching external storage or tape device units. Two power supplies and two fan units power and cool the server. Front and rear views of the SPARC Enterprise M3000 server are found in Figure 2-2.

Figure 2-2. SPARC Enterprise M3000 server enclosure diagram.

## 2.3 Midrange Systems — SPARC Enterprise M4000 and M5000 Servers

SPARC Enterprise M4000 and M5000 servers are economical, high-power compute platforms with enterprise-class features. These midrange servers are designed to reliably carry datacenter workloads that support core business operations.

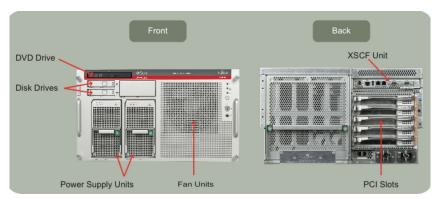

#### 2.3.1 SPARC Enterprise M4000 Server

The SPARC Enterprise M4000 server enclosure measures six rack-units (RU) and supports up to four processor chips, 256 GB of memory, and up to two Dynamic Domains. In addition, the SPARC Enterprise M4000 server features four short internal PCI Express slots and one short internal PCI-X slot, as well as two disk drives, one DVD drive, and an optional DAT tape drive. Two power supplies and four fan units power and cool the SPARC Enterprise M4000 server. Front and rear views of the SPARC Enterprise M4000 server are found in Figure 2-3.

Figure 2-3. SPARC Enterprise M4000 server enclosure diagram.

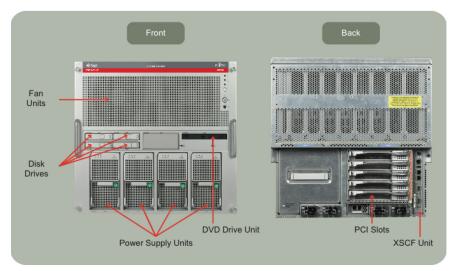

#### 2.3.2 SPARC Enterprise M5000 Server

The SPARC Enterprise M5000 server enclosure measures 10 RU and supports up to eight processor chips, 512 GB of memory, and up to four Dynamic Domains. In addition, the SPARC Enterprise M5000 server features eight short internal PCI Express and two short internal PCI-X slots, as well as four disk drives, one DVD drive, and an optional DAT tape drive. Four power supplies and four fan units power and cool the SPARC Enterprise M5000 server. Front and rear views of the SPARC Enterprise M5000 server are found in Figure 2-4.

Figure 2-4. SPARC Enterprise M5000 server enclosure diagram.

# 2.4 High-End Systems — SPARC Enterprise M8000 and M9000 Servers

High-end SPARC Enterprise servers are designed to deliver outstanding performance for even the most challenging workloads. By merging mainframe reliability, advanced performance technology often used in supercomputers, and an open systems environment, these servers help organizations create reliable, high-throughput, flexible solutions.

#### 2.4.1 SPARC Enterprise M8000 Server

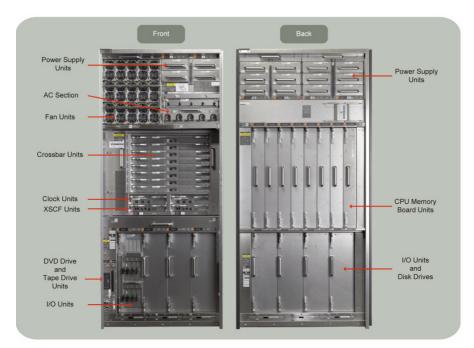

The SPARC Enterprise M8000 server is mounted in an enterprise system cabinet and supports up to four CPU Memory Units (CMU) and four I/O Units (IOU). Fully configured, the SPARC Enterprise M8000 server houses 16 processor chips, 1 TB of memory, 32 short internal PCI Express slots, and can be divided into 16 Dynamic Domains. In addition, the SPARC Enterprise M8000 server supports up to 16 disk drives, one DVD drive, and an optional DAT tape drive. Nine power supplies and 12 fan units power and cool the SPARC Enterprise M8000 server. Front and rear views of the SPARC Enterprise M8000 server are found in Figure 2-5.

Figure 2-5. SPARC Enterprise M8000 server enclosure diagram.

#### 2.4.2 SPARC Enterprise M9000 Server (32 CPU Configuration)

The SPARC Enterprise M9000 server (32 CPU configuration) mounts in an enterprise system cabinet and supports up to eight CMUs and eight IOUs. Fully configured, the SPARC Enterprise M9000 server (32 CPU configuration) houses 32 processor chips, 2 TB of memory, 64 short internal PCI Express slots, and can be divided into 24 Dynamic

Domains. In addition, the SPARC Enterprise M9000 server (32 CPU configuration) supports up to 32 disk drives, one DVD drive, and an optional DAT tape drive. Power and cooling for the SPARC Enterprise M9000 server (32 CPU configuration) is provided by 15 power supplies and 16 fan units. Front and rear views of the SPARC Enterprise M9000 server (32 CPU configuration) are found in Figure 2-6.

Figure 2-6. SPARC Enterprise M9000 server (32 CPU configuration) enclosure diagram.

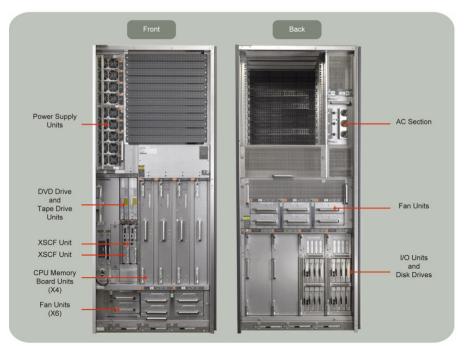

#### 2.4.3 SPARC Enterprise M9000 Server (64 CPU configuration)

An expansion cabinet can be added to an existing base cabinet to create the SPARC Enterprise M9000 server (64 CPU configuration), supporting up to 16 CMUs and 16 IOUs. Fully configured, the SPARC Enterprise M9000 server (64 CPU configuration) houses 64 processor chips, 4 TB of memory, 128 short internal PCI Express slots, and can be divided into 24 Dynamic Domains. In addition, the SPARC Enterprise M9000 server (64 CPU configuration) supports up to 64 disk drives two DVD drives, and two optional DAT tape drives. The SPARC Enterprise M9000 server (64 CPU configuration) utilizes 30 power supplies and 32 fan units for power and cooling. A front of the SPARC Enterprise M9000 server (64 CPU configuration) is found in Figure 2-7.

Figure 2-7. SPARC Enterprise M9000 server (64 CPU configuration) enclosure diagram.

# 2.5 Meeting the Needs of Commercial and Scientific Computing

Suiting a wide range of computing environments, SPARC Enterprise M-series servers provide the availability features needed to support commercial computing workloads along with the raw performance demanded by high performance computing (HPC) (Table 2-3).

Table 2-3. The power and flexibility of SPARC Enterprise servers benefit a broad range of enterprise applications.

| SPARC Enterprise M3000, M4000, and M5000 servers                                                                                                                                                                                                                                          | SPARC Enterprise M8000 and M9000 servers                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Server consolidation</li> <li>Business processing (ERP, CRM, OLTP, Batch)</li> <li>Database</li> <li>Decision support</li> <li>Datamart</li> <li>Web services</li> <li>System and network management</li> <li>Application development</li> <li>Scientific engineering</li> </ul> | <ul> <li>Server consolidation</li> <li>Business processing (ERP, CRM, OLTP, Batch)</li> <li>Database</li> <li>Decision support</li> <li>Data warehouses</li> <li>IT infrastructure</li> <li>Application serving</li> <li>Compute-intensive scientific engineering</li> </ul> |

# 3. System Architecture

Continually challenged by growing workloads and demands to do more with less, IT organizations realize that meeting processing requirements with fewer, more powerful systems can provide economic advantages. In SPARC Enterprise M-series servers the interconnect, processors, memory subsystem, and I/O subsystem work together to create a scalable, high-performance platform ready to address server consolidation needs. By taking advantage of these servers, organizations can load multiple projects onto a single platform and accelerate application execution at lower costs.

#### 3.1 System Component Overview

The design of SPARC Enterprise servers specifically focuses on delivering high reliability, outstanding performance, and true SMP scalability. The characteristics and capabilities of every subsystem within these servers work toward this goal. A high-bandwidth system bus, powerful SPARC64 VI and SPARC64 VII/VII+ processors, dense memory option, and fast PCI Express (PCIe), and PCI eXtended (PCI-X) expansion slots combine within these servers to deliver high levels of uptime and throughput, as well as dependable scaling for enterprise applications.

#### 3.1.1 System Interconnect

Based on mainframe technology, the Jupiter system interconnect fosters high level of performance, scalability and reliability for SPARC Enterprise M-series servers. A single system controller within SPARC Enterprise M3000 servers and multiple system controllers and crossbar units within SPARC Enterprise M4000, M5000, M8000, and M9000 servers provide point-to-point connections between CPU, memory, and I/O subsystems. Offering more than one bus route between components enhances performance and allows system operation to continue in the event of a faulty switch. Indeed, the system interconnect used in these servers delivers as much as 737 GB/second of peak bandwidth, offering 5.5x more system throughput than Fujitsu's previous generation of high-end servers. Additional technical details for the system interconnect on each SPARC Enterprise server are found in *Chapter 3 – System Bus Architecture*.

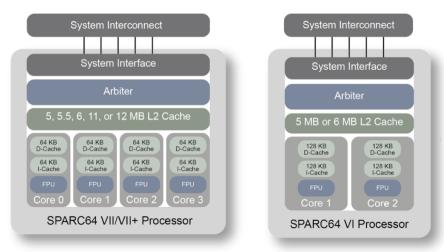

#### 3.1.2 The SPARC64 VI and SPARC64 VII/VII+ Processors

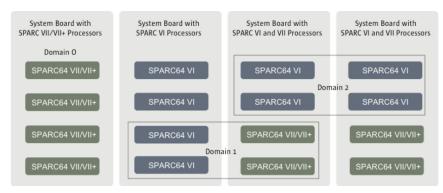

SPARC Enterprise M3000 servers support SPARC64 VII and VII+ processors while the SPARC Enterprise M4000, M5000, M8000, and M9000 servers can utilize SPARC64 VI and SPARC64 VII/VII+ processor developed by Fujitsu. The design of the multi-core, multithreaded SPARC64 VI and SPARC64 VII/VII+ processors are based on several decades of experience in creating mainframe systems that achieve high levels of reliability and performance. SPARC64 VI dual-core, multithreaded processor takes advantage of 90 nm technologies while the SPARC64 VII/VII+ processor provides a quad-core implementation with a faster clock speed and a reduction in size using 65 nm fabrication. Both processors execute at a power consumption level below 150 W. Moreover the SPARC Enterprise M4000, M5000, M8000, and M9000 servers increase flexibility and maintain investment protection by supporting configurations that can mix SPARC64 VI and SPARC64 VII/VII+ processors within the same system board or the same Dynamic Domain. Additional technical details about the SPARC64 processors are found in *Chapter 4 – SPARC64 VI/SPARC64 VII/SPARC64 VII-Processors*.

#### 3.1.3 Memory

The memory subsystem of SPARC Enterprise M-series servers increase the scalability and throughput of these systems. In fact, the SPARC Enterprise M9000 server accommodates up to 4 TB of memory. SPARC Enterprise M3000 server support DDR-II DIMMs with 2-way memory interleave. SPARC Enterprise M4000, M5000, M8000, and M9000 servers use DDR-II DIMM with 8-way memory interleave to enhance system performance. While multiple DIMM sizes are not supported within a single bank, DIMM capacities can vary across system boards. Available DIMM sizes include 1 GB, 2 GB, 4 GB, and 8 GB densities. Further details about the memory subsystem are described in Table 3-1.

Table 3-1. SPARC Enterprise server memory subsystem specifications.

|                               | E<br>M | PARC<br>nterprise<br>I3000<br>erver | Er<br>M | PARC<br>nterprise<br>4000<br>rver | Er<br>M | PARC<br>nterprise<br>5000<br>rver | Eı<br>M | PARC<br>nterprise<br>8000<br>rver | E1 M (3 | PARC<br>nterprise<br>9000 server<br>2 CPU<br>onfiguration) | E1<br>M<br>(6 | 4 CPU     |

|-------------------------------|--------|-------------------------------------|---------|-----------------------------------|---------|-----------------------------------|---------|-----------------------------------|---------|------------------------------------------------------------|---------------|-----------|

| Maximum<br>Memory<br>Capacity | •      | 64 GB                               | •       | 256 GB                            | •       | 512 GB                            | •       | 1 TB                              | •       | 2 TB                                                       | •             | 4 TB      |

| DIMM<br>slots                 | •      | 8                                   | •       | 32                                | •       | 64                                | •       | Up to 128                         | •       | Up to 256                                                  | •             | Up to 512 |

| Bank Size                     | •      | 4 DIMMs                             | •       | 4 DIMMs                           | •       | 4 DIMMs                           | •       | 8 DIMMs                           | •       | 8 DIMMs                                                    | •             | 8 DIMMs   |

| Number of Banks               | •      | 2                                   | •       | 8                                 | •       | 16                                | •       | Up to 16                          | •       | Up to 32                                                   | •             | Up to 64  |

Beyond performance, the memory subsystem of SPARC Enterprise servers are built with reliability in mind. ECC protection is implemented for all data stored in main memory, and the following advanced features foster early diagnosis and fault isolation that preserve system integrity and raise application availability.

- Memory patrol Memory patrol periodically scans memory for errors. This proactive

function prevents the use of faulty areas of memory before they can cause system or

application errors, improving system reliability.

- Memory Extended ECC The memory Extended ECC function of these servers

provides single-bit error correction, supporting continuous processing despite events

such as burst read errors that are sometimes caused by memory device failures. This

feature is similar to IBM's Chipkill technology.

#### 3.1.4 Memory Mirroring

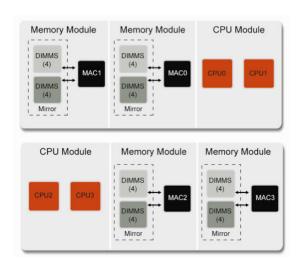

SPARC Enterprise M4000, M5000, M8000, and M9000 servers support memory mirroring capabilities. Memory mirroring is an optional, high-availability feature appropriate for execution of applications with the most stringent availability requirements. When memory mirroring mode is enabled on SPARC Enterprise M4000, M5000, M8000, and M9000 servers, the memory subsystem duplicates the data on write and compares the data on read to each side of the memory mirror. In the event that errors occur at the bus or DIMM level, normal data processing continues through the other memory bus and alternate DIMM set. In SPARC Enterprise M4000 and M5000 servers, memory is mirrored within the same memory module, using the common memory address controller (MAC) Application Specific Integrated Circuit (ASIC) (Figure 3-1 and Figure 3-2).

Figure 3-1. SPARC Enterprise M4000 server memory mirroring architecture.

Figure 3-2. SPARC Enterprise M5000 server memory mirroring architecture.

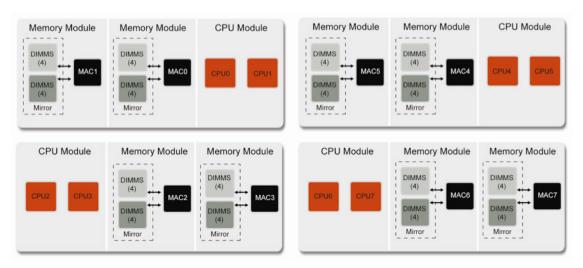

On SPARC Enterprise M8000 and M9000 servers, memory is mirrored across adjacent MAC ASICs to increase reliability (Figure 2-5). However, in a Quad-XSB configuration, paired DIMMs are split across different SPARC Enterprise M8000 and M9000 servers Quad-XSBs. As such, memory mirroring is not supported on a Quad-XSB configuration.

Figure 3-3. SPARC Enterprise M8000 and M9000 servers memory mirroring architecture.

#### 3.1.5 System Clock

While the implementation of the system clock varies with the member of the SPARC Enterprise M-series servers each server is engineered with reliability in mind. In particular, SPARC Enterprise M8000 server clock chip is built with redundant internal components. Further enhancing availability and easing maintenance, the SPARC Enterprise M9000 server also implements two sources of clock signal and a dual signal source synchronous line exists between the clock chip and the system boards. In the event one route fails, the system can be restarted via the other route.

#### 3.1.6 PCI-Express and PCI-X Technology

SPARC Enterprise M-series servers use a PCI bus to provide high-speed data transfer within the I/O subsystem. In order to support PCI Express expansion cards, SPARC Enterprise M-series use a PCI Express physical layer (PCIe PHY) ASIC to manage the implementation of the PCI Express protocol. PCI Express technology doubles the peak data transfer rates of original PCI technology and reaches 2.5 Gb/second of throughput. In fact, PCI Express was developed to accommodate high-speed interconnects such as Fibre Channel, Infiniband, and Gigabit Ethernet. SPARC Enterprise M4000, M5000, M8000, and M9000 servers also support PCI-X expansion cards for fast access to external devices. PCI-X is backward compatible with existing PCI cards, but increases bandwidth enabling data transfer of up to 1 GB/second for 64-bit devices. Additional technical details for SPARC Enterprise server I/O subsystems can be found in *Chapter 5 – I/O Subsystem*.

#### 3.1.7 Service Processor – Extended System Control Facility

Simplifying management of compute systems leads to higher availability levels for hosted applications. With this in mind, SPARC Enterprise M-series servers include an eXtended System Control Facility (XSCF). The XSCF consists of a dedicated processor that is independent of the server and runs the XSCF Control Package (XCP) to provide remote monitoring and management capabilities. This service processor regularly monitors environmental sensors, provides advanced warning of potential error conditions, and executes proactive system maintenance procedures as necessary. Indeed, while power is supplied to the server, the XSCF constantly monitors the platform even if the system is inactive. XCP facilitates Dynamic Domains configuration, audit administration, hardware control capabilities, hardware status monitoring, reporting, and handling, automatic diagnosis and domain recovery, capacity on demand operations, and XSCF failover services. Additional technical details about the XSCF and XCP are found in *Chapter 7 – System Management*.

#### 3.1.8 Power and Cooling

SPARC Enterprise M-series servers use separate modules for power and cooling. Sensors placed throughout the system measure temperatures on processors and key ASICS as well as the ambient temperature at several location. Hardware redundancy in the power and cooling subsystems combined with environmental monitoring keep servers operating even under power or fan fault conditions.

#### 3.1.8.1 Fan Unit

Fully redundant, hot-swap fans function as the primary cooling system for SPARC Enterprise M-series servers (Table 3-2 and Table 3-3). If a single fans fails, the XSCF detects the failure and switches the remaining fans to high-speed operation to compensate for the reduced airflow. SPARC Enterprise M-series servers can operate normally under these conditions, allowing ample time to service the failed unit. Replacement of fans units can occur without interrupting application processing.

#### 3.1.8.2 Power Supply

The use of redundant power supplies and power cords adds to the fault resilience of SPARC Enterprise M-series servers (Table 3-2 and Table 3-3). Power is supplied by redundant hot-swap power supplies, helping to support continued server operation even if a power supply fails. Since the power units are hot-swappable, removal and replacement can occur while the system continues to operate.

As an option, SPARC Enterprise M8000 and M9000 servers can be ordered with a three-phase power supply unit and corresponding server cabinet. Models with a three-phase power supply permit two configurations, a star connection that connects a neutral line and each phase, and a delta connection that connects each phase.

Table 3-2. SPARC Enterprise M3000, M4000, and M5000 servers power and cooling specifications.

|                | SPARC Enterprise<br>M3000 server                                                                                                                          | SPARC Enterprise<br>M4000 server                                                                                           | SPARC Enterprise<br>M5000 server                                                                                                                             |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fan Units      | <ul> <li>Two fan units</li> <li>Two 80 mm fans</li> <li>Two 60 mm fans</li> <li>1+1 redundant</li> </ul>                                                  | <ul> <li>Four fan units</li> <li>Two 172 mm fans</li> <li>Two 60 mm fans</li> <li>One of each type is redundant</li> </ul> | <ul> <li>Four fan units</li> <li>Four 172 mm fans</li> <li>Two fan groups, each containing two fan units</li> <li>One redundant fan per fan group</li> </ul> |  |

| Power Supplies | <ul> <li>AC: 505 W,<br/>DC: 510 W (2.86 GHz) (max)</li> <li>Two units</li> <li>1+1 redundant</li> <li>Single-phase AC or<br/>DC power supplies</li> </ul> | <ul> <li>1,692 W (2.66 GHz) (max)</li> <li>Two units</li> <li>1+1 redundant</li> <li>Single-phase</li> </ul>               | <ul> <li>1,692 W (2.66 GHz) (max)</li> <li>Four units</li> <li>2+2 redundant</li> <li>Single-phase</li> </ul>                                                |  |

| Power Cords    | <ul><li>Two power cables</li><li>1+1 redundant power cables</li></ul>                                                                                     | <ul><li>Two power cables</li><li>1+1 redundant<br/>power cables</li></ul>                                                  | <ul><li>Four power cables</li><li>2+2 redundant<br/>power cables</li></ul>                                                                                   |  |

Table 3-3. SPARC Enterprise M8000 and M9000 servers power and cooling specifications.

|                | SPARC Enterprise<br>M8000 server                                                                                           | SPARC Enterprise<br>M9000 server<br>(32 CPU configuration)                                                                  | SPARC Enterprise<br>M9000 server<br>(64 CPU<br>configuration)                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Fan Units      | <ul><li>12 fan units</li><li>Four 172 mm fans</li><li>Eight 60 mm fans</li><li>N+1 redundant</li></ul>                     | <ul><li>16 fan units</li><li>16 172 mm fans</li><li>N+1 redundant</li></ul>                                                 | <ul><li>32 fan units</li><li>32 172 mm fans</li><li>N+1 redundant</li></ul>                                                  |

| Power Supplies | <ul> <li>10,500 W (3.0 GHz) (max)</li> <li>9 units</li> <li>N+1 redundant</li> </ul>                                       | <ul> <li>20,220 W (3.0 GHz) (max)</li> <li>15 units</li> <li>N+1 redundant</li> </ul>                                       | <ul> <li>40,440 W (3.0 GHz) (max)</li> <li>30 units</li> <li>N+1 redundant</li> </ul>                                        |

| Options        | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>                                                       | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>                                                        | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>                                                         |

| Power Cords    | <ul> <li>3 power cables (single feed)</li> <li>6 power cables (dual feed)</li> <li>2 power cables (three-phase)</li> </ul> | <ul> <li>5 power cables (single feed)</li> <li>10 power cables (dual feed)</li> <li>2 power cables (three-phase)</li> </ul> | <ul> <li>10 power cables (single feed)</li> <li>20 power cables (dual feed)</li> <li>4 power cables (three-phase)</li> </ul> |

#### 3.1.8.3 Optional Dual Power Feed

While organizations can control most factors within the datacenter, utility outages are often unexpected. The consequences of loss of electrical power can be devastating to IT operations. In order to help reduce the impact of such incidents, SPARC Enterprise M-series are dual power feed capable. The AC power subsystem in these servers is completely duplicated, providing optional reception of power from two external and independent AC power sources. The use of a dual power feed and redundant power supplies increases system availability, as server operations can remain unaffected even after a single power grid failure.

#### 3.1.9 Operator Panel

SPARC Enterprise M-series servers feature an operator panel to display server status, store server identification and user setting information, change between operational and maintenance modes, and turn on power supplies for domains (Figure 3-4). During server startup, the front panel LED status indicators verify XSCF and server operation.

Figure 3-4. The SPARC Enterprise server operator panel.

# System Bus Architecture — Jupiter Interconnect

High end systems containing dozens of CPUs only provide scalability if all processors are able to actually contribute to the performance of the application. The ability to deliver near-linear scalability and fast, predictable performance for a broad set of applications rests largely on the capabilities of the system bus. SPARC Enterprise M-series servers utilize a system interconnect designed to deliver massive bandwidth and consistent, low latency between components. The Jupiter system bus benefits IT operations by delivering balanced and predictable performance to application workloads.

#### 4.1 Interconnect Architecture

The Jupiter interconnect design maximizes the overall performance of SPARC Enterprise M-series servers. Implemented as point-to-point connections that utilize packet-switched technology, this system bus provides fast response times by transmitting multiple data streams. Packet-switching allows the interconnect to operate at much higher system-wide throughput by eliminating "dead" cycles on the bus. All routes are uni-directional, noncontentious paths with multiplexed address, data, and control plus ECC in each direction.

System controllers within the interconnect architecture on all SPARC Enterprise M4000, M5000, M8000, and M9000 servers direct traffic between local CPUs, memory, I/O subsystems, and interconnect paths. On SPARC Enterprise M8000 and M9000 servers, the system bus is implemented as a crossbar switch between system boards to support high-throughput data transfer with consistent latency times between all components. To improve performance, the physical addressing of memory on a motherboard of a SPARC Enterprise M4000 and M5000 servers or the CMU of a SPARC Enterprise M8000 and M9000 servers is evenly spread out across all system controllers on the same board.

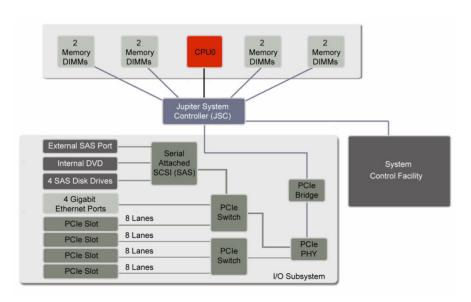

#### 4.1.1 SPARC Enterprise M3000 Server Interconnect Architecture

The SPARC Enterprise M3000 server system design is contained within a single motherboard. Within the architecture, the Jupiter System Controller (JSC) is a single ASIC that performs both the memory address controller and system controller functions. The JSC is connected to the CPU, memory DIMMs, and the I/O controller (PCIe bridge). An architecture diagram of the SPARC Enterprise M3000 server is shown in Figure 4-1.

Figure 4-1. SPARC Enterprise M3000 server interconnect diagram.

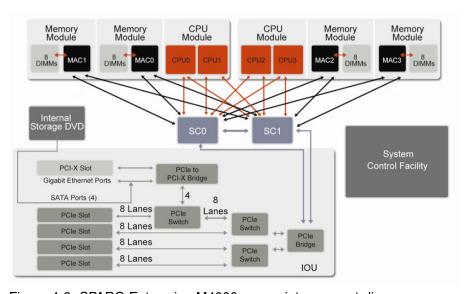

#### 4.1.2 SPARC Enterprise M4000 Server Interconnect Architecture

The SPARC Enterprise M4000 server is implemented within a single motherboard that contains two system controllers. Both system controllers connect to each other, as well as CPU modules, memory address controllers, and the IOU (Figure 4-2).

Figure 4-2. SPARC Enterprise M4000 server interconnect diagram.

#### 4.1.3 SPARC Enterprise M5000 Server Interconnect Architecture

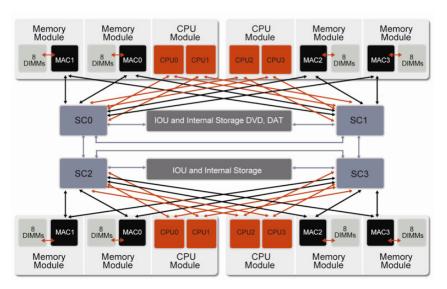

The SPARC Enterprise M5000 server is implemented within a single motherboard but features two logical system boards. Similar to the SPARC Enterprise M4000 server design, each logical system board contains two system controllers that connect to each other, as well as CPU modules, memory access controllers, and an IOU. In addition, each system controller connects to a corresponding system controller on the other logical system board (Figure 4-3).

Figure 4-3. SPARC Enterprise M5000 server interconnect diagram.

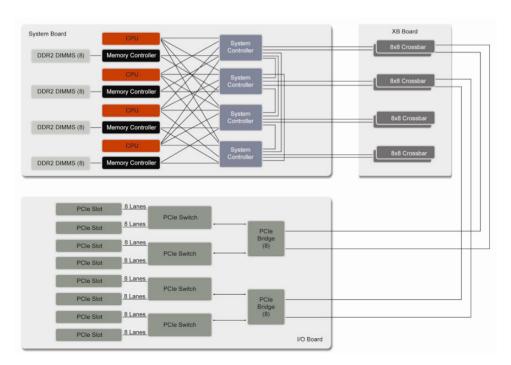

#### 4.1.4 SPARC Enterprise M8000 and M9000 Servers Interconnect Architecture

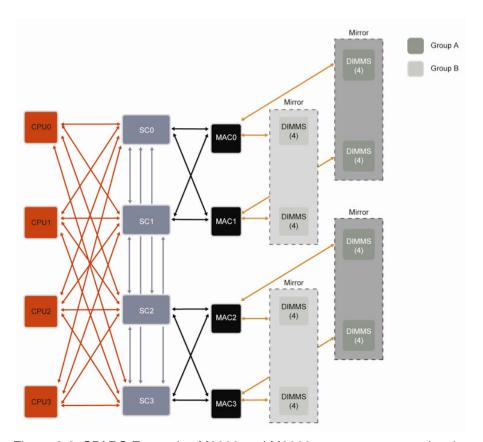

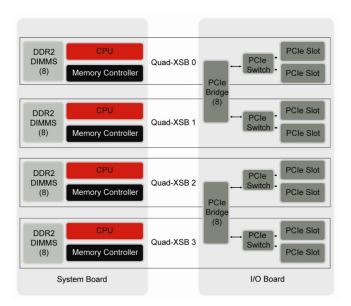

SPARC Enterprise M8000 and M9000 servers feature multiple system boards that connect to a common crossbar. Each system board contains four system controllers and each system controller connects to every CPU module. For improved bandwidth, every memory access controller connects to two system controllers, and each system controller connects to every other system controller within the system board. The system controllers also provide a connection to each crossbar unit, supporting data transfer to other system boards (Figure 4-4).

Figure 4-4. SPARC Enterprise M8000 and M9000 server interconnect diagram.

### 4.2 System Interconnect Reliability Features

Built-in redundancy and reliability features of SPARC Enterprise M-series servers system interconnect enhance the stability of these servers. The Jupiter interconnect protects against loss or corruption of both address and data of transaction with ECC protection on all system buses. When a single-bit data error is detected in a CPU, Memory Access Controller, or I/O Controller, hardware corrects the data and performs the transfer. SPARC Enterprise M8000 and M9000 servers can automatically make the best choice of whether degrading a specific bus or degrading the crossbar switches. In the rare event of a hardware failure within the interconnect, the system uses the surviving bus route on restart, isolating the faulty crossbar and facilitating the resumption of operations.

#### 4.3 Scalable Performance

The high bandwidth and overall design of the Jupiter system interconnect contributes to the scalable performance of SPARC Enterprise M-series servers. Theoretical peak system throughput, snoop bandwidth, and I/O Bandwidth numbers, as well as Stream benchmark results are found in Table 4-1.

In SPARC Enterprise M4000, M5000, M8000, and M9000 servers, the CPUs, memory address controllers, and I/O controllers are directly connected to the system controllers by a high-speed broadband switch for data transfer. As a result, a relatively even latency can be maintained between individual components. As components are added, processing capability and latency are not degraded. In fact, the crossbar interconnect implementation in SPARC Enterprise M8000 and M9000 servers results in increased interconnect bandwidth every time a system board is added to the server.

Table 4-1. Theoretical system bandwidth and theoretical I/O bandwidth at peak time, snoop bandwidth, and stream benchmark results for SPARC Enterprise.

|                                                               | Theoretical<br>system<br>bandwidth at<br>peak time*a<br>(GB/second) | Snoop<br>bandwidth<br>(GB/second) |       | Stream<br>Benchmark<br>Copy results<br>(GB/second) | Theoretical<br>Peak I/O<br>bandwidth*b<br>(GB/second) |

|---------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|-------|----------------------------------------------------|-------------------------------------------------------|

| SPARC Enterprise<br>M3000 server                              | 20                                                                  | N/A                               | 5.1   | 6.4                                                | 4                                                     |

| SPARC Enterprise<br>M4000 server                              | 32                                                                  | 129                               | 12.7  | 12.5                                               | 8                                                     |

| SPARC Enterprise<br>M5000 server                              | 64                                                                  | 129                               | 25.2  | 24.8                                               | 16                                                    |

| SPARC Enterprise<br>M8000 server                              | 184                                                                 | 245                               | 69.6  | 60.3                                               | 61                                                    |

| SPARC Enterprise<br>M9000 server<br>(32-CPU<br>configuration) | 368                                                                 | 245                               | 134.4 | 114.9                                              | 122                                                   |

| SPARC Enterprise<br>M9000 server<br>(64-CPU<br>configuration) | 737                                                                 | 245                               | 227.1 | 224.4                                              | 244                                                   |

<sup>\*</sup>a:Theoretical Peak System Bandwidth is calculated by multiplying the bus width by the frequency of the bus between the system controller and the memory access controller.

<sup>\*</sup>b:Theoretical Peak I/O Bandwidth is calculated by multiplying the bus width by the frequency of the bus between the system controller and the PCI bridge.

# SPARC64 VI and SPARC64 VII/VII+ Processors

SPARC Enterprise M3000 server supports quad-core and dual-core of SPARC64 VII and SPARC64 VII+ processors. SPARC Enterprise M4000, M5000, M8000, and M9000 servers can utilize both the Fujitsu dual-core SPARC64 VI and quad-core SPARC64 VII/ VII+ processors. These processors incorporate innovative multi-core and multithreaded technology, and provide extensive reliability features. In addition, the SPARC64 VI and SPARC64 VII/VII+ processors are SPARC V9 level 2 compliant, helping to provide support for thousands of existing software applications. The use of SPARC64 VI and SPARC64 VII/VII+ processors within SPARC Enterprise M-series servers offer organizations exceptional reliability, application choice, and outstanding processing power.

## 5.1 Next-Generation Processor Technology

The past decade introduced major changes to processor architectures as system design engineers found that increases to CPU clock rates began exhibiting diminishing returns on performance, and creating power and heat concerns. Innovations such as Chip Multiprocessing (CMP), Vertical Multithreading (VMT), and Simultaneous Multithreading (SMT) technologies now dominate plans for improving compute capacity.

#### 5.1.1 Chip Multiprocessing (CMT)

Chip Multiprocessing technology (CMT) is an architecture in which multiple physical cores are integrated on a single processor module. Each physical core runs a single execution thread of a multithreaded application independently from other cores at any given time. With this technology, dual-core processors often double the performance of single-core modules. The ability to process multiple instructions at each clock cycle provides the bulk of the performance advantage, but improvements also result from the short distances and fast bus speeds between chips as compared to traditional CPU to CPU communication.

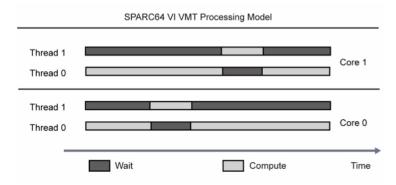

#### 5.1.2 Vertical Multithreading (VMT)

Vertical multithreading (VMT) technology lets a single physical core host multiple threads, each viewed by the operating system as a virtual CPU. Multiple threads on the same core run in a time-sliced fashion, with only one executing at any given moment. A thread does not run if it is idle, or has encountered a cache miss and is waiting for main memory. A thread switch occurs on events such as an L2 cache miss, hardware timer, interrupt, or specific instruction to control threads. In this way, VMT improves system performance by maximizing processor utilization and effectively mitigating the impact of a cache miss. VMT is enabled automatically to improve performance when the number of threads in the system exceeds the number of cores.

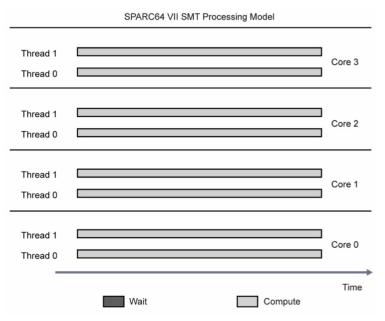

#### 5.1.3 Simultaneous Multithreading (SMT)

Simultaneous multithreading (SMT) technology supports the simultaneous execution of multiple threads in a multithreaded core. From the software point of view, each thread is independent. This method of multithreading is facilitated by duplicating compute resources. A few resources remain shared between threads, such as instruction buffers, Reservation Station, and caches. With SMT, context switch time is eliminated and threads within a single core share the instruction pipeline smoothly. When both threads are ready to run, they alternate cycles for superscaler instruction issue, and share the functional units according to need.

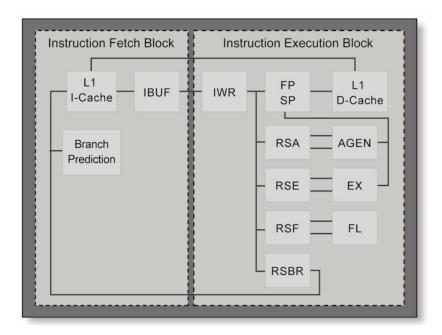

### 5.2 Architecture of SPARC64 VII and SPARC64 VII/VII+ Processors

Steady enhancements and changes rather than design overhauls are key to the current success of SPARC64 series processors. Toward that end, the SPARC64 VI and SPARC64 VII/VII+ CPU modules reuse the proven and reliable SPARC64 V core with no major pipeline changes. To increase throughput, the SPARC64 VI and SPARC64 VII/VII+ processors leverage multi-core, multithreaded architectures. The SPARC64 VI processor utilizes VMT technology and offers two cores and two threads per core. The SPARC 64 VII/VII+ processors incorporates a quad-core architecture with two threads per core and takes advantage of SMT technology to further improve performance. Specifications for the SPARC64 VI and SPARC64 VII/VII+ processors are detailed in Table 5-1.

Table 5-1. SPARC64 VI and SPARC64 VII/VII+ processors specifications

|              | SPARC VI processor                                                                                                                                                                                                              | SPARC VII processor                                                                                                                                                                                                                    | SPARC VII+ processor                                                                                                                                                                  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speed        | <ul><li>2.15 GHz</li><li>2.28 GHz</li><li>2.4 GHz</li></ul>                                                                                                                                                                     | <ul> <li>2.4 GHz</li> <li>2.52 GHz</li> <li>2.53 GHz</li> <li>2.75 GHz</li> <li>2.77 GHz</li> <li>2.88 GHz</li> </ul>                                                                                                                  | <ul><li>2.66 GHz</li><li>2.86 GHz</li><li>3.0 GHz</li></ul>                                                                                                                           |

| Architecture | <ul><li>Dual-core</li><li>SPARC V9</li><li>sun4u</li><li>90 nm process technology</li></ul>                                                                                                                                     | <ul> <li>Quad-core,<br/>Dual-core*a</li> <li>SPARC V9</li> <li>sun4u</li> <li>65 nm process<br/>technology</li> </ul>                                                                                                                  | <ul> <li>Quad-core,<br/>Dual-core*a</li> <li>SPARC V9</li> <li>sun4u</li> <li>65 nm process<br/>technology</li> </ul>                                                                 |

| L1 cache     | <ul> <li>128 KB L1 I-cache<br/>per core</li> <li>128 KB L1 D-cache<br/>per core</li> </ul>                                                                                                                                      | <ul><li>64 KB L1 I-cache<br/>per core</li><li>64 KB L1 D-cache<br/>per core</li></ul>                                                                                                                                                  | <ul><li>64 KB L1 I-cache<br/>per core</li><li>64 KB L1 D-cache<br/>per core</li></ul>                                                                                                 |

| L2 cache     | <ul> <li>5 MB (2.15 GHz and 2.28 GHz)</li> <li>6 MB (2.4 GHz)</li> <li>10-way associative (2.15 and 2.28 GHz)</li> <li>12-way associative (2.4 GHz)</li> <li>256 byte line size</li> <li>ECC tag and data protection</li> </ul> | <ul> <li>5 MB (2.4 GHz, 2.52 GHz*a, 2.75 GHz, and 2.77 GHz)</li> <li>5.5 MB (2.53 GHz)</li> <li>6 MB (2.52 GHz*b and 2.88 GHz)</li> <li>12-way associative</li> <li>256 byte line size</li> <li>ECC tag and data protection</li> </ul> | <ul> <li>5.5 MB (2.86 GHz)</li> <li>11 MB (2.66 GHz)</li> <li>12 MB (3.0 GHz)</li> <li>12-way associative</li> <li>256 byte line size</li> <li>ECC tag and data protection</li> </ul> |

| Power        | <ul><li>120 watts nominal</li><li>150 watts maximum</li></ul>                                                                                                                                                                   | • 135 watts nominal<br>• 150 watts maximum                                                                                                                                                                                             | <ul><li>135 watts nominal</li><li>160 watts maximum</li></ul>                                                                                                                         |

<sup>\*</sup>a:SPARC Enterprise M3000 server

<sup>\*</sup>b:SPARC Enterprise M8000 and M9000 servers

#### 5.2.1 Cache System

As shown in Figure 5-1, SPARC64 VI and SPARC64 VII/VII+ processors implement a two-layer cache memory structure. Both processors include a moderate-capacity primary cache (L1 cache) and a high-capacity secondary cache (L2 cache). The L1 cache consists of a cache dedicated for instructions (L1 I-cache) and a cache dedicated for operands (L1 D-cache). The L1 D-cache is divided into eight banks on four-byte address boundaries, and two operands can be accessed at one time. The L1 cache utilizes virtual addresses for cache indexes and physical addresses for cache tags, a method known as virtually indexed physically tagged (VIPT). In order to protect against the VIPT synonym problem — indexing the same physical address to two virtual addresses — the L2 cache on SPARC64 VI and SPARC64 VII/VII+ processors prevents creation of synonym entries in the L1 cache.

Figure 5-1. The SPARC64 VI and SPARC64 VII/VII+ processors incorporate a cache structure.

Within SPARC64 VI and SPARC64 VII/VII+ processors, the L2 cache is shared across all cores. The bus for sending data that is read from the L2 cache to the L1 cache provides a width of 32 bytes per two cores, and the bus for sending data from the L1 D-cache to L2 cache offers a width of 16 bytes per core.

The cache update policies of L1 cache and L2 cache are both write-back. Updates to cached data are written only to cache rather than system memory. As a result, store operations can complete with the update of one cache hierarchy. Data in the cache location is written-back to system memory when the cache line is reassigned to another memory location. Given the high frequency of the store operation, the write-back method can provide a performance advantage by reducing inter-cache and memory access traffic.

Since the write-back method keeps the latest data in the cache, special measures must be taken to prevent a single cache fault from impacting system wide operations. SPARC64 VI and SPARC64 VII/VII+ processors include advanced capabilities to track error

conditions and force write-backs from cache to system memory when the potential for processor faults exist. More information on these features can be found in this chapter in the section titled *Reliability, Availability, and Serviceability Features*.

#### 5.2.2 SPARC64 VI Processor Micro-Architecture Overview

The SPARC64 VI processor design retains the high performance and reliability of the SPARC64 V processor, while offering considerable throughput improvement. To achieve performance gains, the SPARC64 VI processor implements a combination of CMP and VMT technologies. This processor consists of two physical cores where each core supports two VMT threads, supporting the execution of four threads in parallel. The operating system views each thread as a virtual processor. For example, the Oracle Solaris psradm command can be used to set each virtual CPU as spare, on-line, or off-line as desired.

Two threads that belong to the same physical core share most of the core's resources, such as the ALU and instruction pipeline, while the two physical cores only share the L2 cache and system interface. Using coarse-grained multithreading techniques, a single thread occupies the full resources of the core until a long latency event. Specifically, a thread switch is triggered on an L2 cache miss or passage of a periodic time interval. This approach mitigates the effect of cache misses by scheduling an unblocked thread, while maintaining fairness so all threads make progress.

Support for multiple threads in this manner requires duplicating general-purpose registers (GPR), floating point registers (FPR), the program counter (PC), and the control (state) registers. A copy of GPR called the current window register (CWR) realizes one-cycle register file access time. In addition, a fast, high-bandwidth path from the GPR to the CWR speeds operations when a register window move or thread switch is required.

While the CMP and VMT innovations specifically enhance multithreaded performance, single-threaded throughput is not compromised. The SPARC64 VI processor delivers approximately two times the single threaded performance of SPARC64 V running at 1.35 GHz. Other enhancements to the SPARC64 VI processor include a refined core with floating point improvements and a doubled Translation Lookaside Buffer (TLB) which reduces the miss rate to improve both integer and floating-point application performance.

#### 5.2.3 SPARC64 VII/VII+ Processor Micro-Architecture Overview

The basic structure of the core pipeline of the SPARC64 VII/VII+ processor is the same as that of the SPARC64 VI processor. However, the SPARC64 VII/VII+ processor utilizes SMT technology instead of VMT technology to implement multithreading. As shown in Figure 5-2, the SPARC64 VI processor takes advantage of VMT technology to execute two threads in parallel — only one thread is active at any given time.

Figure 5-2. Within the VMT processing model utilized by the SPARC64 VI processor only one thread per core is active at any given time.

Within the VMT model, a specific trigger must occur for processing to switch over to the alternate thread. By implementing SMT technology, both threads within each core on the SPARC VII/VII+ processor can execute simultaneously (Figure 5-3). As a result, the SPARC VII/VII+ offers the potential to achieve greater throughput and performance.

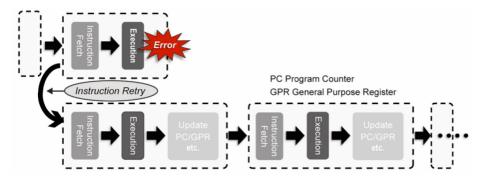

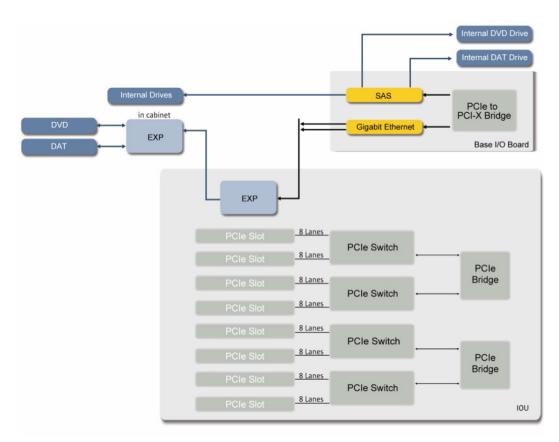

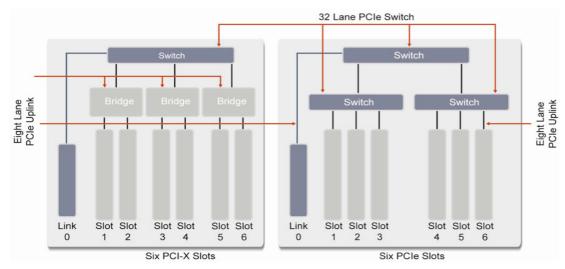

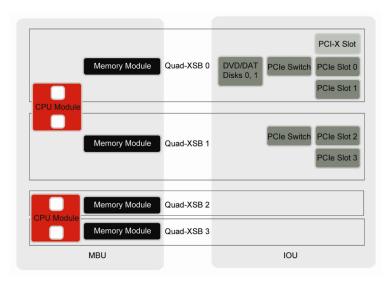

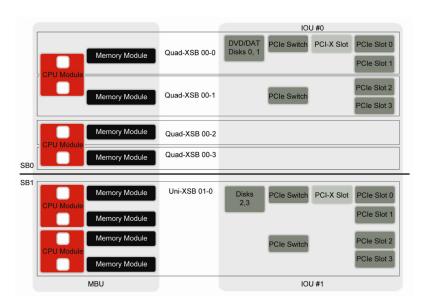

Figure 5-3. SMT technology implemented by the SPARC64 VII/VII+ processor offers the potential execute all threads within a core simultaneously.