## **SPARC Enterprise ARCHITECTURE**

M4000/M5000/M8000/M9000 Servers

Architecture Flexible, Mainframe-Class Computer Power

White Paper October 2009

Copyright 2007-2009 FUJITSU LIMITED, 1-1, Kamikodanaka 4-chome, Nakahara-ku, Kawasaki-shi, Kanagawa-ken 211-8588, Japan. All rights reserved.

Sun Microsystems, Inc. provided technical input and review on portions of this material.

Sun Microsystems, Inc. and Fujitsu Limited each own or control intellectual property rights relating to products and technology described in this document, and such products, technology and this document are protected by copyright laws, patents and other intellectual property laws and international treaties. The intellectual property rights of Sun Microsystems, Inc. and Fujitsu Limited in such products, technology and this document include, without limitation, one or more of the United States patents listed at http://www.sun.com/patents and one or more additional patents or patent applications in the United States or other countries.

This document and the product and technology to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of such product or technology, or of this document, may be reproduced in any form by any means without prior written authorization of Fujitsu Limited and Sun Microsystems, Inc., and their applicable licensors, if any. The furnishing of this document to you does not give you any rights or licenses, express or implied, with respect to the product or technology to which it pertains, and this document does not contain or represent any commitment of any kind on the part of Fujitsu Limited or Sun Microsystems, Inc., or any affiliate of either of them.

This document and the product and technology described in this document may incorporate third-party intellectual property copyrighted by and/or licensed from suppliers to Fujitsu Limited and/or Sun Microsystems, Inc., including software and font technology.

Per the terms of the GPL or LGPL, a copy of the source code governed by the GPL or LGPL, as applicable, is available upon request by the End User. Please contact Fujitsu Limited or Sun Microsystems, Inc.

This distribution may include materials developed by third parties.

Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California. UNIX is a registered trademark in the U.S. and in other countries, exclusively licensed through X/Open Company, Ltd.

Sun, Sun Microsystems, the Sun logo, Java, Netra, Solaris, Sun Ray, Answerbook2, docs.sun.com, OpenBoot, and Sun Fire are trademarks or registered trademarks of Sun Microsystems, Inc., or its subsidiaries, in the U.S. and other countries.

Fujitsu and the Fujitsu logo are registered trademarks of Fujitsu Limited.

All SPARC trademarks are used under license and are registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon architecture developed by Sun Microsystems, Inc.

SPARC64 is a trademark of SPARC International, Inc., used under license by Fujitsu Microelectronics, Inc. and Fujitsu Limited.

The OPEN LOOK and Sun<sup>TM</sup> Graphical User Interface was developed by Sun Microsystems, Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees who implement OPEN LOOK GUIs and otherwise comply with Sun's written license agreements.

United States Government Rights - Commercial use. U.S. Government users are subject to the standard government user license agreements of Sun Microsystems, Inc. and Fujitsu Limited and the applicable provisions of the FAR and its supplements.

Disclaimer: The only warranties granted by Fujitsu Limited, Sun Microsystems, Inc. or any affiliate of either of them in connection with this document or any product or technology described herein are those expressly set forth in the license agreement pursuant to which the product or technology is provided. EXCEPT AS EXPRESSLY SET FORTH IN SUCH AGREEMENT, FUJITSU LIMITED, SUN MICROSYSTEMS, INC. AND THEIR AFFILIATES MAKE NO REPRESENTATIONS OR WARRANTIES OF ANY KIND (EXPRESS OR IMPLIED) REGARDING SUCH PRODUCT OR TECHNOLOGY OR THIS DOCUMENT, WHICH ARE ALL PROVIDED AS IS, AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID. Unless otherwise expressly set forth in such agreement, to the extent allowed by applicable law, in no event shall Fujitsu Limited, Sun Microsystems, Inc. or any of their affiliates have any liability to any third party under any legal theory for any loss of revenues or profits, loss of use or data, or business interruptions, or for any indirect, special, incidental or consequential damages, even if advised of the possibility of such damages.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Copyright 2007-2009 FUJITSU LIMITED, 1-1, Kamikodanaka 4-chome, Nakahara-ku, Kawasaki-shi, Kanagawa-ken 211-8588, Japon. Tous droits réservés.

Entrée et revue tecnical fournies par Sun Microsystems, Incl sur des parties de ce matériel.

Sun Microsystems, Inc. et Fujitsu Limited détiennent et contrôlent toutes deux des droits de propriété intellectuelle relatifs aux produits et technologies décrits dans ce document. De même, ces produits, technologies et ce document sont protégés par des lois sur le copyright, des brevets, d'autres lois sur la propriété intellectuelle et des traités internationaux. Les droits de propriété intellectuelle de Sun Microsystems, Inc. et Fujitsu Limited concernant ces produits, ces technologies et ce document comprennent, sans que cette liste soit exhaustive, un ou plusieurs des brevets déposés aux États-Unis et indiqués à l'adresse http://www.sun.com/patents de même qu'un ou plusieurs brevets ou applications brevetées supplémentaires aux États-Unis et dans d'autres pays.

Ce document, le produit et les technologies afférents sont exclusivement distribués avec des licences qui en restreignent l'utilisation, la copie, la distribution et la décompilation. Aucune partie de ce produit, de ces technologies ou de ce document ne peut être reproduite sous quelque forme que ce soit, par quelque moyen que ce soit, sans l'autorisation écrite préalable de Fujitsu Limited et de Sun Microsystems, Inc., et de leurs éventuels bailleurs de licence. Ce document, bien qu'il vous ait été fourni, ne vous confère aucun droit et aucune licence, expresses ou tacites, concernant le produit ou la technologie auxquels il se rapporte. Par ailleurs, il ne contient ni ne représente aucun engagement, de quelque type que ce soit, de la part de Fujitsu Limited ou de Sun Microsystems, Inc., ou des sociétés affiliées.

Ce document, et le produit et les technologies qu'il décrit, peuvent inclure des droits de propriété intellectuelle de parties tierces protégés par copyright et/ou cédés sous licence par des fournisseurs à Fujitsu Limited et/ou Sun Microsystems, Inc., y compris des logiciels et des technologies relatives aux polices de caractères.

Par limites du GPL ou du LGPL, une copie du code source régi par le GPL ou LGPL, comme applicable, est sur demande vers la fin utilsateur disponible; veuillez contacter Fujitsu Limted ou Sun Microsystems, Inc.

Cette distribution peut comprendre des composants développés par des tierces parties.

Des parties de ce produit pourront être dérivées des systèmes Berkeley BSD licenciés par l'Université de Californie. UNIX est une marque déposée aux Etats-Unis et dans d'autres pays et licenciée exclusivement par X/Open Company, Ltd.

Sun, Sun Microsystems, le logo Sun, Java, Netra, Solaris, Sun Ray, Answerbook2, docs.sun.com, OpenBoot, et Sun Fire sont des marques de fabrique ou des marques déposées de Sun Microsystems, Inc., ou ses filiales, aux Etats-Unis et dans d'autres pays.

Fujitsu et le logo Fujitsu sont des marques déposées de Fujitsu Limited.

Toutes les marques SPARC sont utilisées sous licence et sont des marques de fabrique ou des marques déposées de SPARC International, Inc. aux Etats-Unis et dans d'autres pays. Les produits portant les marques SPARC sont basés sur une architecture développée par Sun Microsystems, Inc.

SPARC64 est une marques déposée de SPARC International, Inc., utilisée sous le permis par Fujitsu Microelectronics, Inc. et Fujitsu Limited.

L'interface d'utilisation graphique OPEN LOOK et Sun<sup>TM</sup> a été développée par Sun Microsystems, Inc. pour ses utilisateurs et licenciés. Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d'utilisation visuelle ou graphique pour l'industrie de l'informatique. Sun détient une license non exclusive de Xerox sur l'interface d'utilisation graphique Xerox, cette licence couvrant également les licenciés de Sun qui mettent en place l'interface d'utilisation graphique OPEN LOOK et qui, en outre, se conforment aux licences écrites de Sun.

Droits du gouvernement américain - logiciel commercial. Les utilisateurs du gouvernement américain sont soumis aux contrats de licence standard de Sun Microsystems, Inc. et de Fujitsu Limited ainsi qu'aux clauses applicables stipulées dans le FAR et ses suppléments.

Avis de non-responsabilité: les seules garanties octroyées par Fujitsu Limited, Sun Microsystems, Inc. ou toute société affiliée de l'une ou l'autre entité en rapport avec ce document ou tout produit ou toute technologie décrit(e) dans les présentes correspondent aux garanties expressément stipulées dans le contrat de licence régissant le produit ou la technologie fourni(e). SAUF MENTION CONTRAIRE EXPRESSÉMENT STIPULÉE DANS CE CONTRAT, FUJITSU LIMITED, SUN MICROSYSTEMS, INC. ET LES SOCIÉTÉS AFFILIÉES REJETTENT TOUTE REPRÉSENTATION OU TOUTE GARANTIE, QUELLE QU'EN SOIT LA NATURE (EXPRESSE OU IMPLICITE) CONCERNANT CE PRODUIT, CETTE TECHNOLOGIE OU CE DOCUMENT, LESQUELS SONT FOURNIS EN L'ÉTAT. EN OUTRE, TOUTES LES CONDITIONS, REPRÉSENTATIONS ET GARANTIES EXPRESSES OU TACITES, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE À LA QUALITÉ MARCHANDE, À L'APTITUDE À UNE UTILISATION PARTICULIÈRE OU À L'ABSENCE DE CONTREFAÇON, SONT EXCLUES, DANS LA MESURE AUTORISÉE PAR LA LOI APPLICABLE. Sauf mention contraire expressément stipulée dans ce contrat, dans la mesure autorisée par la loi applicable, en aucun cas Fujitsu Limited, Sun Microsystems, Inc. ou l'une de leurs filiales ne sauraient être tenues responsables envers une quelconque partie tierce, sous quelque théorie juridique que ce soit, de tout manque à gagner ou de perte de profit, de problèmes d'utilisation ou de perte de données, ou d'interruptions d'activités, ou de tout dommage indirect, spécial, secondaire ou consécutif, même si ces entités ont été préalablement informées d'une telle éventualité.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTES AUTRES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES SONT FORMELLEMENT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON.

#### **Table of Contents**

| Chapter 1  | Flexible, Mainframe-Class Compute Power for the                                      |

|------------|--------------------------------------------------------------------------------------|

|            | Datacenter                                                                           |

| 1.1        | Introducing the Fujitsu SPARC Enterprise Server Family 1                             |

| 1.2<br>1.3 | Fujitsu SPARC Enterprise Server Family Overview                                      |

| 1.3        | -                                                                                    |

| Chapter 2  | System Architecture 6                                                                |

| 2.1        | System Component Overview 6                                                          |

| 2.2        | Midrange Systems — Fujitsu SPARC Enterprise M4000 and                                |

| 0.0        | Fujitsu SPARC Enterprise M5000                                                       |

| 2.3        | High-End Systems — Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 |

|            | rujiisu SPANO Eilleipiise M9000                                                      |

| Chapter 3  | System Bus Architecture — Jupiter Interconnect 18                                    |

| 3.1        | Fujitsu SPARC Enterprise Server Interconnect                                         |

| 0.0        | Architecture                                                                         |

| 3.2<br>3.3 | System Interconnect Reliability Features                                             |

|            | Scalable Felloffilance                                                               |

| Chapter 4  | Fujitsu SPARC64 VI/SPARC64 VII Processors 24                                         |

| 4.1        | SPARC64 Series                                                                       |

| 4.2        | SPARC64 VI Overview                                                                  |

| 4.3<br>4.4 | SPARC64 VII Overview                                                                 |

| 4.4<br>4.5 | Cache System                                                                         |

| 4.6        | Reliability, Availability, and Serviceability (RAS) Functions33                      |

|            |                                                                                      |

| Chapter 5  | I/O Subsystem                                                                        |

| 5.1<br>5.2 | I/O Subsystem Architecture                                                           |

| 5.2<br>5.3 | Internal Peripherals                                                                 |

|            | ·                                                                                    |

| Chapter 6  | Reliability, Availability, and Serviceability 42                                     |

| 6.1        | Redundant and Hot-Swap Components42                                                  |

| 6.2        | Dynamic Domains                                                                      |

| 6.3        | Dynamic Reconfiguration                                                              |

| 6.4<br>6.5 | Advanced Reliability Features                                                        |

| 0.0        | Error Detection, Diagnosis, and Recovery48                                           |

| Chapter 7  | System Management                                                                    |

| 7.1        | Extended System Control Facility                                                     |

i

#### Table of Contents

| Chapter 8 | The Solaris 10 Operating System        |

|-----------|----------------------------------------|

| 8.1       | Observability and Performance          |

| 8.2       | Availability55                         |

| 8.3       | Security57                             |

| 8.4       | Virtualization and Resource Management |

| Chapter 9 | <b>Summary</b>                         |

## Flexible, Mainframe-Class Compute Power for the Datacenter

Reliance upon technology within enterprises is greater than ever. Today, compute systems play a critical role in every function from product design to customer order fulfillment. In many cases, business success is dependent on continuous availability of IT services. Once only required in pockets of the datacenter, mainframe-class reliability and serviceability are now essential for systems throughout the enterprise. In addition, powering datacenter servers and keeping services running through a power outage are significant concerns.

While availability is a top priority, costs must also remain in budget and operational familiarity maintained. To deliver networked services as efficiently and economically as possible, enterprises look to maximize use of every IT asset through consolidation and virtualization strategies. As a result, modern IT system requirements reach far beyond simple measures of compute capacity. Organizations need highly flexible servers with built-in virtualization capabilities and associated tools, technologies, and processes that work to optimize sever utilization. With budgets still in mind, new computing infrastructures must also help protect current investments in technology and training.

#### 1.1 Introducing the Fujitsu SPARC Enterprise Server Family

Fujitsu SPARC Enterprise<sup>TM</sup> servers are highly reliable, easy to manage, vertically-scalable systems with all of the benefits of traditional mainframes and none of the associated cost, complexity, or vendor lock-in (Figure 1-1). In fact, Fujitsu SPARC Enterprise servers deliver a mainframe-class system architecture at open systems prices. With symmetric multiprocessing (SMP) scalability from one to 64 processors, memory subsystems as large as 4 TB, and high-throughput I/O architectures, Fujitsu SPARC Enterprise servers easily perform the heavy lifting required by consolidated workloads. Furthermore, Fujitsu SPARC Enterprise servers run the powerful Solaris<sup>TM</sup> 10 Operating System (OS) and include leading virtualization technologies. By offering Dynamic Domains (=Partitioning feature), eXtended System Boards, Dynamic Reconfiguration, and Solaris Containers technology, Fujitsu SPARC Enterprise servers bring mainframe-class, sophisticated resource control to an open systems compute platform.

Massive compute power, a resilient system architecture, flexible resource control features, and the advanced capabilities of the Solaris 10 OS combine in Fujitsu SPARC

1

Enterprise servers to provide organizations a best-in-class enterprise platform. As an added benefit, Fujitsu SPARC Enterprise servers also offer improved performance over previous generations of Fujitsu servers, with a clear upgrade path that protects existing investments in software, training, and datacenter practices. By taking advantage of Fujitsu SPARC Enterprise servers, IT organizations can create a more powerful infrastructure, optimize hardware utilization, and increase application availability — resulting in lower operational cost and risk.

Figure 1-1. The Fujitsu SPARC Enterprise server family provides enterprises with scalable power, reliability, and flexibility.

#### 1.2 Fujitsu SPARC Enterprise Server Family Overview

The members of the Fujitsu SPARC Enterprise server family share many of the same characteristics which provide power, reliability, and flexibility to enterprises. Fujitsu SPARC Enterprise servers all feature a balanced, highly scalable SMP design that utilizes the latest generation of SPARC64 processors connected to memory and I/O by a new high-speed, low latency system interconnect, delivering exceptional throughput to software applications. Also architected to reduce planned and unplanned downtime, Fujitsu SPARC Enterprise servers include stellar reliability, availability, and serviceability capabilities to avoid outages and reduce recovery time. Design features of Fujitsu SPARC Enterprise servers, such as advanced CPU integration and data path integrity, memory Extended ECC and memory mirroring, end-to-end data protection, hot-swappable components, fault resilient power options, and hardware redundancy boost the reliability of these servers.

Fujitsu SPARC Enterprise servers also provide unmatched configuration flexibility. As in other Fujitsu high-end servers, administrators can use Dynamic Domains to physically divide a single Fujitsu SPARC Enterprise server into multiple electrically isolated partitions, each running independent instances of the Solaris Operating System (Solaris OS). Hardware or software failures in one Dynamic Domains do not affect applications running in other domains, unless the failed resource is shared across both domains.

Dynamic Reconfiguration can then reallocate hardware resources among Dynamic Domains — without interrupting critical systems. Fujitsu SPARC Enterprise servers advance resource control one-step further with eXtended System Board technology, enabling allocation of sub-system board resources such as CPUs, memory, and I/O components to Dynamic Domains. The fine-grain resource control provided by eXtended System Board technology helps enterprises to further optimize resource utilization.

Adding even more value, the range of compute power offered by the Fujitsu SPARC Enterprise server family provides the levels of vertical scalability required for many deployment classes, enabling enterprises to match the right system to the job at hand. Rackmount Fujitsu SPARC Enterprise M4000 and Fujitsu SPARC Enterprise M5000 are economical, powerful, and reliable servers well-suited for mid-range system requirements, while Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 deliver the massive processing power needed for high-end computing (Table 1-1).

Table 1-1. The Fujitsu SPARC Enterprise server family supports midrange and high-end compute requirements.

|                           | Fujitsu SPARC<br>Enterprise M4000                                                                      | Fujitsu SPARC<br>Enterprise M5000                                                                      | Fujitsu SPARC<br>Enterprise M8000                                                                     | Fujitsu SPARC<br>Enterprise M9000<br>(32 CPU configuration                                        | Fujitsu SPARC<br>Enterprise M9000<br>) (64 CPU configuration)                                         |

|---------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Enclosure                 | 6 rack units                                                                                           | • 10 rack units                                                                                        | One cabinet                                                                                           | One cabinet                                                                                       | Two cabinets                                                                                          |

| SPARC64 VI<br>Processors  | <ul><li>2.15 GHz</li><li>5 MB L2 cache</li><li>Up to four dual-core chips</li></ul>                    | <ul><li>2.15 GHz</li><li>5 MB L2 cache</li><li>Up to eight dual-core chips</li></ul>                   | <ul> <li>2.28 GHz/2.4 GHz</li> <li>5 - 6 MB L2 cache</li> <li>Up to 16<br/>dual-core chips</li> </ul> | <ul> <li>2.28 GHz/2.4 GHz</li> <li>5 - 6 MB L2 cache</li> <li>Up to 32 dual-core chips</li> </ul> | <ul> <li>2.28 GHz/2.4 GHz</li> <li>5 - 6 MB L2 cache</li> <li>Up to 64<br/>dual-core chips</li> </ul> |

| SPARC64 VII<br>Processors | <ul> <li>2.4 GHz/2.53 GHz</li> <li>5 MB/5.5 MB L2 cache</li> <li>Up to four quad-core chips</li> </ul> | <ul> <li>2.4 GHz/2.53 GHz</li> <li>5 MB/5.5 MB L2 cache</li> <li>Up to eight quadcore chips</li> </ul> | <ul> <li>2.52 GHz/2.88 GHz</li> <li>6 MB L2 cache</li> <li>Up to 16<br/>quad-core chips</li> </ul>    | <ul><li>2.52 GHz/2.88 GHz</li><li>6 MB L2 cache</li><li>Up to 32 quad-core chips</li></ul>        | <ul> <li>2.52 GHz/2.88 GHz</li> <li>6 MB L2 cache</li> <li>Up to 64 quad-core chips</li> </ul>        |

| Memory                    | <ul><li> Up to 256 GB(*)</li><li> 32 DIMM slots</li></ul>                                              | <ul><li> Up to 512 GB(*)</li><li> 64 DIMM slots</li></ul>                                              | <ul><li> Up to 1 TB</li><li> 128 DIMM slots</li></ul>                                                 | <ul><li>Up to 2 TB</li><li>256 DIMM slots</li></ul>                                               | <ul><li> Up to 4 TB</li><li> 512 DIMM slots</li></ul>                                                 |

| Internal I/O<br>Slots     | <ul><li>Four PCIe</li><li>One PCI-X</li></ul>                                                          | <ul><li>Eight PCIe</li><li>Two PCI-X</li></ul>                                                         | • 32 PCIe                                                                                             | • 64 PCIe                                                                                         | • 128 PCIe                                                                                            |

| External I/O<br>Chassis   | • Up to two units                                                                                      | • Up to four units                                                                                     | • Up to 8 units                                                                                       | • Up to 16 units                                                                                  | • Up to 16 units                                                                                      |

| Internal<br>Storage       | <ul><li>Serial Attached<br/>SCSI</li><li>Up to two drives</li></ul>                                    | <ul><li>Serial Attached<br/>SCSI</li><li>Up to four drives</li></ul>                                   | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 16 drives</li></ul>                                    | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 32 drives</li></ul>                                | <ul><li>Serial Attached<br/>SCSI</li><li>Up to 64 drives</li></ul>                                    |

| Dynamic<br>Domains        | • Up to two                                                                                            | • Up to four                                                                                           | • Up to 16                                                                                            | • Up to 24                                                                                        | • Up to 24                                                                                            |

<sup>\*:</sup> When 8 GB DIMM is available.

#### 1.3 Meeting the Needs of Commercial and Scientific Computing

Suiting a wide range of computing environments, Fujitsu SPARC Enterprise servers provide the availability features needed to support commercial computing workloads along with the raw performance demanded by the high performance community (Table 1-2).

Table 1-2. The power and flexibility of Fujitsu SPARC Enterprise servers provide benefit to a broad range of enterprise applications.

| Fujitsu SPARC Enterprise M4000 and Fujitsu SPARC Enterprise M5000                                                                                                                                                                                                                         | Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000                                                                                                                                                                                                            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Server consolidation</li> <li>Business processing (ERP, CRM, OLTP, Batch)</li> <li>Database</li> <li>Decision support</li> <li>Datamart</li> <li>Web services</li> <li>System and network management</li> <li>Application development</li> <li>Scientific engineering</li> </ul> | <ul> <li>Server consolidation</li> <li>Business processing (ERP, CRM, OLTP, Batch)</li> <li>Database</li> <li>Decision support</li> <li>Data warehouses</li> <li>IT infrastructure</li> <li>Application serving</li> <li>Compute-intensive scientific engineering</li> </ul> |  |  |

### 2. System Architecture

Continually challenged by growing workloads and demands to do more with less, IT organizations realize that meeting processing requirements with fewer, more powerful systems holds economic advantages. The Fujitsu SPARC Enterprise server system interconnect, processors, memory subsystem, and I/O subsystem work together to create a scalable, high-performance platform ready to address server consolidation needs. By taking advantage of Fujitsu SPARC Enterprise servers, organizations can load multiple projects onto a single platform and accelerate application execution at lower costs.

#### 2.1 System Component Overview

The design of Fujitsu SPARC Enterprise servers specifically focuses on delivering high reliability, outstanding performance, and true SMP scalability. The characteristics and capabilities of every subsystem within these servers work toward this goal. The high-bandwidth system bus, powerful SPARC64 VI and SPARC64 VII processor chips, high-density memory option, high-speed PCI Express (PCIe), and PCI-extended (PCI-X) expansion slots of the SPARC Enterprise provide not only reliable scaling for enterprise applications but also high-level operational time and throughput.

#### 2.1.1 System Interconnect

Based on mainframe technology, the Jupiter system interconnect enables performance scalability and reliability for Fujitsu SPARC Enterprise servers. Multiple system controllers and crossbar units provide point-to-point connections between CPU, memory, and I/O subsystems. Providing more than one bus route between components enhances performance and enables system operation to continue in the event of a faulty switch. Indeed, the system interconnect used in these servers delivers as much as 737 GB/second of peak bandwidth, offering 5.5x more system throughput than Fujitsu's previous generation of high-end servers. Additional technical details for the system interconnect on each Fujitsu SPARC Enterprise server are found in *Chapter 3 – System Bus Architecture*.

#### 2.1.2 The SPARC64 VI/SPARC64 VII Processors

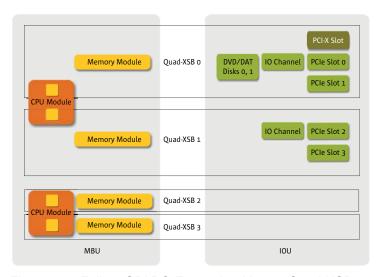

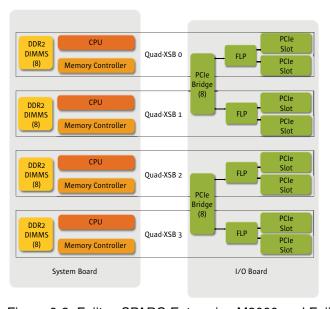

The SPARC Enterprise M4000, M5000, M8000, and M9000 use the SPARC64 VI processor and SPARC64 VII processor developed by Fujitsu. The SPARC64 VI and SPARC64 VII processors, which have multi-core (two cores for the SPARC64 VI and four cores for SPARC64 VII) and multi-threading architecture, have been designed based on experience in the mainframe computer field accumulated over several decades in pursuit of excellence in reliability and speed. They adopt advanced technology (90 nm for the SPARC64 VI and 65 nm for SPARC64 VII) with power consumption below 150 W. Moreover, because the SPARC64 VII processor can be mounted in a unit in which the SPARC64 VI processor is mounted, system performance can be expanded according to the customer's needs. Other detailed technical information about the SPARC64 VI and SPARC64 VII processors is contained in *Chapter 4 – SPARC64 VI/SPARC64 VII Processors*.

#### 2.1.3 Memory

The memory subsystem of Fujitsu SPARC Enterprise servers increases the scalability and throughput of these systems. In fact, the Fujitsu SPARC Enterprise M9000 accommodates up to 4 TB of memory. Fujitsu SPARC Enterprise servers use DDR-II DIMMs with 8-way memory interleave to enhance system performance. While multiple DIMM sizes are not supported within a single bank, DIMM capacities can vary across system boards. Available DIMM sizes include 1GB, 2GB, 4GB, and 8GB densities. Further details about the memory subsystem of each Fujitsu SPARC Enterprise server are described in Table 2-1.

Table 2-1. Fujitsu SPARC Enterprise server memory subsystem specifications.

|                               | Fujitsu<br>SPARC<br>Enterprise<br>M4000 | Fujitsu<br>SPARC<br>Enterprise<br>M5000 | Fujitsu<br>SPARC<br>Enterprise<br>M8000 | Fujitsu<br>SPARC<br>Enterprise<br>M9000<br>(32 CPU<br>configuration) | Fujitsu<br>SPARC<br>Enterprise<br>M9000<br>(64 CPU<br>configuration) |

|-------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Maximum<br>Memory<br>Capacity | • 256 GB(*)                             | • 512 GB(*)                             | • 1 TB                                  | • 2 TB                                                               | • 4 TB                                                               |

| DIMM slots                    | • 32                                    | • 64                                    | • Up to 128                             | • Up to 256                                                          | • Up to 512                                                          |

| Bank Size                     | • 4 DIMMs                               | • 4 DIMMs                               | • 8 DIMMs                               | • 8 DIMMs                                                            | • 8 DIMMs                                                            |

| Number of<br>Banks            | • 8                                     | • 16                                    | • Up to 16                              | • Up to 32                                                           | • Up to 64                                                           |

<sup>\*:</sup> When 8 GB DIMM is available.

Beyond performance, the memory subsystem of Fujitsu SPARC Enterprise servers are built with reliability in mind. ECC protection is implemented for all data stored in main memory, and the following advanced features foster early diagnosis and fault isolation that preserve system integrity and raise application availability.

- Memory patrol Memory patrol periodically scans memory for errors. This proactive

function prevents the use of faulty areas of memory before they can cause system or

application errors, improving system reliability.

- Memory Extended ECC —The memory Extended ECC function of these servers

enables single-bit error correction, enabling processing to continue despite events such

as burst read errors that are sometimes caused by memory device failures.

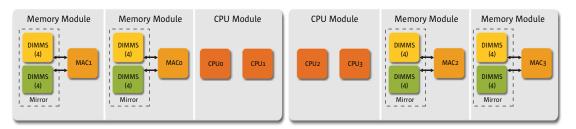

- Memory mirroring Memory mirroring is an optional, high-availability feature appropriate for execution of applications with the most stringent availability requirements. When memory mirroring mode is enabled on Fujitsu SPARC Enterprise servers, the memory subsystem duplicates the data on write and compares the data on read to each side of the memory mirror. In the event that errors occur at the bus or DIMM level, normal data processing continues through the other memory bus and alternate DIMM set. In Fujitsu SPARC Enterprise M4000 and Fujitsu SPARC Enterprise M5000, memory is mirrored within the same memory module, using the common memory address controller (MAC) Application Specific Integrated Circuit (ASIC) (Figure 2-1 and Figure 2-2).

Figure 2-1. Fujitsu SPARC Enterprise M4000 memory mirroring architecture.

Figure 2-2. Fujitsu SPARC Enterprise M5000 memory mirroring architecture.

On Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000, memory is mirrored across adjacent MAC ASICs to increase reliability (Figure 2-7). However, in a Quad-XSB configuration, paired DIMMs are split across different Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 Quad-XSBs. As such, memory mirroring is incompatible with the optional configuration of Quad-XSBs on Fujitsu SPARC Enterprise high-end server system boards.

Figure 2-3. Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 memory mirroring architecture.

#### 2.1.4 System Clock

While the implementation of the system clock varies within each member of the Fujitsu SPARC Enterprise server family, all are engineered with reliability in mind. In particular, Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 use a clock chip with redundant internal components. These high-end servers also implement two sources of clock signal and a dual signal source synchronous line exists between the clock chip and the system boards, enabling the system to restart in the event one route fails. Further enhancing availability and easing maintenance, the Fujitsu SPARC Enterprise M9000 provides for configuration of a redundant clock control unit.

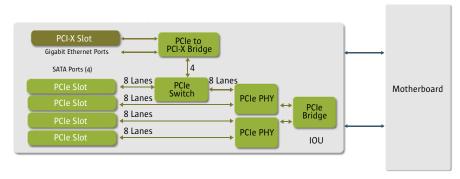

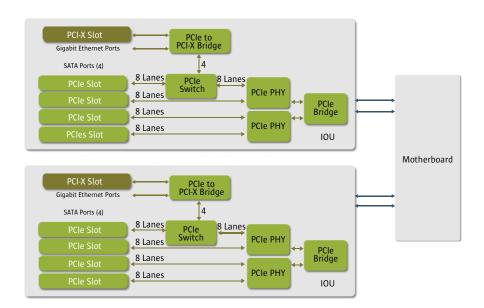

#### 2.1.5 PCI-Express and PCI-eXtended Technology

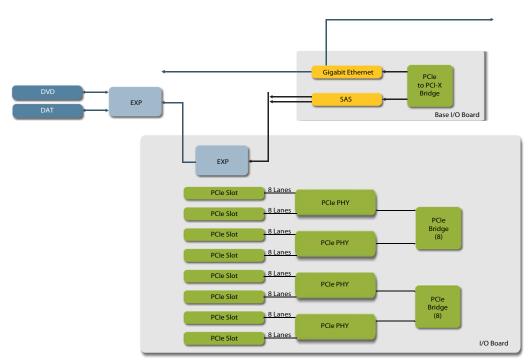

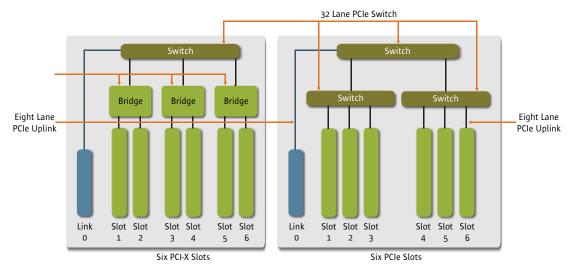

Fujitsu SPARC Enterprise servers use a PCI bus to provide high-speed data transfer within the I/O subsystem. In order to support PCIe expansion cards, all Fujitsu SPARC Enterprise servers use a PCIe physical layer (PCIe PHY) ASIC to manage the implementation of the PCIe protocol. PCIe technology doubles the peak data transfer rates of original PCI technology and reaches 2.5 Gb/second of throughput. In fact, PCIe was developed to accommodate high-speed interconnects such as Fibre Channel, Infiniband, and Gigabit Ethernet. Fujitsu SPARC Enterprise servers also support PCI-X expansion cards for fast access to external devices. PCI-X is backward compatible with existing PCI cards, but increases bandwidth enabling data transfer of up to 1 GB/second for 64-bit devices. Additional technical details for Fujitsu SPARC Enterprise server I/O subsystems can be found in *Chapter 5 – I/O Subsystem*.

#### 2.1.6 Service Processor – Extended System Control Facility

Simplifying management of compute systems leads to higher availability levels for hosted applications. With this in mind, mid-range and high-end models of Fujitsu SPARC Enterprise servers include an eXtended System Control Facility (XSCF). The XSCF consists of a dedicated processor that is independent of the server and runs the XSCF Control Package (XCP) to provide remote monitoring and management capabilities. This service processor regularly monitors environmental sensors, provides advanced warning of potential error conditions, and executes proactive system maintenance procedures as necessary. Indeed, while power is supplied to the server, the XSCF constantly monitors the platform even if the system is inactive. XCP enables Dynamic Domains (= partitioning feature) configuration, audit administration, hardware control capabilities, hardware status monitoring, reporting, and handling, automatic diagnosis and domain recovery, capacity on demand operations, and XSCF failover services. Additional technical details about the XSCF and XCP are found in *Chapter 7 – System Management*.

#### 2.1.7 Power and Cooling

Fujitsu SPARC Enterprise servers use separate modules for power and cooling. Sensors placed throughout the system measure temperatures on processors and key ASICS as well as the ambient temperature at several location. Hardware redundancy in the power and cooling subsystems combined with environmental monitoring keep servers operating even under power or fan fault conditions.

#### 2.1.7.1 Fan Unit

Fujitsu SPARC Enterprise server family members use fully redundant, hot-swap fans as the primary cooling system (Table 2-2 and Table 2-3). If a single fans fails, the XSCF detects the failure and switches the remaining fans to high-speed operation to compensate for the reduced airflow. Fujitsu SPARC Enterprise servers operate normally under these conditions, enabling ample time to service the failed unit. Replacement of fans units can occur without interrupting application processing.

#### 2.1.7.2 Power Supply

The use of redundant power supplies and power cords adds to the fault resilience of Fujitsu SPARC Enterprise servers (Table 2-2 and Table 2-3). Power is supplied to Fujitsu SPARC Enterprise servers by redundant hot-swap power supplies, enabling continued server operation even if a power supply fails. Since the power units are hot-swappable, removal and replacement can occur while the system continues to operate.

As an option, Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 can be ordered with a three-phase power supply unit and corresponding server cabinet. Models with a three-phase power supply permit two configurations, a star connection that connects a neutral line and each phase, and a delta connection that connects each phase.

Table 2-2. Fujitsu SPARC Enterprise midrange servers power and cooling specifications.

|                | Fujitsu SPARC Enterprise<br>M4000                                                                                          | Fujitsu SPARC Enterprise<br>M5000                                                                                                                            |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Fan Units      | <ul> <li>Four fan units</li> <li>Two 172 mm fans</li> <li>Two 60 mm fans</li> <li>One of each type is redundant</li> </ul> | <ul> <li>Four fan units</li> <li>Four 172 mm fans</li> <li>Two fan groups, each containing two fan units</li> <li>One redundant fan per fan group</li> </ul> |  |  |

| Power Supplies | <ul> <li>1656 W (max)</li> <li>Two units</li> <li>1+1 redundant</li> <li>Single-phase</li> </ul>                           | <ul><li>3198 W (max)</li><li>Four units</li><li>2+2 redundant</li><li>Single-phase</li></ul>                                                                 |  |  |

| Power Cords    | <ul><li>Two power cables</li><li>1+1 redundant power cables</li></ul>                                                      | <ul><li>Four power cables</li><li>2+2 redundant power cables</li></ul>                                                                                       |  |  |

Table 2-3. Fujitsu SPARC Enterprise high-end servers power and cooling specifications.

|                | Fujitsu SPARC<br>Enterprise M8000                                                                                          | Fujitsu SPARC<br>Enterprise M9000<br>(32 CPU configuration)                 | Fujitsu SPARC<br>Enterprise M9000<br>(64 CPU configuration)                 |

|----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Fan Units      | <ul><li>12 fan units</li><li>Four 172 mm fans</li><li>Eight 60 mm fans</li><li>N+1 redundant</li></ul>                     | <ul><li>16 fan units</li><li>16 172 mm fans</li><li>N+1 redundant</li></ul> | <ul><li>32 fan units</li><li>32 172 mm fans</li><li>N+1 redundant</li></ul> |

| Power Supplies | • 10.49 kW (max)<br>• 9 units<br>• N+1 redundant                                                                           | <ul><li>19.87 kW (max)</li><li>15 units</li><li>N+1 redundant</li></ul>     | <ul><li>39.72 kW (max)</li><li>30 units</li><li>N+1 redundant</li></ul>     |

| Options        | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>                                                       | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>        | <ul><li>Single-phase</li><li>Three-phase</li><li>Dual-grid</li></ul>        |

| Power Cords    | <ul> <li>3 power cables (single feed)</li> <li>6 power cables (dual feed)</li> <li>2 power cables (three phase)</li> </ul> | feed) • 10 power cables (dual feed)                                         | (single feed) • 20 power cables (dual feed)                                 |

#### 2.1.7.3 Optional Dual Power Feed

While enterprises can control most factors within the datacenter, utility outages are often unexpected. The consequences of loss of electrical power can be devastating to IT operations. In order to enable organizations to reduce the impact of such incidents, midrange and high-end models of Fujitsu SPARC Enterprise servers are dual power feed capable. The AC power subsystem in these servers is completely duplicated, enabling optional reception of power from two external, independent AC power sources. The use of a dual power feed and redundant power supplies increases system availability, as server operations can remain unaffected even after a single power grid failure.

#### 2.1.8 Operator Panel

Mid-range and high-end models of Fujitsu SPARC Enterprise servers feature an operator panel to display server status, store server identification and user setting information, change between operational and maintenance modes, and turn on power supplies for all domains. During server startup, the front panel LED status indicators verify XSCF and server operation.

Figure 2-4. The Fujitsu SPARC Enterprise server operator panel.

## 2.2 Midrange Systems — Fujitsu SPARC Enterprise M4000 and Fujitsu SPARC Enterprise M5000

Fujitsu SPARC Enterprise M4000 and Fujitsu SPARC Enterprise M5000 are economical, high-power compute platforms with enterprise-class features. These midrange servers are designed to reliably carry datacenter workloads that support core business operations.

#### 2.2.1 Fujitsu SPARC Enterprise M4000

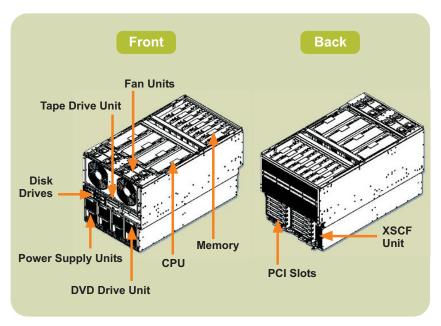

The Fujitsu SPARC Enterprise M4000 enclosure measures six rack-units (RU) and supports up to four processor chips, 128 GB of memory, and up to two Dynamic Domains. As a processor chip, either SPARC64 VI or SPARC64 VII can be mounted, or both can be mounted together. In addition, the Fujitsu SPARC Enterprise M4000 features four short internal PCIe slots and one short internal PCI-X slot, as well as two disk drives, one DVD drive, and an optional DAT tape drive. Two power supplies and four fan units power and cool the Fujitsu SPARC Enterprise M4000.

Figure 2-5. Fujitsu SPARC Enterprise M4000 enclosure diagram.

#### 2.2.2 Fujitsu SPARC Enterprise M5000

The Fujitsu SPARC Enterprise M5000 enclosure measures 10 RU and supports up to eight processor chips, 256 GB of memory, and up to four Dynamic Domains. As a processor chip, either SPARC64 VI or SPARC64 VII can be mounted, or both can be mounted together. In addition, the Fujitsu SPARC Enterprise M5000 features eight short internal PCIe and two short internal PCI-X slots, as well as four disk drives, one DVD drive, and an optional DAT tape drive. Four power supplies and four fan units power and cool the Fujitsu SPARC Enterprise M5000.

Figure 2-6. Fujitsu SPARC Enterprise M5000 enclosure diagram.

## 2.3 High-End Systems — Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000

Designed to deliver outstanding performance for even the most challenging workloads, high-end Fujitsu SPARC Enterprise servers merge mainframe reliability, advanced performance technology often used in supercomputers, and an open systems environment to create reliable, high-throughput, flexible systems.

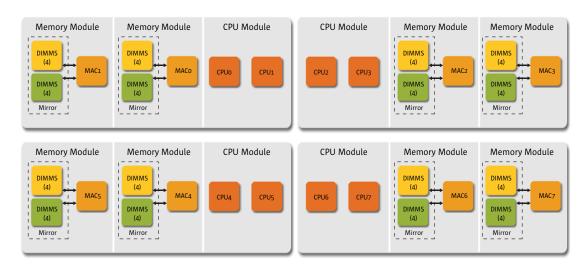

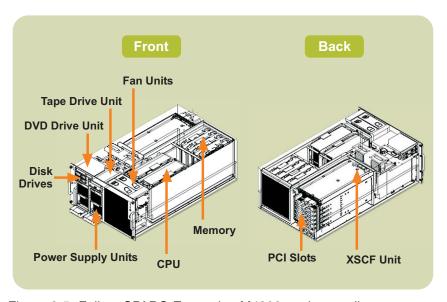

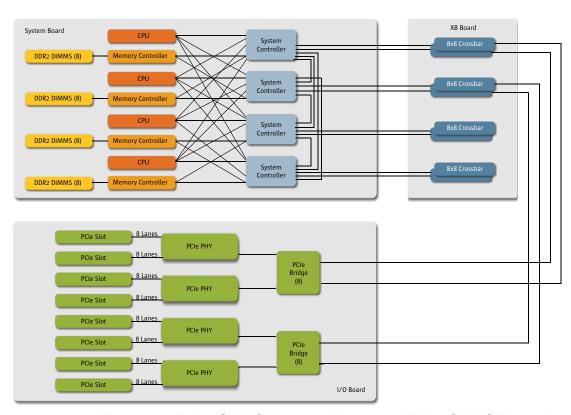

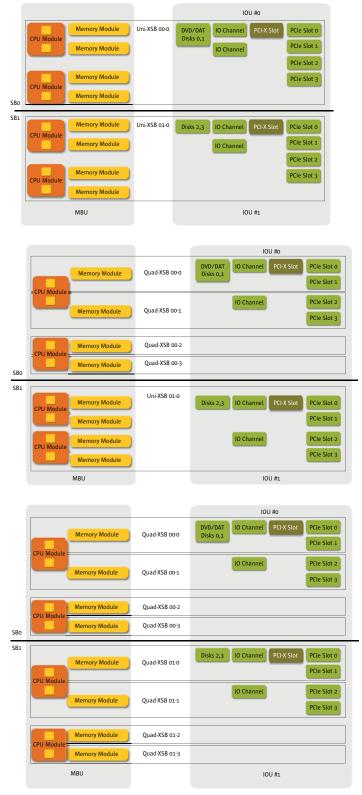

#### 2.3.1 Fujitsu SPARC Enterprise M8000

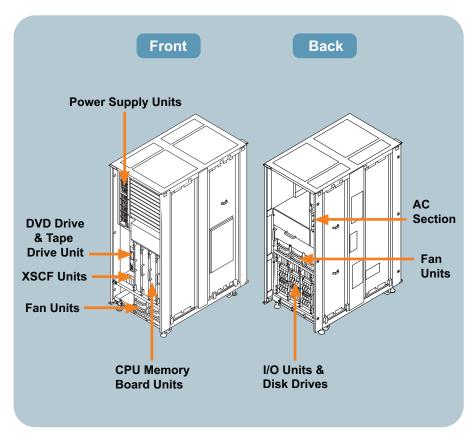

The Fujitsu SPARC Enterprise M8000 is mounted in an enterprise system cabinet and supports up to four CPU Memory Units (CMU) and four I/O Units (IOU). Fully configured, the Fujitsu SPARC Enterprise M8000 houses 16 processor chips, 512 GB of memory, 32 short internal PCIe slots, and can be divided into 16 Dynamic Domains. As a processor chip, either SPARC64 VI or SPARC64 VII can be mounted, or both can be mounted together. In addition, the Fujitsu SPARC Enterprise M8000 supports up to 16 disk drives, one DVD drive, and an optional DAT tape drive. Nine power supplies and 12 fan units power and cool the Fujitsu SPARC Enterprise M8000.

Figure 2-7. Fujitsu SPARC Enterprise M8000 enclosure diagram.

#### 2.3.2 Fujitsu SPARC Enterprise M9000 (32 CPU configuration)

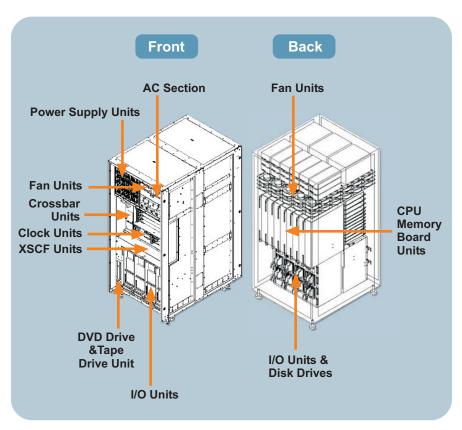

The Fujitsu SPARC Enterprise M9000 (32 CPU configuration) mounts in an enterprise system cabinet and supports up to eight CMUs and eight IOUs. Fully configured, it houses 32 processor chips, 2 TB of memory, 64 short internal PCIe slots, and can be divided into 24 Dynamic Domains. As a processor chip, either SPARC64 VI or SPARC64 VII can be mounted, or both can be mounted together. In addition, it supports up to 32 disk drives, one DVD drive, and an optional DAT tape drive. Power and cooling is provided by 15 power supplies and 16 fan units.

Figure 2-8. Fujitsu SPARC Enterprise M9000 (32 CPU configuration) enclosure diagram.

#### 2.3.3 Fujitsu SPARC Enterprise M9000 (64 CPU configuration)

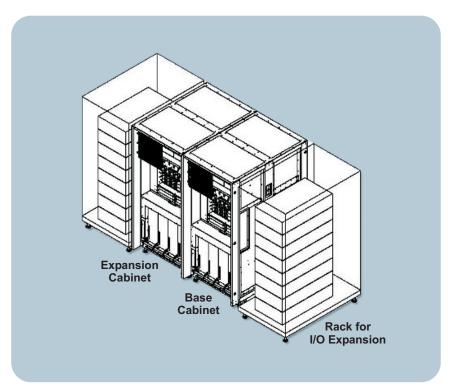

An expansion cabinet can be added to an existing base cabinet to create the Fujitsu SPARC Enterprise M9000 (64 CPU configuration) which supports up to 16 CMUs and 16 IOUs. Fully configured, it houses 64 processor chips, 4 TB of memory, 128 short internal PCIe slots, and can be divided into 24 Dynamic Domains. As a processor chip, either SPARC64 VI or SPARC64 VII can be mounted, or both can be mounted together. In addition, it supports up to 64 disk drives, two DVD drives, and two optional DAT tape drives. The Fujitsu SPARC Enterprise M9000 (64 CPU configuration) utilizes 30 power supplies and 32 fan units for power and cooling.

Figure 2-9. Fujitsu SPARC Enterprise M9000 (64 CPU configuration) enclosure diagram.

## System Bus Architecture — Jupiter Interconnect

High end systems containing dozens of CPUs only provide scalability if all processors actually contribute to the performance of the application. The ability to deliver near-linear scalability and fast, predictable performance for a broad set of applications rests largely on the capabilities of the system bus. Fujitsu SPARC Enterprise servers utilize a system interconnect designed to deliver massive bandwidth and consistent, low latency between components. The Jupiter system bus benefits IT operations by delivering balanced and predictable performance to application workloads.

#### 3.1 Fujitsu SPARC Enterprise Server Interconnect Architecture

The Jupiter interconnect design maximizes the overall performance of Fujitsu SPARC Enterprise servers. Implemented as point-to-point connections which utilize packet-switched technology, this system bus provides fast response times by transmitting multiple data streams. Packet-switching enables the interconnect to operate at much higher system-wide throughput by eliminating "dead" cycles on the bus. All routes are uni-directional, non-contentious paths with multiplexed address, data, and control plus ECC in each direction.

System controllers within the interconnect architecture on all Fujitsu SPARC Enterprise servers direct traffic between local CPUs, memory, I/O subsystems, and interconnect paths. On high-end systems, the system bus is implemented as a crossbar switch between system boards to support high-throughput data transfer with consistent latency times between all components. In addition, the physical addressing of memory on a motherboard of a Fujitsu SPARC Enterprise midrange server or CMU of a Fujitsu SPARC Enterprise high-end server is evenly spread out across all system controllers on that same board, improving performance.

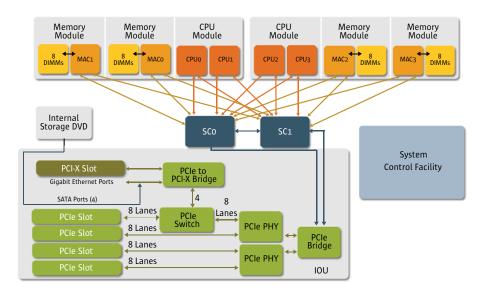

# 3.1.1.1 Fujitsu SPARC Enterprise M4000 System Interconnect Architecture The Fujitsu SPARC Enterprise M4000 system is implemented within a single motherboard. This server design features one logical system board with two system controllers. Both system controllers connect to each other, as well as CPU modules,

memory address controllers, and the IOU (Figure 3-1).

Figure 3-1. Fujitsu SPARC Enterprise M4000 system interconnect diagram.

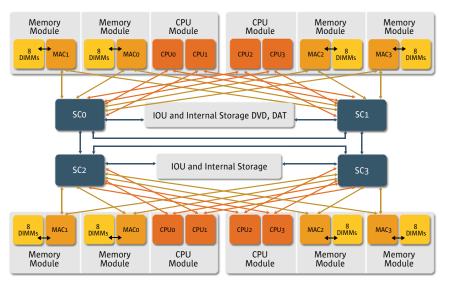

#### 3.1.1.2 Fujitsu SPARC Enterprise M5000 System Interconnect Architecture

The Fujitsu SPARC Enterprise M5000 system is implemented within a single motherboard but features two logical system boards. Similar to the Fujitsu SPARC Enterprise M4000 design, each logical system board contains two system controllers which connect to each other, as well as CPU modules, memory access controllers, and an IOU. In addition, each system controller connects to a corresponding system controller on the other logical system board (Figure 3-2).

Figure 3-2. Fujitsu SPARC Enterprise M5000 system interconnect diagram.

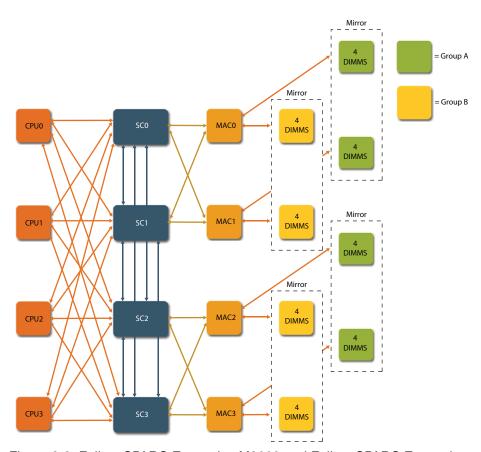

## 3.1.1.3 Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 System Interconnect Architecture

Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 feature multiple system boards which connect to a common crossbar. Each system board contains four system controllers. Each system controller connects to every CPU module. For improved bandwidth, every memory access controller connects to two system controllers, and each system controller connects to every other system controller within the system board. The system controllers also provide a connection to each crossbar unit, enabling data transfer to other system boards (Figure 3-3).

Figure 3-3. Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 system interconnect diagram.

#### 3.2 System Interconnect Reliability Features

Built-in redundancy and reliability features of Fujitsu SPARC Enterprise server system interconnects enhance the stability of these servers. The Jupiter interconnect protects against loss or corruption of data with full ECC protection on all system buses and in memory. When a single-bit data error is detected in a CPU, Memory Access Controller, or I/O Controller, hardware corrects the data and performs the transfer. Fujitsu SPARC Enterprise M8000 and Fujitsu SPARC Enterprise M9000 feature degradable crossbar switches and degradable bus routes. In the rare event of a hardware failure within the interconnect, the system uses the surviving bus route on restart, isolating the faulty crossbar and enabling operations to resume.

#### 3.3 Scalable Performance

The high bandwidth and overall design of the Jupiter system interconnect contributes to the scalable performance of Fujitsu SPARC Enterprise servers. Theoretical peak system throughput, snoop bandwidth, and I/O Bandwidth numbers, as well as Stream benchmark results for all Fujitsu SPARC Enterprise servers are found in Table 3-1.

In Fujitsu SPARC Enterprise servers, the CPUs, memory address controllers, and IOUs are directly connected by a high-speed broadband switch for data transfer, enabling a relatively even latency to be maintained between individual components. As components are added, processing capability and latency are not degraded. In fact, the crossbar interconnect implementation in Fujitsu SPARC Enterprise high-end servers results in increased interconnect bandwidth every time a system board is added to the server.

Table 3-1. Theoretical system bandwidth and theoretical I/O bandwidth at peak time, snoop bandwidth, and stream benchmark results for SPARC Enterprise.

|                                                        | Theoretical<br>system<br>bandwidth at<br>peak time <sup>a</sup><br>(GB/s) | Snoop<br>bandwidth<br>(GB/s) | Triad results<br>of stream<br>benchmark<br>(GB/s) | Copy results<br>of stream<br>benchmark<br>(GB/s) | Theoretical I/O bandwidth at peak time <sup>b</sup> (GB/s) |

|--------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|---------------------------------------------------|--------------------------------------------------|------------------------------------------------------------|

| SPARC Enterprise M4000                                 | 32                                                                        | 129                          | 12.7                                              | 12.6                                             | 8                                                          |

| SPARC Enterprise M5000                                 | 64                                                                        | 129                          | 25.3                                              | 24.8                                             | 16                                                         |

| SPARC Enterprise M8000                                 | 184                                                                       | 245                          | 69.6                                              | 60.3                                             | 61                                                         |

| SPARC Enterprise<br>M9000<br>(32-CPU<br>configuration) | 368                                                                       | 245                          | 134.4                                             | 114.9                                            | 122                                                        |

| SPARC Enterprise<br>M9000<br>(64-CPU<br>configuration) | 737                                                                       | 245                          | 227.1                                             | 224.4                                            | 244                                                        |

a. The theoretical system bandwidth at peak time is calculated by multiplying the bus width by the bus frequency between the system controller and memory access controller.

b.The logical I/O bandwidth at peak time is calculated by multiplying the bus width by the bus frequency between the system controller and PCI bridge.

# 4. Fujitsu SPARC64 VI/SPARC64 VII Processors

#### 4.1 SPARC64 Series

The SPARC64 Series is a SPARC processor developed by Fujitsu for UNIX servers. High reliability technology of the mainframe class and a frequency exceeding 1 GHz have been realized with the SPARC64 V. This processor has been used for Fujitsu PRIMEPOWER servers. The SPARC64 VI has realized high throughput by using the SPARC64 V as a base and by incorporating a two-core x two thread architecture. The throughput of the latest SPARC 64 VII has been improved further by incorporating four-core architecture and by modifying the multi-threading mechanism. These SPARC64 VI and SPARC64 VII processors are used with SPARC Enterprise servers.

#### 4.2 SPARC64 VI Overview

The SPARC64 VI is a SPARC64 series processor developed by Fujitsu using its 90-nm technology. This processor has an operating frequency of 2.4 GHz, and a chip size of 20.4 x 10.7 mm. The chip, which has two built-in cores and a shared 6-MB L2 cache, has a maximum operating power consumption of 120 W.

The SPARC64 VI design not only retains the high performance and high reliability of the SPARC64 V, but also features throughput improved considerably with the use of two CPU cores packed in one chip and Vertical Multi Threading, which is being adopted for the first time in the SPARC64 series. Furthermore, the new system bus called Jupiter bus has been designed to maximize the performance of SPARC64 VI and SPARC64 VII.

#### 4.3 SPARC64 VII Overview

The SPARC64 VII is the latest processor developed by Fujitsu for the SPARC64 Series. It uses the 65-nm technology of Fujitsu and it has realizes an operating frequency of 2.88 GHz. The chip measures 21.3 mm by 20.9 mm. The chip has four built-in cores with a shared 6 MB L2 cache configuration. The operating power consumption is 140 W.

Fujitsu designed the SPARC64 VII for increased throughput while maintaining the high performance and high reliability that have been realized with the existing SPARC64 VI. For increased throughput, the number of built-in cores has been increased from two to four, and the multi-threading mechanism to be used has been changed from VMT to SMT. The L2 cache is configured to be shared by the four cores, and the throughput has been doubled so that data can be supplied to the four cores. Also, especially with the field of high performance computing (HPC) in mind, an inter-core high-speed synchronization mechanism called hardware barrier has been implemented.

At the same time, by using a bus protocol that is the same as that of the existing SPARC64 VI, each CPU module can be upgraded from SPARC64 VI to SPARC64 VII.

#### 4.4 SPARC64 VII micro-architecture

This section provides an overview of the micro-architecture of the SPARC64 VII. While the basic structure of the core pipeline of SPARC64 VII is the same as that of the SPARC64 VI, it uses simultaneous multi-threading (SMT) instead of vertical multi-threading (VMT) to implement multi-threading. As shown in Figure 4-1, two threads can be executed simultaneously on each of the four cores.

Figure 4-1. Multi-threading of the SPARC64 VII

In SMT design, Fujitsu focused on eliminating interference between threads as much as possible. The chip is configured so that, as a rule, the hardware resources for one thread are isolated from those of the other when both threads are running. In contrast, when either thread is in the idle state, the other thread can use resources of both threads except for some resources. Thus, the chip has been designed to provide increased performance of single-thread operation.

In the structure, both threads share the pipeline core. However, it is controlled so that, even if a pipeline is stalled in one thread, the processing in the other thread is not clogged up. In the instruction fetch stage, instruction decoding stage, or commit stage, either thread is selected in each cycle.

#### 4.4.1 Details of the Micro-architecture

Details of the micro-architecture are outlined below.

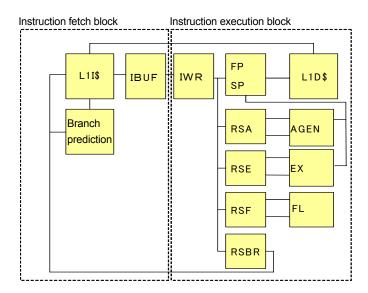

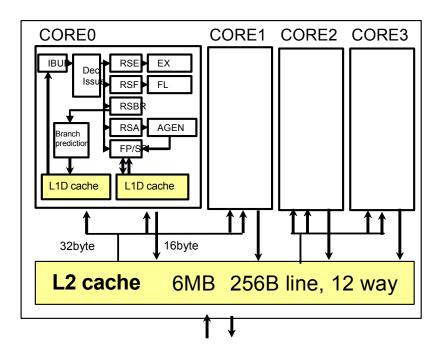

As shown in Figure 4-2, a core of the SPARC64 VII is divided into the instruction fetch block and instruction execution block. The instruction fetch block includes the primary cache dedicated for instructions (L1I cache), and the instruction execution block includes the primary cache dedicated for operands (L1D cache).

Figure 4-2. Functional diagram of the SPARC64 VII core

#### 4.4.2 Instruction Fetch block

The instruction fetch block, which operates independently of the instruction execution block, takes a series of instructions into the instruction buffer (IBUF), which are expected to be executed according to branch prediction. The IBUF has a capacity of 256 bytes, and can store up to 64 instructions. When both threads are running, the IBUF is divided evenly for each thread.

When the instruction execution is stalled, instruction fetch continues until the IBUF becomes full. In contrast, when instruction fetch pauses for some reason such as a cache error, instructions can be taken from the IBUF and execution can continue as long as the IBUF includes instructions. Instruction fetch can be started in every cycle, and 32 bytes, which comprise eight instructions, are fetched at one time. The throughput of instruction execution is up to four instructions per cycle, while twice the throughput of instruction execution is assured for instruction fetch. The IBUF conceals the latency of the large-capacity primary instruction cache by separating instruction fetch and instruction execution from each other (decoupling).

#### 4.4.3 Instruction Execution Block

#### 4.4.3.1 Instruction decode and issue

In the Instruction decode and instruction issue stages, the four instructions in the IWR are decoded simultaneously, and resources required for execution (various reservation stations, fetch port and store port, and register update buffer) are determined. Then, whether there are free resources for them is checked. If there are free resources, they are allocated and given instruction identifications (IID) ranging from 0 to 63. Then, the instruction is issued. In other words, the maximum number of in-flight instructions is 64. Meanwhile, when both threads are running, the maximum number of instructions for each thread is 32. In each cycle, an instruction of either thread is decoded and threads are alternately switched.

When an instruction is issued, the IWR is released. For the instruction in any slot of the IWR, there are no restrictions on the allocation of resources such as reservation stations. Also, there are no restrictions on instruction type combinations. Therefore, as long as there are free resources, instructions can be issued. Even if there is no sufficient space for four instructions, as many instructions as possible are issued in program order. As described above, by eliminating stall conditions of instruction issue as much as possible, a high multiplicity level is assured for any binary code.

#### 4.4.3.2 Instruction execution

A decoded instruction is registered in a reservation station. The SPARC64 VII has reservation stations for integer operation (reservation stations for execution: RSE) and reservation stations for floating point operation (reservation stations for floating point: RSF). The RSEs and RSFs are divided into two queues for the execution unit. In other words, four reservation stations for operation are provided. They are RSEA, RSEB, RSFA, and RSFB. Each instruction stored in a reservation station is dispatched to the execution unit that corresponds to the reservation station in the order in which source operands are prepared for instructions. Therefore, four operations can be dispatched simultaneously. Basically, the oldest instruction that can be dispatched (oldest ready) is selected from the instructions in a reservation station. However, in cases where a register to be updated by a load instruction is used as a source operand for an operation, the instruction is speculatively dispatched before the result of the load instruction is obtained. Then, in the execution stage, whether the speculative dispatch has been successful is determined. This is called speculative dispatch. Use of speculative dispatch conceals the latency of the pipeline for cache access, increasing the use efficiency of the execution unit.

In addition to the above described RSEs and RSFs, there are other reservation stations, which are reservation stations for branch instructions (reservation station for branch: RSBR) and reservation stations for calculating addresses for load/store instructions (reservation station for address generation: RSA).

#### 4.4.3.3 Instruction commit

All results of instructions that are executed out of order are once stored in the GUB and FUB work registers, which not visible to software. To assure the instruction order in a program, registers such as GPR and FPR and memory are updated in program order in the commit stage. In addition, control registers such as the PC are also updated at the same time in the commit stage. As described above, precise interrupt is guaranteed, and processing in execution can always be canceled. The method above is called a synchronous update method, which does not only make it easier to re-execute instructions due to a branch prediction error, but also contributes to increased RAS as explained in a later chapter. The maximum number of instructions that can be committed at one time is four. The instruction commit stage is shared by the two threads, and either thread is selected in each cycle to perform commit processing.

## 4.5 Cache System

The cache memory of the SPARC64 VII has a two-layer structure, consisting of a middle-capacity primary cache (L1 cache) and a high-capacity secondary cache (L2 cache).

Figure 4-3. SPARC64 VII core and cache

The L1 cache consists of a cache dedicated for instructions (L1I cache) and a cache dedicated for operands (L1D cache). Each of these caches has the capacity of 64 kilobytes, uses the two-way set associative method, and has the block size of 64 bytes. The L1D cache is divided into eight banks on the four-byte address boundaries, and two operands can be accessed at one time. The L1 cache uses virtual addresses for cache indexes and physical addresses for cache tags (virtually indexed physically tagged: VIPT). In the VIPT method, consistency may be lost if the same area of memory is accessed using different virtual addresses because different indexes are used for registration (synonym problem). Through coordination with the L2 cache, the SPARC64 VII resolves the synonym problem with hardware.

The L2 cache has a maximum capacity of 6 megabytes, uses a 12-way set associative method, has a block size of 256 bytes, and is shared by the four cores. By adopting two-bank interleaved structure, 64 bytes of data can be read in each cycle. The bus for sending data that is read from the L2 cache to the L1 cache has a width of 32 bytes per two cores, and the bus for sending data from the L1 cache to L2 cache has a width of 16 bytes per one core.

The cache update policies of L1 cache and L2 cache are both write-back. That is, the store data is written into only one cache hierarchy. In the write-back method, cache-

missed lines are always loaded on to the cache memory, so that the store operations can complete with updating one cache hierarchy. In the write-back method, it is necessary to bring old data on the memory onto the cache, even if the data is stored, when a cache error occurs, but store operation is completed only on the cache when a cache hit occurs. In general, because the frequency of the store operation is quite high, the write-back method has an advantage because it can reduce intercache traffic and memory access traffic.

Meanwhile, because the write-back method keeps the latest data in the cache, if an error occurs in the relevant processor, there is a risk that the error may affect not only the internal operation of the processor, but also the entire system. The SPARC64 VII has powerful RAS functions to cope with this problem.

Also, a new hardware barrier mechanism has been implemented in the SPARC64 VII. The hardware barrier mechanism synchronizes the cores in a CPU chip with each other, and faster synchronization processing can be implemented compared with a conventional synchronization process realized by software. This mechanism is especially useful in the HPC area.

## 4.6 Reliability, Availability, and Serviceability (RAS) Functions

In the SPARC64 VII, RAS functions comparable to mainframe computers have been implemented. With these RAS functions, errors are reliably detected, their effect is kept within a limited range, recovery processing is tried, error logs are recorded, software is notified, and so forth. In other words, the basics of RAS functions are thoroughly implemented. Through the implementation of the RAS functions, the SPARC64 VII provides high reliability, high availability, high serviceability, and high data integrity as a processor for mission-critical UNIX servers.

#### 4.6.1 RAS of Internal RAMs

Among the parts of a processor, the error occurrence frequency is highest in RAM. In the SPARC64 VII, because any one-bit error in RAM can automatically be corrected by hardware without intervention by software, it does not affect software.

| Туре                 |      | Error detection<br>method<br>Protection method | Error correction method                 |

|----------------------|------|------------------------------------------------|-----------------------------------------|

| L1 instruction cache | Data | Parity                                         | Invalidation and reread                 |

|                      | Tag  | Parity + duplication                           | Rewrite of duplicated data              |

| L1 data cache        | Data | SECDED ECC                                     | One-bit error correction using ECC      |

|                      | Tag  | Parity + duplication                           | Rewrite of duplicated data              |

| L2 cache             | Data | SECDED ECC                                     | One-bit error correction using ECC      |

|                      | Tag  | SECDED ECC                                     | One-bit error correction using ECC      |

| Instruction TLB      |      | Parity                                         | Invalidation                            |

| Data TLB             |      | Parity                                         | Invalidation                            |

| Branch history       |      | Parity                                         | Recovery from branch prediction failure |

SECDED: Single Error Correction Double Error Detection

For the L1 cache, L2 cache, and TLB, degradation can be performed separately in way units. Error occurrence counts are counted for each function unit. When an error occurrence count per unit time exceeds the upper limit, degradation is performed and the relevant way is not used subsequently. Hardware performs degradation automatically. At the same time, it also performs the required operation to assure the continuity of coherency automatically. More specifically, hardware automatically performs the following: 1) operation that writes back to the L2 cache all the dirty lines in the way of the L1D cache to be degraded, and 2) operation that writes back to the memory the dirty lines in the way of the L2 cache to be degraded. The degradation of a way is performed without adversely affecting software, and software operation is free from any effects except for a slowdown of processing speed.

#### 4.6.2 RAS of Internal Registers and Execution Units

The SPARC64 VII also provides error protection for registers and execution units, making assurance doubly sure for data integrity.

| Type           |                                                                  | Error detection method<br>Protection method |

|----------------|------------------------------------------------------------------|---------------------------------------------|

| Register       | Integer register                                                 | SECDED ECC                                  |

|                | Floating-point register                                          | Parity                                      |

|                | PC, PSTATE, etc.                                                 | Parity                                      |

|                | Computation input-output register                                | Parity                                      |

| Execution unit | Addition and subtraction, division, shift, and graphic operation | Parity prediction                           |

|                | Multiplication                                                   | Parity prediction + residue check           |

For integer architecture registers, ECC is used from the SPARC64 VII to increase reliability. When an error occurs, the ECC circuit corrects the error. Parity bits have been added to the floating point architecture registers and other registers. Also, the parity prediction circuit, residue check circuit, and other circuits have been added to an execution unit to propagate parity information to output results. In the unlikely event that a parity error is detected, hardware automatically re-executes the instruction to attempt recovery as described below. This function is called instruction retry.

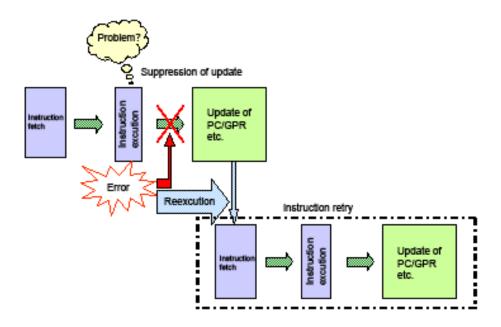

#### 4.6.3 Synchronous Update Method and Instruction Retry

As shown in the explanation of the instruction execution block, the SPARC64 VII uses the synchronous update method. When an error is detected, all the instructions being executed at this time is canceled. Intermediate results before commitment can be discarded, and only results updated by instructions that have been completed without encountering any errors remain in programmable resources. Therefore, not only can the destruction of programmable resources due to errors be prevented, hardware can also perform an instruction retry after error detection. Even in case of a hang-up, because stalled instructions can be discarded once and then retried from the beginning, there is a possibility of recovery.

Instruction retry is triggered by an error and is automatically started. A retry is performed instruction by instruction to increase the chance of normal execution. When the execution is completed normally, the state automatically returns to the normal execution state. During this period, no software intervention is required, and if the instruction retry succeeds, the error does not affect software. An instruction retry is repeated until the number of retry times reaches the threshold, and when the threshold is exceeded, the occurrence of the error is reported to software by an interrupt.

#### 4.6.4 Increased Serviceability

The SPARC64 VII has error checking mechanisms in a variety of locations. When an error occurs, the system is notified of the error through a dedicated interface. On receipt of this notification, the system control facility (SCF) firmware collects error logs through the dedicated interface and analyzes them. This series of operations does not affect software and is performed in the background.