本技术介绍参考了以下链接

English

2014年9月22日

世界最快!面向CPU之间通信的56Gbps接收机电路技术

数据通信速度翻倍,为下一代服务器和超级计算机的高性能化做出贡献

株式会社富士通研究所(注1)(以下简称,富士通研究所)开发了以下技术。

开发背景

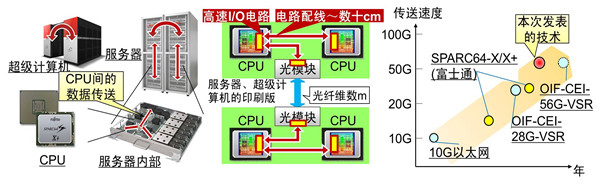

近年来,面向支撑云计算的数据中心等,对服务器的数据处理能力提出了更高的要求。因此,不仅CPU的性能得到了提升,连接了多个CPU的大规模系统也得到了构建,搭载了CPU的机箱内和机箱间的数据交换也在急剧增加。为了应对这一情况,在现在的服务器上,数据通信速度从几个Gbps提升至十几个Gbps。但是,预期数据处理量将继续高速增加,因此,面向下一代高性能服务器,相当于当前水平2倍的56Gbps高速通信受到了高度期待。另外,用于机箱间光通信等的光模块的通信速度,在OIF(注2)中也在推进56Gbps的标准化。

图1 服务器内部CPU间以及机箱间的高速数据通信

课题

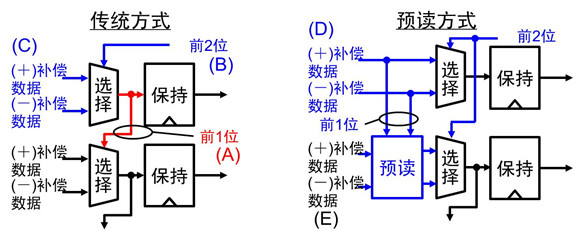

在接收机电路的高速化中,有效的方法是提升对退化的输入信号波形进行补偿的电路DFE(注3)的处理能力(图2)。

DFE的基本的思路是,按前一位的位值补偿输入信号,强调输入信号的变化,但是实际的电路设计中会预先准备2个已经补偿了的候补,按照比特值不同进行选择。所谓补偿,例如,前一位是0时,对输入信号进行正方向的补偿(加法),以此来强调从0到1的变化。前一位是1时,对输入信号进行反方向的补偿(减法),以此来强调从1到0的变化。0持续的时候,通过正方向的补偿可以提升信号的电平,只要不超过判断电路的1/0判断水平就不会造成问题。

通常的56Gbps电路设计是将16个DFE连接起来使用,比如是4个就按照1/4周期运作。因此,如果是28Gbps,1/4周期就是142皮秒,在142皮秒内完成全部4个位的补偿。但是,56Gbps的1/4周期是71皮秒,只能完成2个位的补偿,出现定时误差(timing error)(图3)。

图2 高速化的主要技术:信号退化补偿电路(DFE)及其作用

图3 传统DFE的实际构成和56Gbps运行时的课题

开发的技术

从前1位的选择结果中获取两个候补预先进行计算,如果确定了前2位的位值,前1位的位值和现在的位值就同时确定了,因此我们将预读方式重新设计为并行处理,这样就可以缩短运算时间,从而成功开发出了以56Gbps运作的接收机电路(图4)。

开发的技术特点如下所述:

1. 通过预读方式进行补偿

在传统方式中,前1位的选择电路结果(A)是通过前2位的选择电路结果(B)和前1位的选择电路的输入信号(+/-补偿数据)(C)的组合电路来实现的。在预读方式中,前1位的选择电路的输入信号(+/-补偿数据)(D)和现在的选择电路的输入信号(+/-补偿数据)(E)预先在预读电路中组合,重新计算出选择电路的候补。这样一来,无需使用前1位的选择电路结果,仅通过前2位的选择电路的结果就能实现和传统方式同样的功能。

图4 预读方式的原理

2. 通过保持电路实现预读处理的并行化

每隔1个位的多个DFE预读电路可以独立运作(图5)。在选择电路和预读电路之间插入保持电路,使各个保持电路的输入输出同步,就可以实现并行处理。

由于预读电路的运算时间基本上和选择器的选择时间相同,所以整体的运算时间依赖于前2位的数据所决定的选择器的数量,如果是4位构成则为2。由此,可以在56Gbps的1/4周期71皮秒内完成运算。这样就能够以56Gbps,传统的2倍通信速度进行数据接收。

图5 新体系结构的DFE及其效果

效果

通过本技术,在下一代服务器和超级计算机中即使CPU的性能翻倍,不增加引脚(pin)数目也能够实现CPU间通信的宽带化,将为连接多个CPU的大规模系统的性能提高做出贡献。此外,它符合光模块通信的OIF标准,与光模组通信OIF-CEI-28G构建的400Gbps以太网相比,能够减少一半并行运行的电路数(道数),因此通过光模块的小型化,将允许系统在较低功耗水平下,以更高性能运行。

今后

富士通研究所开发的技术适用于CPU和光模块的界面部分,旨在2016年实现实用化。并且,富士通研究所将继续研究适用于下一代的服务器和超级计算机等的产品。

注释

注1 株式会社富士通研究所

社长 佐相秀幸

总公司所在地 日本神奈川县川崎市

注2 OIF:

Optical Internetworking Forum(光互联网络论坛)的缩写。

注3 DFE:

Decision Feedback Equalizer(判决反馈均衡器)的缩写。